內存技术中高纵深比工艺控制的深入研究

数据是我们生活中不可或缺的一部分。过去我们必须定期删除文件以释放存储空间,现在则相反,假设我们的数据永远不需要被删除。为什么冒险错删文件呢?保存它们!这种新方法将耗费大量内存,提高了对存储空间的需求。内存部分的两个主力是NAND 快闪内存和DRAM。DRAM是动态、易失和快速的,非常适合用作短期系统内存。相反,NAND 快闪内存是非易失的,这意味着它具有良好的保留性,可很好地用于长期低成本存储。随着需求的不断增加,这两种内存类型的主要目标都是更快的速度,更高的密度和更低的存储单元成本1。

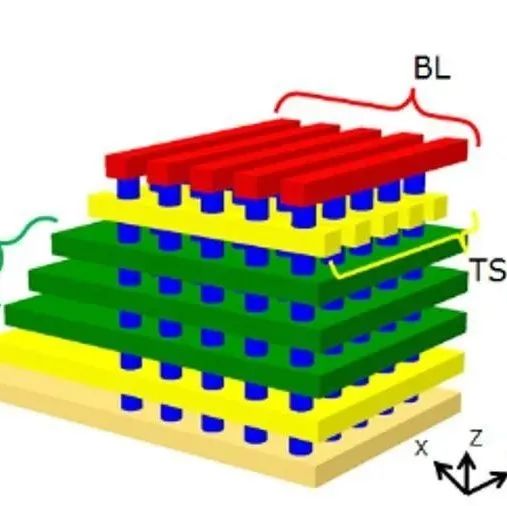

为了更好的实现NAND和DRAM的性能,所采用的开发途径略有不同。DRAM的开发途径与逻辑产品类似,采用持续微缩的单元设计。这种单元尺寸的微缩推动了多重图案化技术的引入,并最终在批量制造中需要采用EUV光刻技术。平面 NAND也曾面临微缩的限制,并最终采取垂直方向上的转变。这种垂直集成放宽了对3D NAND器件的光刻要求,却将最复杂的工艺挑战迁移到沉积和蚀刻2。其主要的结构由交替薄膜沉积,然后对整个堆叠进行高纵深比(HAR)蚀刻。3D NAND中的每个新节点的工艺都采用更高的垂直堆叠。高纵深比结构具有独特的工艺控制要求,因为沟槽的深度是微米级,而精度要求达到埃级3。如图1所示,这类HAR结构的示例如3D NAND中的通道电洞,以及高级DRAM中的储存节点电容。

图1:3D NAND结构,显示例如通道电洞的高纵深比(HAR)特征。

3D NAND的一些重点工艺挑战包括通道电洞和字线轮廓的可变性和缺陷率,以及连接触点和阶梯的短路。DRAM的挑战包括存储节点电容轮廓的可变性和缺陷率、位线缺陷以及多重图案化误差预算不断减少。改善这些深窄孔的工艺需要克服缺陷和轮廓控制的挑战——在开发阶段实现良率,并最终在批量生产中提高和维持良率。对于其中一些挑战目前已有明确的工艺控制解决方案,而其他挑战则仍处于开发阶段。解决这些复杂堆叠的工艺问题需要多管齐下。

第一道防线–设备监控

当涉及颗粒缺陷时,首先最好避免它们。在进一步的图案化步骤中,这些颗粒可能变成如短路和断路等良率限制缺陷。因为HAR堆叠和3D NAND的一个工艺步骤中就包括许多沉积层,所以避免缺陷尤为重要。清洁的工艺设备不会有颗粒落入薄膜堆叠中。因此,确保工艺设备的清洁度可以主动地避免埋藏颗粒缺陷。控片晶圆检测可以对反应室进行高采样监控,迅速发现任何颗粒问题。然而,一些缺陷仅在图案晶圆上出现; 因此,全面的设备监控策略还包括对图案化晶圆进行充分采样。

设备监控策略的另外一个重要的方面是反应室监控。单一蚀刻设备内的温度均匀性以及设备之间的匹配对于在晶圆上保持蚀刻轮廓均匀以保持通道电洞形状一致是非常重要的。这种均匀性对于这些微米级蚀刻工艺尤其重要,因为它们具有严格的埃级精度要求。对反应室的温度监测可以自动化,将当前数据与基准线数据进行比较,并在检测到偏差时迅速纠正。

为了保证设备监控有效工作,工艺设备的条件应尽可能接近生产环境。温度监测应在“等离子体开启”的蚀刻条件下进行,控片监控应包括真实的薄膜叠层。由于产品晶圆的复杂集成方案,设备监控策略需要配备包括额外的在线高灵敏度检测和测量的第二道防线。

第二道防线-在线检测控制

具有HAR结构的在线产品晶圆需要监控晶圆表面及其前层的缺陷。对晶圆表面上的缺陷进行检测将有助于在表面层上发现颗粒和图案类型缺陷。

高纵深比晶圆生产中另一个工艺控制问题是晶圆弯曲。3D NAND结构采用交替材料堆叠,在晶圆上产生很大应力。一个深入的工艺监控方案还需要监控晶圆的弯曲和翘曲程度,确保其仍然符合下游工艺步骤的规格。

那么,HAR堆叠中的埋藏缺陷怎么办?通常,可以在多个工艺步骤中进行晶圆检测发现缺陷起源。然而,3D NAND的通道电洞蚀刻之前的堆叠沉积是一个工艺步骤,因而没有机会暂停工艺进行检测。理想情况下,工艺工程师可以通过保持极其干净的工艺设备来避免埋藏颗粒,但仍会出现与集成相关的缺陷。埋在堆叠中的缺陷是目前高产量中直接检测面临的挑战。

与此同时,晶圆厂正在寻求检测埋藏缺陷的替代策略。埋藏缺陷将会改变其周围环境,并扰动晶圆顶部的图案。对于圆形通道电洞,这种扰动可能导致临界尺寸(CD)大约10%的变化,这可以通过高灵敏度晶圆检测系统发现。另一种解决埋藏缺陷的检查策略是采用对晶圆的破坏性回蚀来暴露如蚀刻不足之类的工艺问题,并随后进行高灵敏度缺陷检测。

在缺陷检测的同时,内存制造工程师部署了基于量测的各种在线控制策略,用以研究诸如轮廓、叠对和工艺窗口等图形化问题。对于3D NAND和DRAM,光学散射测量可以提供有限的结构讯息,而像TEM这样的破坏性实验室技术则是揭示完整轮廓形状的唯一方法。目前还没有针对通道电洞或存储节点电容之类的HAR完整轮廓的迅速且非破坏性的测量。与3D NAND相比,DRAM的叠对要求更趋严格,因为存储节点电容的构建采用了双重或三重图案。多重图案化建立具有小且密集的特征,当与激进的HAR蚀刻工艺同时使用时,建立工艺窗口将变得具有挑战性4。这是一个应用综合工艺窗口发现、扩展和控制策略(图2)的机会,帮助晶圆厂团队识别可能的热点问题,取得有效工艺窗口5。

图2:工艺窗口的发现、扩展和控制策略。第一步是确定热点的相关设计和工艺起源; 第二步是通过全厂范围的工艺改进来扩展工艺窗口,第三步是实施检测和量测,发现并控制关键工艺随时间的波动变化。

所有这些测量建立了一个全厂范围的数据流,必须将其与智能数据分析相结合,推动工艺控制的反馈回路以及高效的工程分析。

不要遗忘晶边

晶圆边缘附近的HAR结构往往有最多的工艺控制问题。为了取得最高良率,晶圆厂工程师必须加强对晶圆边缘的检测控制,并且采用与晶圆的其余部分相比更为密集的采样。

新内存技术

随着3D NAND和DRAM持续发展,堆叠高度不断增加,而特征尺寸不断缩小。此外,将NAND的容量、成本和非易失性与DRAM更快的存储速度相结合的尝试已经促进了许多新型内存的开发。这些新型内存包括相变内存(PCM)、铁电RAM(FeRAM),自旋转移扭矩磁阻RAM(STT-MRAM),电阻RAM(RRAM或ReRAM)等6。

随着3D NAND和DRAM中的先进节点而不断发展的新技术,以及与新型内存类型相关的新工艺流程,都需要晶圆厂不断调整其工艺控制策略,持续提升先进的内存元件的生产和良率。

參考文献:

1.Sung-Kye Park, “Technology scaling challenge and future prospects of DRAM and NAND flash memory,” Proc. of International Memory Workshop (IMW), 2015 IEEE International, May 2015.

2.M. LaPedus, “How to make 3D NAND,” Semiconductor Engineering, May 23, 2016. https://semiengineering.com/how-to-make-3d-nand/

3.T. Lill, “Overcoming Challenges in 3D NAND Volume Manufacturing,” Proc. Of International Memory Workshop (IMW), 2017 IEEE International, May 2017.

4.M. LaPedus, “1xnm DRAM Challenges,” Semiconductor Engineering, Feb. 18, 2016. http://semiengineering.com/1xnm-dram-challenges/

5.A. Cross, “Process Window Discovery and Control,” Semiconductor Engineering, Dec. 18, 2017. https://semiengineering.com/process-window-discovery-and-control/

6.B. Bailey, “New Memories and Architectures Ahead,” Semiconductor Engineering, Feb. 13, 2017. https://semiengineering.com/new-memories-and-architectures-ahead/

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 上海泰矽微宣布完成新一轮战略融资,博奥集团战略入股

- 2 三方联合,上海国际汽车电子与半导体应用展览会将于明年4月在上海举办

- 3 破除AI落地难题!英特尔全新软硬件平台,助力企业AI创新

- 4 6月5-7日,南京见!2024南京国际半导体博览会邀您共赴盛会