台积电打造WLSI平台,积极布局先进封装

来源:内容来自「芯思想」,作者 赵元闯,谢谢。

2018年10月20日,蒋尚义在“2018年首届中国集成电路国际高峰论坛”发表演讲时指出,在后摩尔时代,他个人看好封装技术的发展。从整个系统层面来看,如何把环环相扣的芯片供应链整合到一起,才是未来发展的重心,封测业将扮演重要的角色。有了先进封装技术,半导体世界将会是另一番情形。现在需要让沉寂了三十年的封装技术成长起来。蒋尚义也在2009年推动台积电进入先进封装领域。

确实在后摩尔时代,先进的封装技术将更提升后段制程对于半导体产业的重要性。目前,摩尔定律已经走到了一个极限,晶圆制造厂正在往下游延伸,而封测厂也在积极往上游拓展,也许就在某一点碰撞在一起,这是自然的产业发展,也是对晶圆制造厂和封测厂两者的挑战。

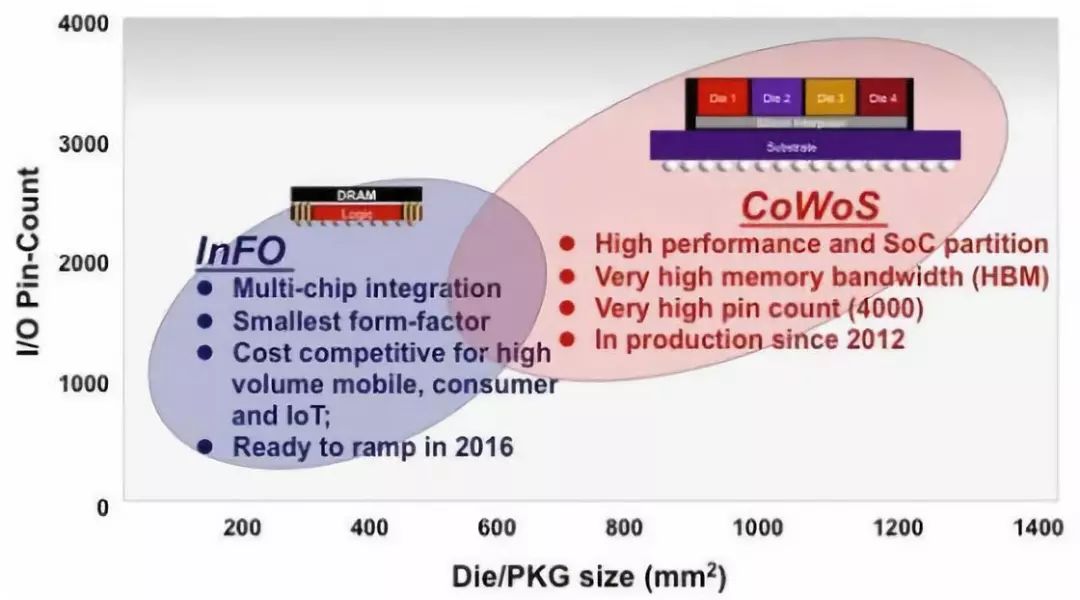

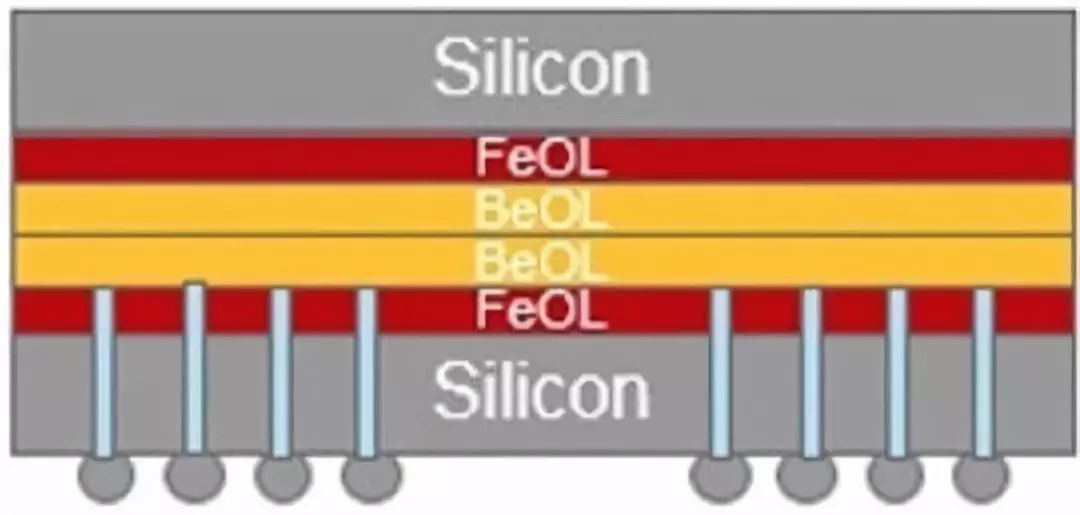

经过10年的构建,目前台积电已经完成晶圆级系统整合(WLSI)技术平台,该平台利用台积电公司工艺制程与产能的核心竞争力,建立支援异质系统整合与封装能力,以满足特定客户在芯片性能、功耗、轮廓(Profile)、 周期时间及成本的需求。晶圆级系统整合与相关技术平台,包括CoWoS(Chip on Wafer on Substrate)、整合型扇出(InFO,Integrated Fan-Out)及无凸块底层金属整合与技术(Under-Bump-Metallurgy Free Integration,UFI)持续发展以满足多样化市场的需求,包括移动运算、物联网、汽车以及高效能运算。

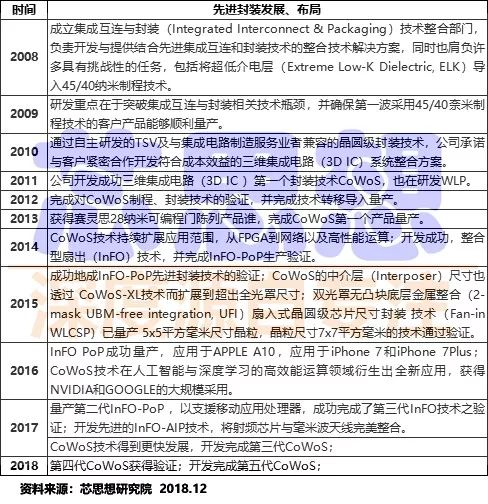

一、2008年开始先进封装布局

2008年底成立集成互连与封装技术整合部门,2009年开始战略布局三维集成电路(3D IC)系统整合平台;2011年推出CoWoS(Chip on Wafer on Substrate),2013年开始量产;2016年开始在苹果的A10处理器中采用InFO()封装,InFO成为台积电独占苹果A系列处理器订单的关键。

目前,台积电先进封装技术WLSI(Wafer-Level-System-Integration)平台包括既有的CoWoS封装、InFO封装,以及针对PM-IC等较低端芯片的扇入型晶圆级封装(Fan-In WLP),还有多晶圆堆叠(WoW,Wafer-on-Wafer)、系统级整合芯片(SoIC,system-on-integrated-chips)等封装技术,阵容更加齐整、坚强。

二、曾被内部称为昂贵的垃圾技术CoWoS在算力时代爆发

2009年6月,在辞去台积电CEO职务四年之后,张忠谋以78岁高龄,重新担任公司CEO。重新执掌权柄的张忠谋邀请蒋尚义重返台积电重新掌舵研发。当时最主要的任务之一,就是开发“先进封装技术”。

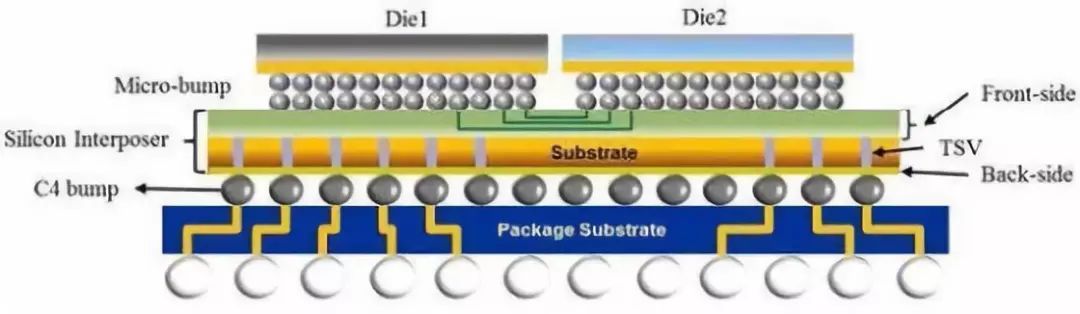

蒋尚义将此重任交给了余振华,并先后调拨约400名研发工程师参与。时任集成互连与封装技术整合部负责人的余振华率团队不负众望,于2011年完成CoWoS是将逻辑芯片和 DRAM 放在硅中介层(interposer)上,然后封装在基板上)。

CoWoS在手,张忠谋在台积电2011年第三季法说会上放言,台积电要进军封装领域。此举震撼半导体业界,特别是封装业。

当时,余振华表示,以后所有高阶产品都会用到CoWoS,市场很大。

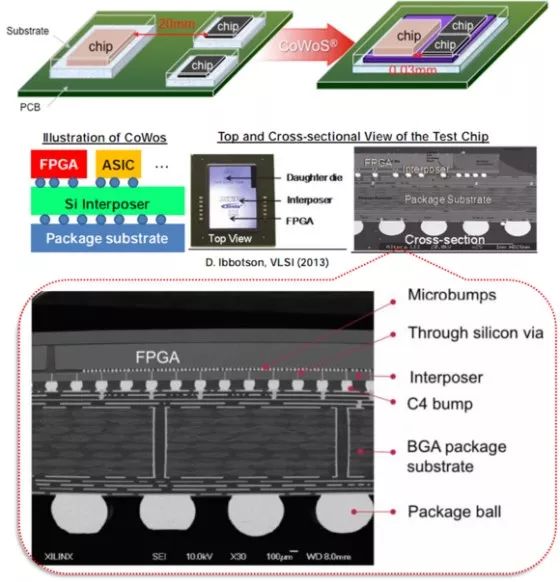

但事与愿违。虽说导入CoWoS技术,理论上可让处理器减掉多达70%厚度,提升处理器的性能,但由于成本的原因,CoWoS价格接近每平方毫米6美分,与客户的期望价格每平方毫米1美分相差太大。虽然有多家客户在验证CoWoS技术,直到2013年量产时,只有可编程逻辑门陈列供应商赛灵思(Xilinx)一家的28纳米产品量产。

此时,不光是余振华,就连蒋尚义也备感内部压力巨大。内部有人称CoWoS是昂贵的垃圾封装技术。

古语说的好“祸兮福所倚,福兮祸所伏”。正当CoWoS艰难时,AI出现了。CoWoS的新客户大量出现。余振华当年的预测成真:最新、最高阶的芯片,真的都必须用CoWoS。因为CoWoS可以让产品的效能提升3到6倍。

2014年底,只有赛灵思、阿尔特拉(Altera)两家可程式逻辑门阵列客户采用CoWoS封装技术,但随着制程推进到16纳米FinFET时,以及异质芯片整合趋势成形,2016年台积电开始为NVIDIA和Avago/Boardcom采用CoWoS封装。2016年,Nvidia推出首款采用CoWoS封装的绘图芯片GP100,为全球AI热潮拉开序幕;2017年Google在AlphaGo中使用的TPU 2.0也采用CoWoS封装;2017年英特尔的Nervana也不例外的交由台积电代工,采用CoWoS封装。2017年CoWoS封装产能由于AI 的爆发,产能已供不应求,迫使因成本高昂而坐冷板凳多年CoWoS封测产能首度扩充,将在原先以InFO产能为主的桃园龙潭封测三厂进行扩产。

目前第三代CoWoS封装技术能够提供现行约26mmx32mm倍缩光罩;而将于2019年量产的第四代CoWoS能提供现行2倍倍缩光罩,约1700平方毫米;而将于2020年量产的第五代CoWoS能提供现行3倍倍缩光罩,约2500平方毫米。倍缩光罩尺寸越大,可搭载更多不同的芯片、提供更大的核心面积、有更多的接脚数,让芯片功能更多元化、提升算力。

目前CoWoS已经获得NVIDIA、AMD、Google、XilinX、华为海思等高端HPC芯片订单。

三、InFO助力台积电独占苹果A系列处理器订单

2013年,对于只有一个客户的CoWoS来说,显得有点高冷。既然客户提出只能接受每平方毫米1美分的价格成本时,蒋尚义让余振华负责开发一种性能可以比CoWoS稍差但成本只能是每平方毫米1美分的先进封装技术。

余振华决定改用“减法”,将CoWoS结构尽量简化,最后出来一个无须硅中介层的精简设计,可以让芯片与芯片之间直接连结,减少厚度,成本也相对较CoWoS低廉,但又能够有良好的表现,适用于追求性价比的移动通信领域,在手机处理器封装中,减低30%的厚度,腾出宝贵的手机空间给电池或其他零件。这就是2016年首次开始在苹果的A10处理器中采用InFO封装,首度用在苹果iPhone 7与iPhone 7Plus中。InFO成为台积电独占苹果A系列处理器订单的关键。

2016 年 11 月,当首度采用InFO技术的iPhone 7大量出货之际,台积电公告,立下大功的余振华,擢升研发组织集成互连与封装处资深处长余振华博士为副总经理。

目前看来,台积电InFO技术成功应用于追求高性价比的移动通讯市场,AP产品是其主要客户。

2016年台积电买下高通龙潭厂,目的就是提供整体晶圆服务,从制造到后段晶圆封装,随后独揽苹果A10及A11处理器,位于龙潭的封装厂已全数满载。在产能需求大增下,台积电除扩充龙潭厂外,也决定于中科再扩增InFO后段高阶封测产能。

据悉,龙潭厂月产能从10万片已经扩增到13万片,并于2018年第一季量产,并取得龙潭二期用地;并确定在中科原台积电太阳能空厂中增加InFO产能。

原来业界有人表示,台积电InFO以后将会委外代工,但从目前台积电的扩产情况来看,似乎委外的可能性微乎其微。

四、SoIC让同体积芯片性能增加两倍

根据2018年4月台积电在美国加州 Santa Clara的24 届年度技术研讨会上的说明,SoIC是一种创新的多芯片堆叠技术,是一种晶圆对晶圆(Wafer-on-wafer)的键合(bonding)技术,这可能是一种3D IC制程的技术,也就是台积电可能已具备直接为客户生产3D IC的能力。

SoIC技术的出现表明未来的芯片能在接近相同的体积里,增加双倍以上的性能。这意味着SoIC技术可望进一步突破单一芯片运行效能,更可以持续维持摩尔定律。SoIC技术的发展关键就在于达到没有凸起的键合结构,因此它非常可能是采用硅导孔(TSV,Through-silicon Vias)技术,直接透过极微小的孔隙来沟通多层的芯片,因此有更佳的性能。

据悉SoIC根植于台积电的CoWoS与多晶圆堆叠(WoW,Wafer-on-Wafer)封装,SoIC特别倚重于CoW(Chip-on-wafer)设计,如此一来,对于芯片业者来说,采用的IP都已经认证过一轮,生产上可以更成熟,良率也可以提升,也可以导入存储器芯片应用。

更重要的是,SoIC能对10纳米或以下的制程进行晶圆级的键合技术,这将有助于台积电强化先进工艺制程的竞争力。

在2018年10月的第三季法说会上,台积电给出了明确量产的时间,2021年SoIC技术就将进行量产。

五、WoW工艺透过TSV提升GPU性能

2018年4月台积电在美国加州 Santa Clara的24 届年度技术研讨会上宣布推出晶圆堆叠(WoW)技术。由于晶圆上的平面空间有限,因此,WoW技术透过硅通孔(TSV)互连连接的10微米孔彼此接触,将多层逻辑运算单元以立体方式堆叠在一起,架构出高速、低延迟互连性能。虽然TSV互连早就运用在DRAM 及3D NAND 等存储器的生产技术上,但是用在逻辑运算单元的量产上,却还是首次。

藉由WoW技术,可以不再需要通过增加芯片物理尺寸,或缩小制造工艺来达到提升GPU性能的目的。由此GPU供应商Nvidia及AMD都将受惠。随着先进工艺技术的成熟和良率的提高,未来GPU供应商可以利用WoW技术,将两个或以上功能齐全的GPU堆叠放到一张显卡上,而不是使用两张显卡进行双系统的运算。如此不但能节省成本,而且还有体积更小、效能更佳、而且更加节能的优点。

据悉,WoW现在最大的问题就是晶圆的良率。这使得量产中的工艺的成熟度要扮演着重要的角色。不过目前看来,台积电的目标是把WoW用在未来的7纳米和5纳米制造工艺,而不是在具有高良率的16纳米或10纳米工艺节点上使用。

六、结语

台积电不仅在晶圆代工技术持续领先,已经量产10纳米/7纳米工艺制程,并透过晶圆级系统整合(WLSI)开发最先进的封装技术CoWoS、InFO PoP、WoW、SoIC。尽管台积电强调,其发展封测技术的主要目标,并非要与专业委外封测代工厂(OSAT)竞争,而是要全力拉开与三星电子(Samsung Electronics)、英特尔(Intel)等竞争者的技术差距。但从目前台积电的布局和扩产动作来看,不止于此。

今天是《半导体行业观察》为您分享的第1820期内容,欢迎关注。

推荐阅读

★ 新一年值得关注的20家模拟、MEMS和传感器初创公司,中国有3家上榜

关注微信公众号 半导体行业观察(ID:icbank) ,后台回复以下关键词获取更多相关内容

华为 | 中美贸易 | IPO | 财报 | 被动元件 | 开源 | 射频 | 5G | 展会

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!

关于摩尔精英

摩尔精英是领先的芯片设计加速器,愿景“让中国没有难做的芯片”,业务包括“芯片设计服务、供应链管理、人才服务、孵化服务”,客户覆盖1500家芯片公司和50万工程师。我们致力于提供ASIC设计和Turnkey解决方案,从Spec/FPGA/算法到芯片交付,包括:芯片架构规划、IP选型、前端设计、DFT、验证、物理设计、版图、流片、封装和测试服务等。 自2012年以来,我们的团队一直专注于积累技术能力,帮助客户实现最优芯片性能,并支持Turnkey、NRE、专业咨询和驻场等灵活服务模式。 摩尔精英目前全球员工200人,总部位于上海,在北京、深圳、合肥、重庆、苏州、广州、成都、西安、南京、厦门、新竹和硅谷等地有分支机构。

点击阅读原文,了解摩尔精英

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻