经典ASIC开发流程

来源:内容来自「不忘出芯」,谢谢。

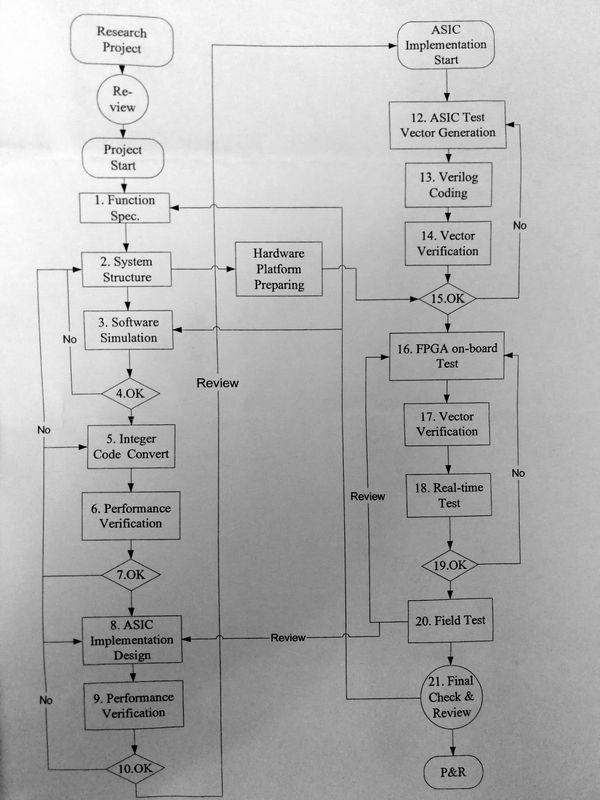

最近收拾书架,翻出一张多年以前的ASIC项目开发流程图,一起回顾一下。典型的瀑布式开发流程:

-

以算法设计为主导

-

算法C代码手工转换为RTL

-

RTL与算法C代码生成的测试向量对比进行验证

-

依赖FPGA做大量实时、现场测试

-

适合通信信号处理,音视频处理产品

1. 算法预研

确定了产品方向之后,算法工程师开始进行调研。

要学习研究行业内最新的研究成果、论文,提出创造性的方法来获得最好的性能。要使用真实的测试数据和仿真结果进行评估。 最终交付为算法描述的C语言源码。

算法调研结束后需要进行审核(review):确定算法性能,确定系统架构设计,确认是否可以正式立项。审核过程需要算法设计、RTL设计、软件、硬件系统、市场、管理层共同参与。

正式立项时,需要提供功能spec,以及算法C代码功能仿真环境。 与此同时,硬件组需要根据项目需求开始搭建硬件FPGA测试平台。

2. 算法优化

接下来进行算法的优化,主要考虑以下几个方面:

-

算法复杂度

-

算法运算量

-

变量精度

-

算法设计以及状态机控制要具有自恢复能力

-

算法代码要足够stable,对于各种滤波器系数和变量要有一定的噪声容忍度。

算法最终确定需要通过审核:算法架构, 算法功能仿真,算法定点化和性能验证。

3. 面向ASIC的C代码实现

在此阶段,算法C仿真代码改变为模块结构代码,分解为若干ASIC功能模块,代码的接口与RTL接口接近:

-

容易实现

-

高效率

-

节省逻辑

-

重用现有模块

-

对带有反馈的模块中增加仿真延时

-

在接口增加仿真延时

最终的C代码中:

-

主函数只包含连接关系和子模块

-

所有子模块以各自的时钟速率调用

-

接口采用cycle based timing

需要准备以下review和文档:

-

ASIC模块和接口设计指导

-

性能验证报告

-

接口变量的时序图和精度描述

4. C到RTL的实现

RTL设计工程师完成从C代码到verilog的实现。算法工程师负责产生相应的测试向量,包括子模块测试和系统联调测试。要使用各种典型的测试场景数据,以及一些子模块级别的随机测试数据。

根据RTL设计以及综合结果,可以获得整个系统的时序信息,gate count和die size预估。

5. FPGA on-board test

由于RTL仿真的速度较慢,可以借助FPGA来进行测试加速。硬件工程师准备FPGA平台,FPGA工程师进行RTL到FPGA的代码移植,软件工程师协助相关测试软件的开发与使用。

在FPGA上可以做到与RTL仿真一样的效果,比如从内存中提供输入,并抓取输出结果,与算法C产生的数据进行比对。需要测试尽可能多的测试用例。

6. FPGA field test

如果项目代码可以在FPGA上跑到与真实应用同样的速度(full speed),就可以用FPGA代码直接做实时现场测试。在现场测试的任何问题,需要反馈给算法组进行分析解决。

7. Final Check and Review

现场测试通过后,需要做最后的检查和review全部代码,然后开始芯片后端设计。

站在今天( 2018年 )的角度看过去上述 流程有存在一些问题:

-

采用算法C到Cycle C再到RTL实现的流程,迭代长,易出错

-

RTL验证以直接定向测试为主,缺少随机验证,覆盖率不够

-

依赖FPGA实时测试作为验证主要手段,FPGA平台开发需要专门的人力资源和硬件平台,而且FPGA平台不够灵活,且容易出现不稳定的问题。

现在已经有很多新技术可以借鉴,比如

-

基于High level synthesis,缩短开发周期

-

采用各种验证方法学,提高验证覆盖率

-

使用专用的硬件加速器平台

最后,以上开发流程简单,投资少,对于算法(大牛)主导的创业型公司,或者以IP开发为主的小型团队,还是可以使用的。

以上抛砖引玉,欢迎一起交流。

今天是《半导体行业观察》为您分享的第1841期内容,欢迎关注。

推荐阅读

识别二维码,回复关键词

回复关键词,阅读更多

并购|财报|CES|开源| 射频|5G|氮化镓|展会|老兵戴辉

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!

关于摩尔精英

摩尔精英是领先的芯片设计加速器,愿景“让中国没有难做的芯片”,业务包括“芯片设计服务、供应链管理、人才服务、企业服务”,客户覆盖1500家芯片公司和50万工程师。我们致力于提供ASIC设计和Turnkey解决方案,从Spec/FPGA/算法到芯片交付,包括:芯片架构规划、IP选型、前端设计、DFT、验证、物理设计、版图、流片、封装和测试服务等。 自2012年以来,我们的团队一直专注于积累技术能力,帮助客户实现最优芯片性能,并支持Turnkey、NRE、专业咨询和驻场等灵活服务模式。 摩尔精英目前全球员工230人,总部位于上海,在北京、深圳、合肥、重庆、苏州、广州、成都、西安、南京、厦门、新竹和硅谷等地有分支机构。

点击阅读原文,了解摩尔精英

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻