[原创] 现在需要怎样的EDA工具?

平静了接近二十年的Fabless投资终于在最近两年迎来了新爆发。

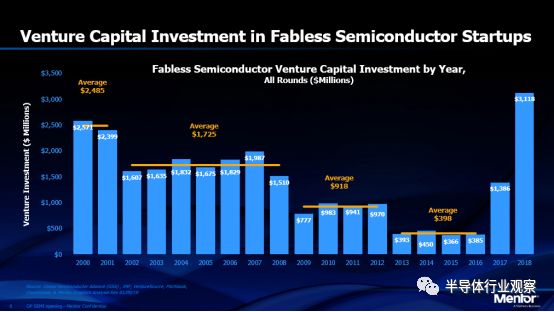

据Mentor, a Siemens business全球副总裁兼亚太区总裁彭启煌先生介绍,走向Fabless领域的风险投资在冷了差不多十年之后,终于在2017年迎来大爆发。数据显示,当年全球Fabless产业获得风险投资为13.86亿美元,较之前一年的3.85亿美元暴涨260%。在随后的2018年,这个数字更是狂飙至31.18亿美元,创下了21世纪以来的新高。

Fabless领域自2000年以来获得的风险投资总结

“这些投资主要集中在AI、加密货币、5G和存储等领域,尤其是AI领域,更是这波投资的主要关注点”,彭启煌指出。按照他的说法,这是行业发展的必然结果。

Mentor, a Siemens business全球副总裁兼亚太区总裁彭启煌先生

首先,他指出,最近几年,因为算法的成熟,人工智能开始在各个领域产生巨大的影响,尤其是自动驾驶汽车和智能手机,更是对芯片的性能提出了更高的要求。然而我们也看到,传统的通用CPU在摩尔定律失效等多种因素的共同影响下,性能上已经不能再满足现在的新兴应用需求,这就驱使了ASIC的产生,而AI芯片就是在这波转变中崛起的;

其次,彭启煌还指出,最近几年系统厂商研发芯片逐渐成为主流,并有愈演愈烈之势,这就带来了从系统到IC的协作和处理的需求;

再者,芯片现在的规模越来越大,单位芯片上集成的晶体管也越来越多,但因为市场竞争的激烈性,开发者对芯片Time To Market的要求也越来越苛刻,这就给相关供应商,尤其是EDA厂商带来巨大的挑战。Mentor作为芯片设计行业内的专家,并且被系统软件的领先厂商西门子收归到麾下,这就让新的Mentor在应对这些新需求的时候游刃有余。

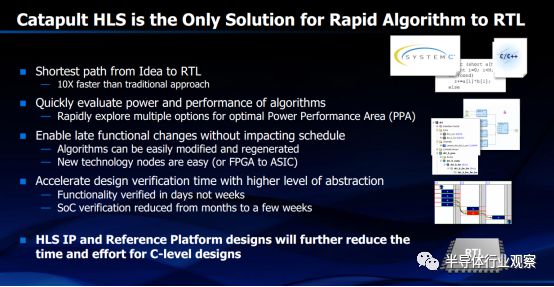

例如为了加速从设计启动到RTL验证收敛时间,Mentor 在其Catapult 平台引入HLS(High-level synthesis),让工程师在做芯片的时候,可以直接使用C++这样的高阶语言直接综合,然后工具就可以自动生成硬件设计,甚至可以不需要RTL而直接进入Physical Layout。这意味着软件工程师可以直接从应用和算法开始,用高级语言描述系统,然后把下面的工作都交给工具完成,大大简化了芯片的设计流程,降低了芯片设计的进入门槛。

据了解,英伟达在设计其Tegra X1芯片的时候,就使用了Mentor的这套工具,验证成本降低了80%,效率提升了50%。以前传统RTL需要1000 个CPU工作 3个月,但使用HLS C++只需要14个CPU工作两星期,效率和成本则大大提升;而谷歌在设计其VP9芯片的时候也将时间缩短了一半,仿真效率更是提升了五百倍。

面对现在汽车的电子化程度越来越高,从芯片到系统的验证需求也越来越多的转变,Mentor也将其本身在IC设计的经验和西门子的系统经验结合,为相关厂商提供全面的支持。

“我们的EDA工具一方面可以提升AI芯片的设计效率,同时也希望把AI引入到EDA当中,提高EDA的效率。我们的目标是在未来的芯片设计中,将那些基本的问题交给工具的AI处理,而把精力投向那些深层次,能够提升芯片竞争力的方面中去,”彭启煌强调。

-

- 半导体行业观察

-

- 摩尔芯闻