DARM和新兴存储器的最新路线图

去年IEDM(国际电子器件会议)期间的一个周日的夜晚,TechInsights举办了一场招待会,Arabinda Das和Jeongdong Choe在会上做了演讲,吸引了一屋子的与会者。在第一部分,我们分享了有关NAND的未来发展路线图预测,今天我们再来看一下有关DRAM和新兴存储器的发展预测。

DRAM Technology

DRAM 技术

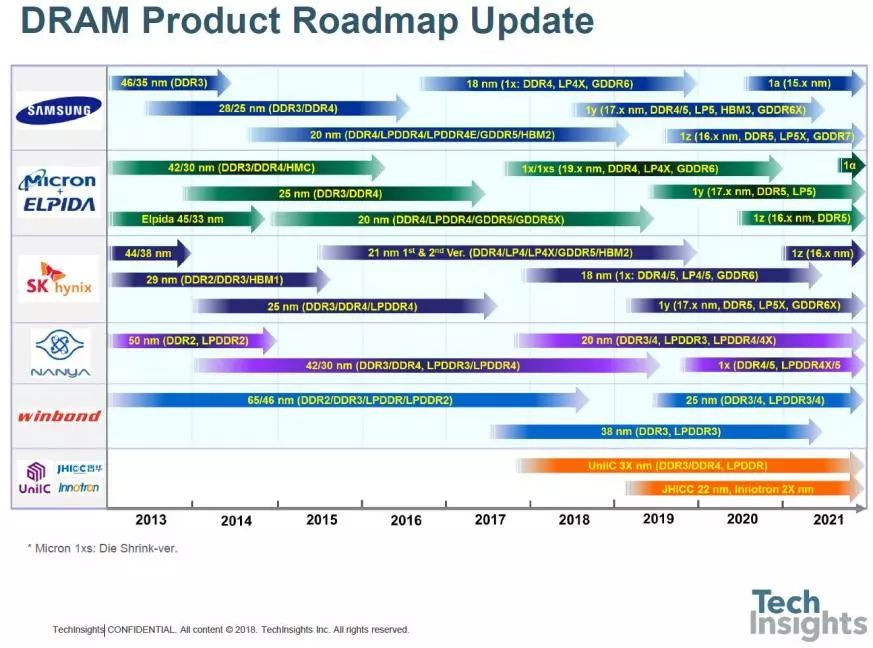

演讲的DRAM部分,首先是路线图:

我们现在已经进入了1x-nm的代际,今年推出了17-nm的器件。如果你相信制造商的话,我们仍然会每年都推出一代微缩,即便差距变得更小,现在我们是在20nm以下。几年前,我倾向于认为,在技术达到极限之前,我们可能会在1x-nm的某个节点上拥有两代产品,但现在看来,我们至少会看到四代产品,这可能至少会让我们坚持到2025年。

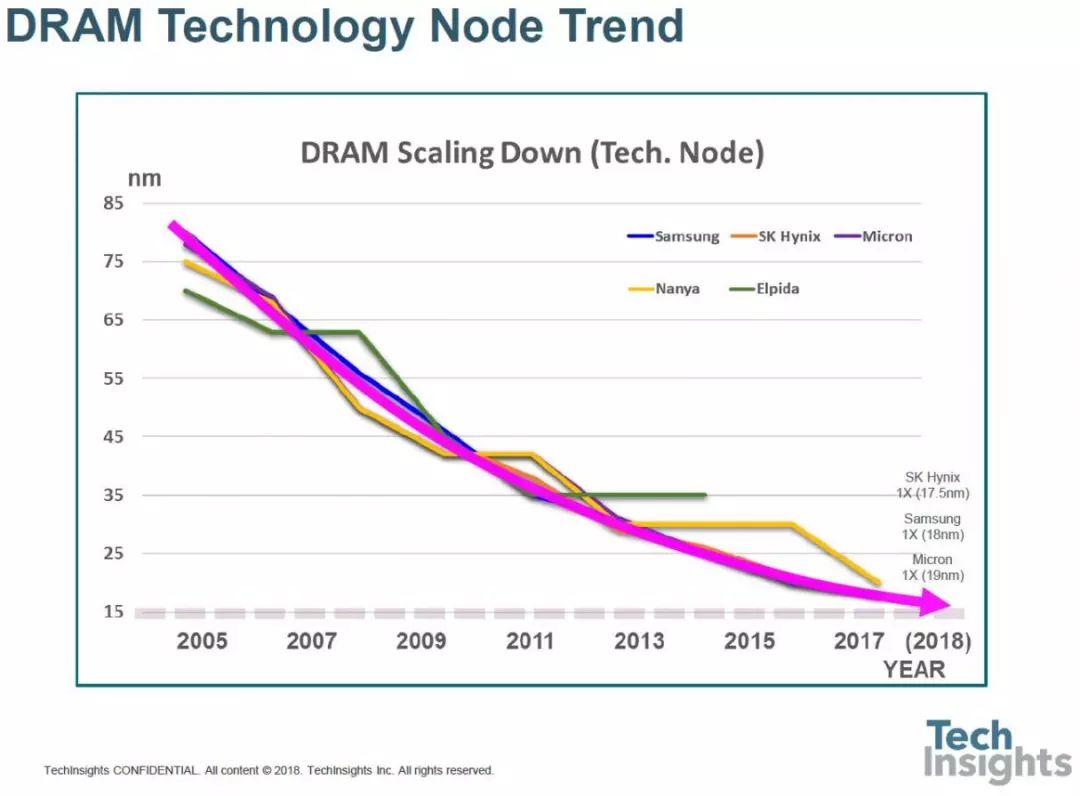

从节点的时间趋势可以看出微缩速度的放缓:

Elpida在被美光收购之前就已经停滞不前,Nanya也是如此。

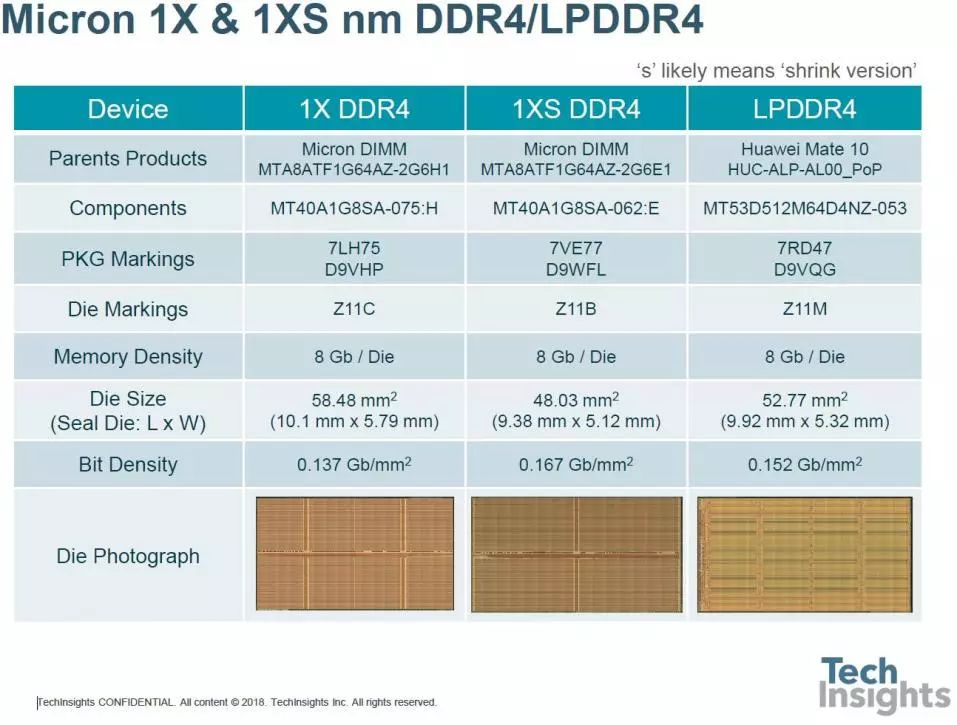

Jeongdong还向我们提供了一些最近的美光存储器的细节,可以看到,在8-GB芯片中,位密度现在达到了0.167 Gb/mm2。

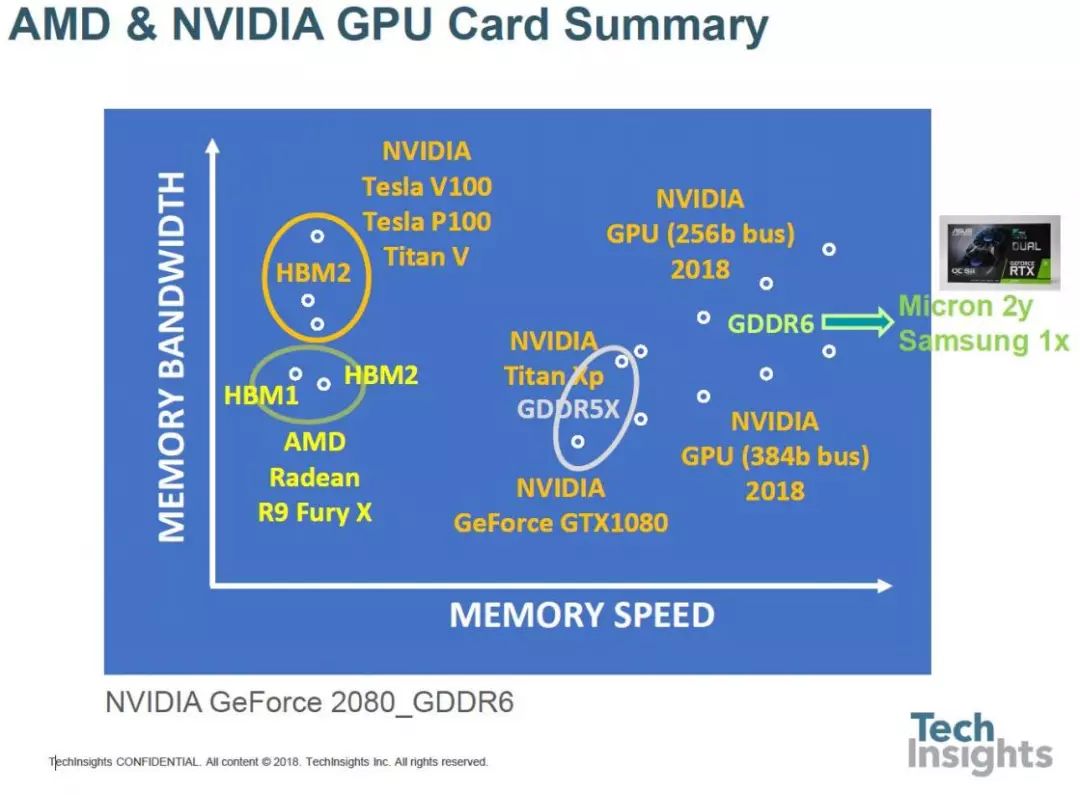

然后,我们看看AMD和英伟达GPU,说明了HBM(高带宽内存)和HBM2的使用、以及从GDDR5X迁移到GDDR6时带宽和速度的增加。

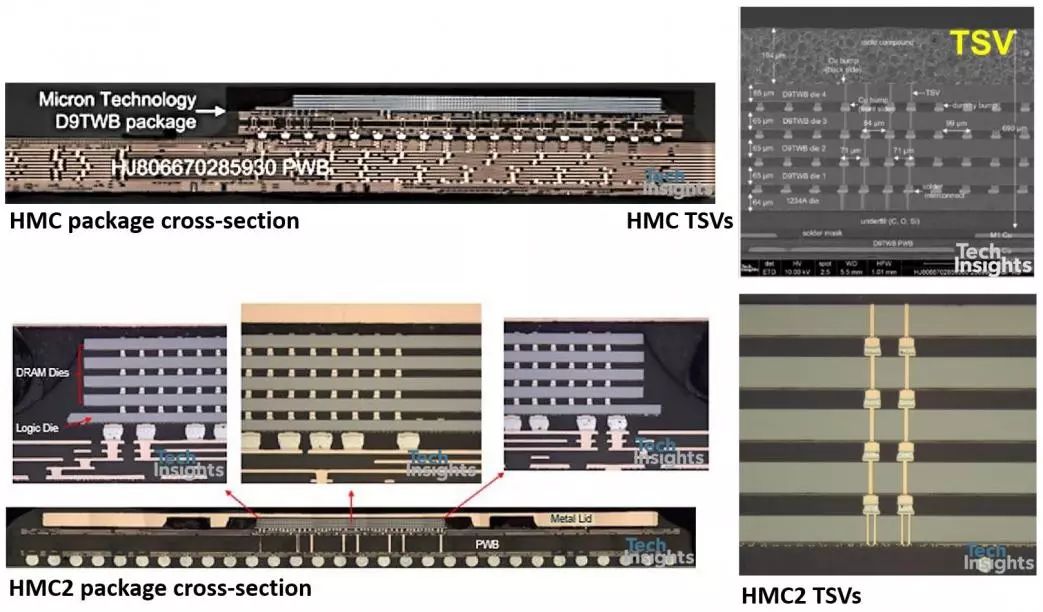

提到HBM会让人联想到美光的HMC(混合存储立方体),它现在已经演进到了HMC2。最初的HMC用于英特尔Knight‘s Landing处理器,这是一种4-stack DRAM,底部是IBM制造的控制器芯片,用硅通孔(TSV)相连。HMC2似乎是作为一个独立产品推出的,但它仍然是带有控制器的4-stack,HMC和HMC2都使用30nm级DRAM。

HBM和HMC都使用TSV,但它们是不同的东西;HMC有它的控制器芯片,并完全封装在PCB基板上;而HBM是与silicon interposer一起使用的。然而,美光已经宣布停止使用HMC,所以即使我们看到了它,它也不会再存在很长时间了。

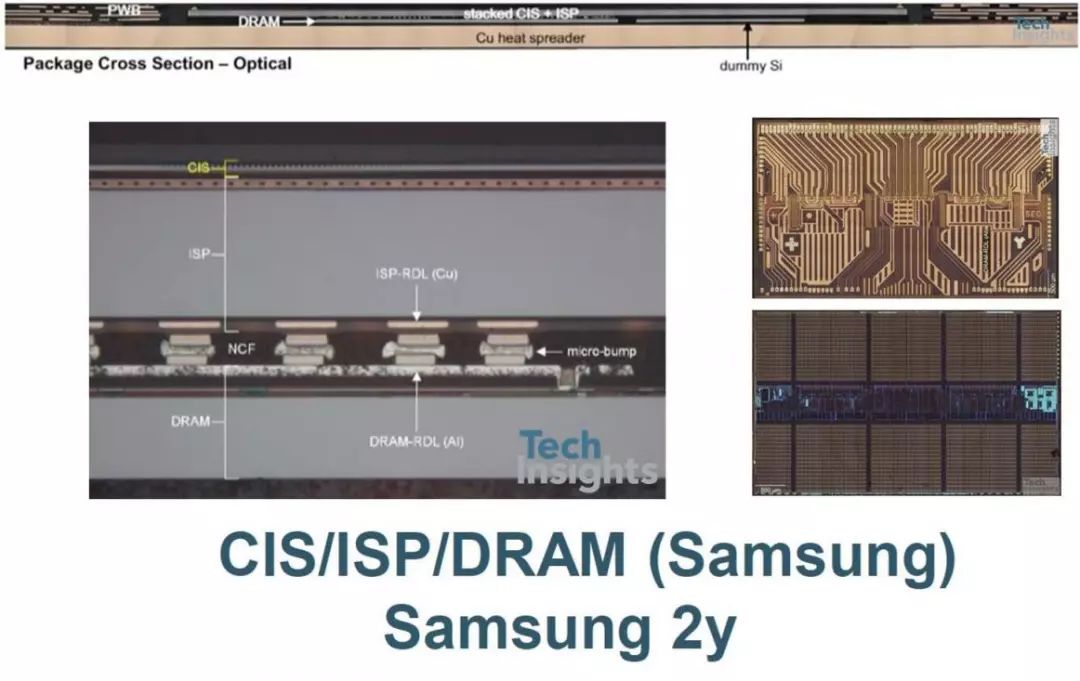

DRAM部分的最后一张幻灯片介绍了索尼和三星用于手机摄像机的CMOS图像传感器(CIS)和处理器(ISP)。在索尼IMX400中,DRAM被夹在CIS和ISP之间;CIS与DRAM脸对背安装,DRAM与ISP面对面安装。将DRAM放在stack中可以让相机系统以960帧/秒的速度运行,从而实现慢镜头功能。IMX400是在索尼Experia XZ手机上发布的,当时我们发表了一篇博客。

三星S5K2L3 ISOCELL快速成像采用了不同的方式——CIS和ISP传统上是面对面放置的,并使用TSV进行电气连接,标准DRAM芯片在ISP上面对背进行微凸点连接。微凸点将DRAM上的重分布层(RDL)连接到ISP背面的基于Cu的RDL,从而将它们连接到TSV,通过ISP基板连接到前端金属。DRAM芯片旁边还有一个虚拟芯片。

新兴存储技术

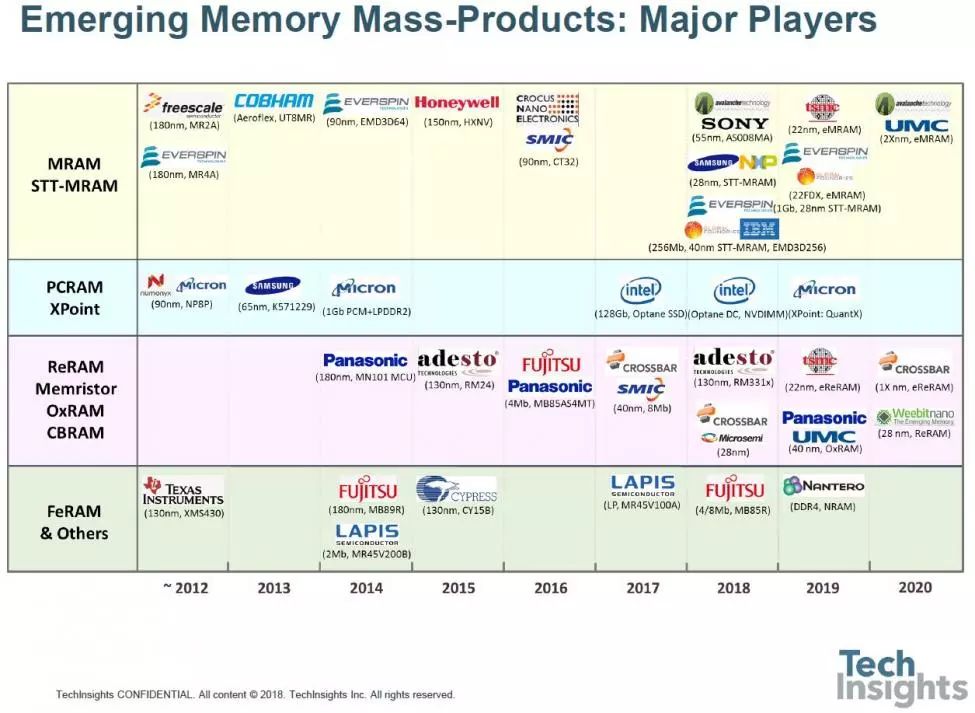

Jeongdong在演讲的最后部分回顾了新兴存储技术——尽管有些存储器有多“新”还有待讨论,因为它们已经问世一段时间了。路线图如下:

例如。Everspin目前已经制造了各种类型的MRAM,相变存储器(PC-RAM)已经被多家公司多次试用,而富士通多年来一直在生产FeRAM。

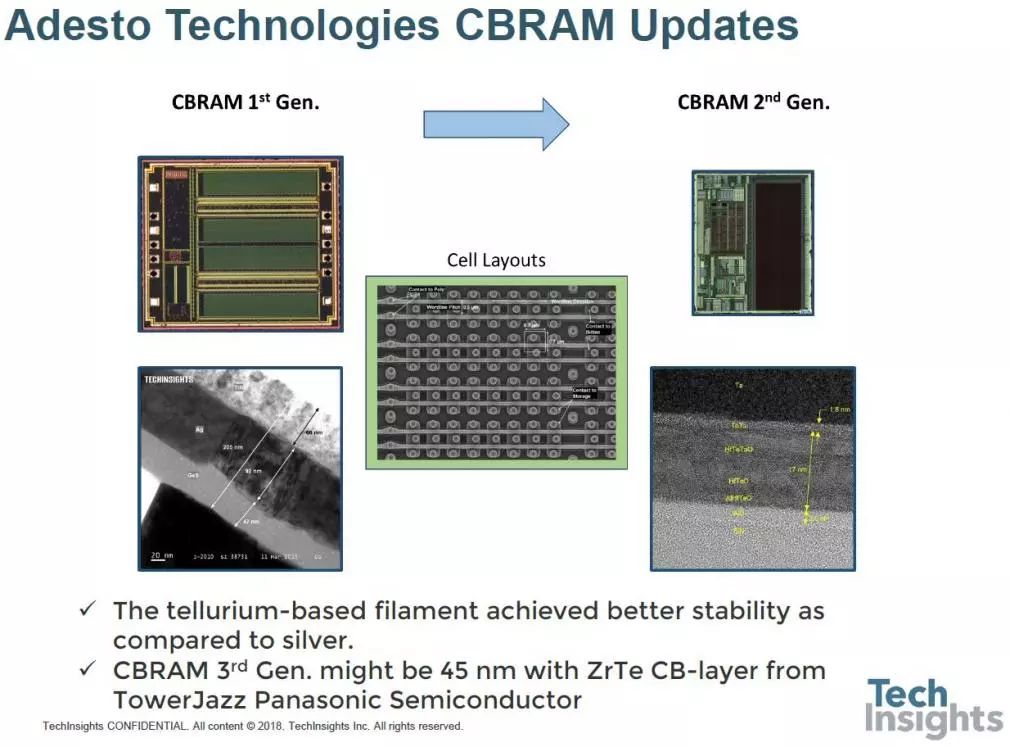

第一个例子是Adesto CBRAM(导电桥RAM),他详细介绍了第一代和第二代CB存储器之间的变化。

在结构上,桥层已经从银/锗硫化物变为基于碲的多层叠层,我认为它的温度敏感性不如银。

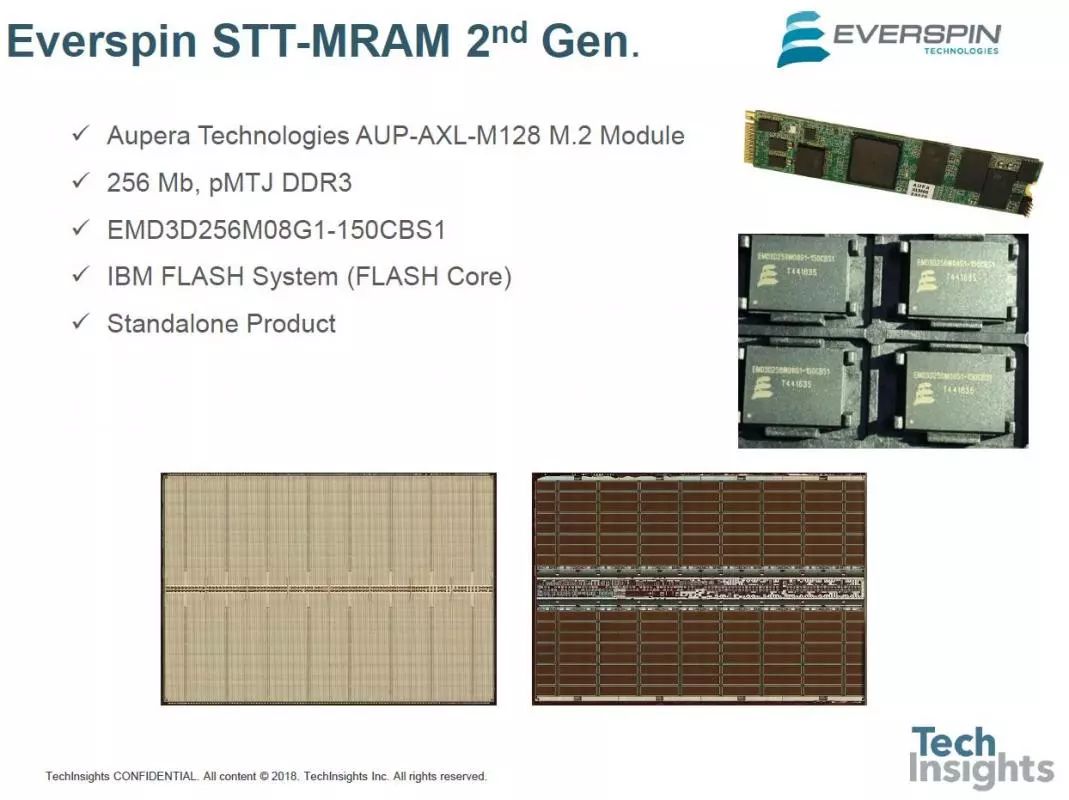

然后,他向我们展示了256-Mb EverSpin第二代STT-MRAM,它使用了DDR3格式的垂直-MTJ(磁性隧道结)技术。

作为结束演讲的3D-Xpoint幻灯片的引导,他提醒我们PC存储器已经存在了一段时间,我们已经从128 Mb、90nm工艺发展到16Gb、20nm工艺:

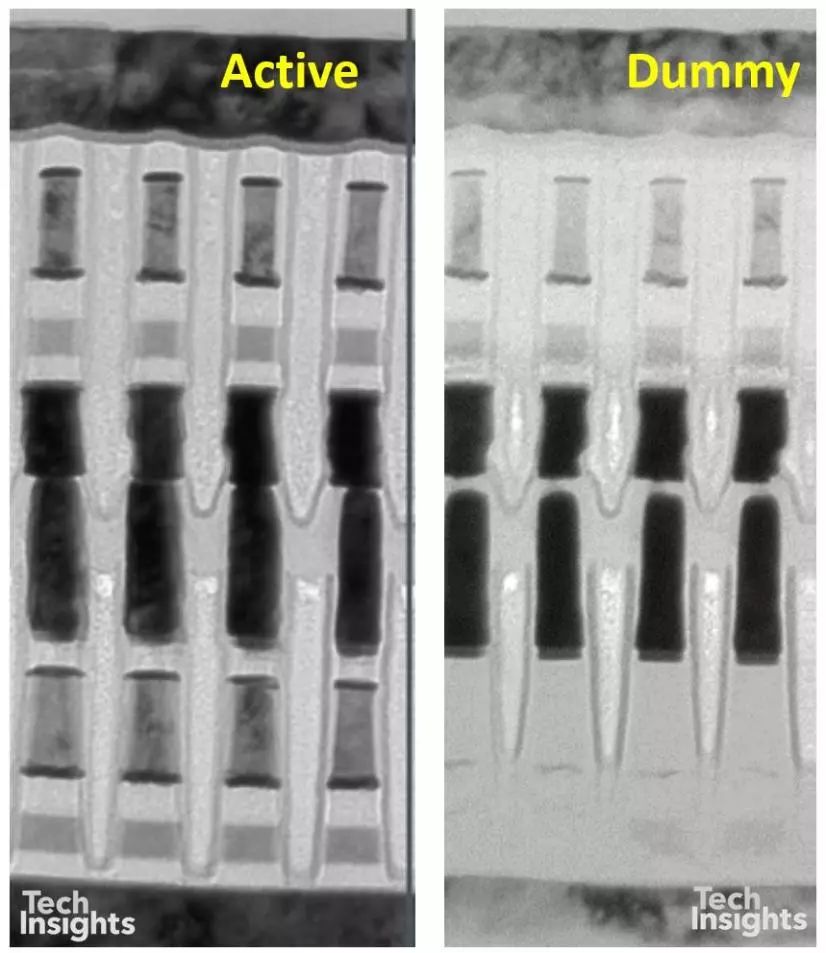

看来,至少在英特尔Optane版本的3D Xpoint中,存储器层次之间(即金属4和金属5之间)有虚拟存储块,它们没有驱动电路,所以电路区域与存储阵列区域不同。双stack存储单元也存在结构上的差异,在较低的单元中,似乎并没有存储层和选择层(尽管在这幅图像中有很多它们的阴影,但消失的可能是样本的虚像)。然而,中间的钨字线是明显分开的。

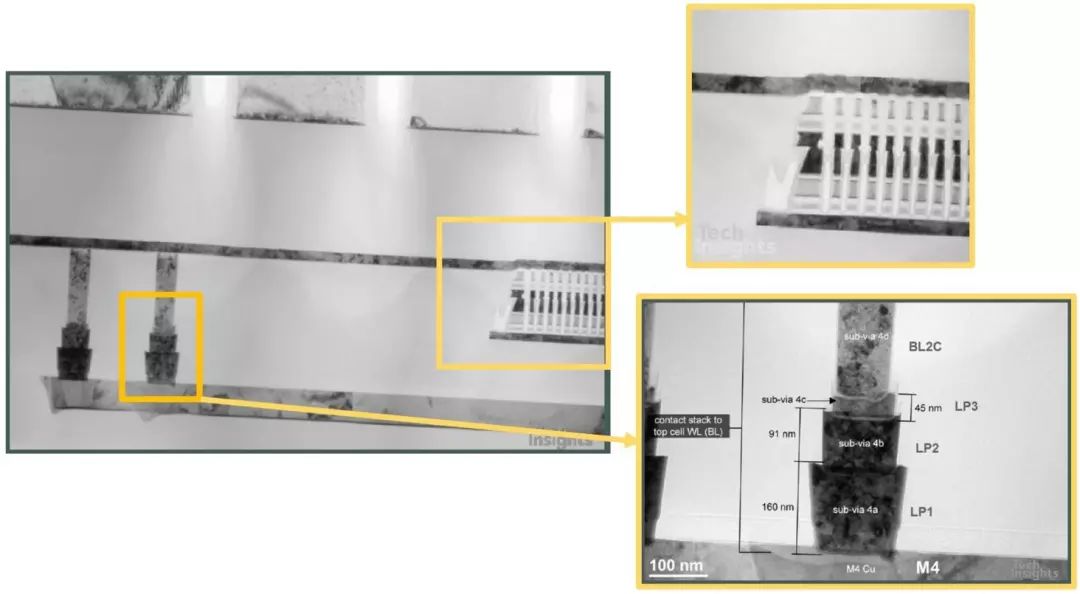

这两层的堆叠无疑会增加工艺的复杂性,因为我们必须将沉积、蚀刻和光学步骤加倍;在底层,字线位于堆栈的顶部,而顶层堆栈的底部有字线;而位线则相反。

在M4和M5之间添加存储层对这些层之间的通孔结构带来了其他挑战,需要更多的掩模层和相关的成本。上面的字线和位线实际上是从下面连接的,例如,位线有一个sub-via的堆栈,可以到达最高的位线层次。

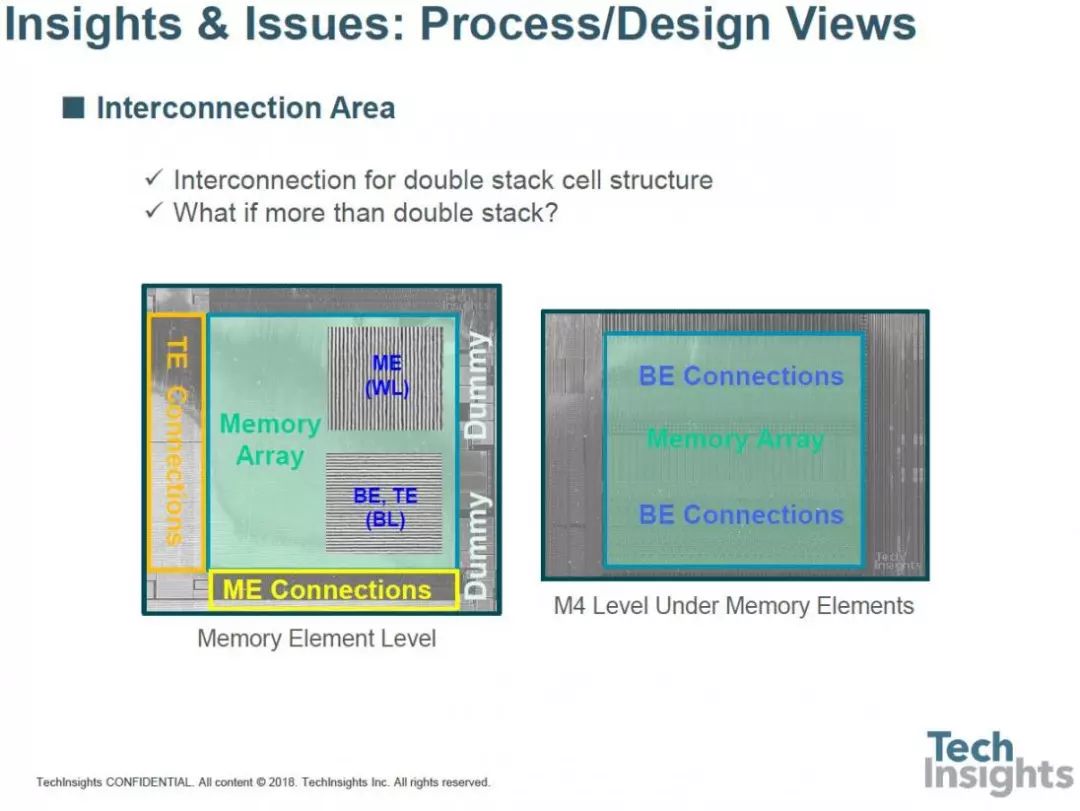

在平面图中,它看起来同样复杂,所以这就提出了一个问题:如果我们想要的不仅仅是双堆叠结构,我们该怎么办?(BE/ME/TE 分别代表底部/中部/顶部电极。)

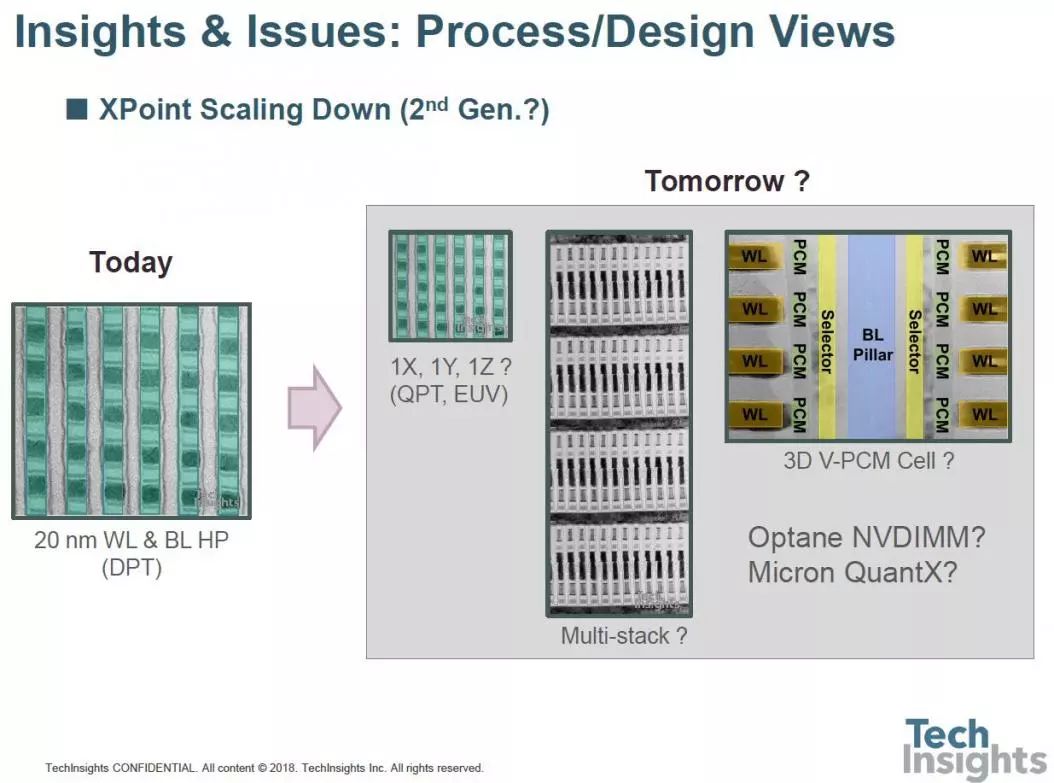

目前正在使用的是双重曝光,但当然也有可能使用四重曝光,甚至是EUV,或许是多堆叠或3D结构:

演讲就此结束。以上信息以及更多信息,都可通过TechInsight的Memory订阅获得。

-

- 半导体行业观察

-

- 摩尔芯闻