以管窥豹,X86服务器芯片将走向何方?

增量变化是人类成功的秘诀,在某些方面也是最困难的。 我们需要推动事情向前发展,但与此同时,我们不能打破先前行之有效的做法。 这就是我们如何从各种各样的系统中得到越来越多华丽的架构,从CPU插槽内部到超大规模数据中心,再到融入地球的政治、经济和文化网络。

英特尔Pentium和Xeon服务器处理器中包含的X86架构非常复杂,并且不断进行调整,以适应越来越多的应用程序的处理需求,而这些应用程序本身的复杂性也在不断增加。 如今,没有多少企业是容易的,但要找到一家比设计CPU并让CPU制造工艺不断发展的企业,或是找到一家比一代代地实现这一工程壮举的企业更有经济回报的企业,则更加困难。

随着两周前推出的“Cascade Lake”Xeon SP处理器,英特尔再次将其架构向前推进了很多,因为它目前使用的是14nm晶圆蚀刻技术。 但是英特尔在处理器上的改变和它的“Apache Pass”Optane内存模块的交付,以及将3D XPoint带入DDR4主内存,这些都是使处理器吸引客户的重要方面,即便“Cooper Lake”Xeon SP针对机器学习工作负载进行了一些调整,采用了新架构,以及备受期待的10nm晶圆工艺的“Ice Lake”Xeon SP将于今年年底推出,2020年上路。

自从英特尔推出“Nehalem”Xeon 5500处理器以来,数据中心发生了很大变化,因为AMD仍在激烈竞争,坦率地讲,公共云业务规模很小,超大规模用户对系统业务的影响不像今天这样大。

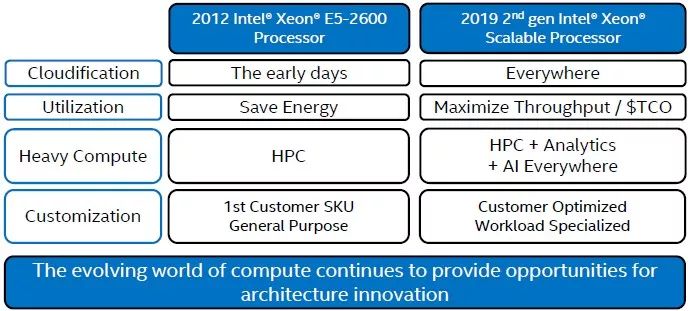

Ian Steiner是英特尔首席工程师、处理器首席架构师,以及自Nehalems以来Xeons所有产品的功率和性能架构师,他在一次关于Cascade Lake Xeon SP细节的演示中,把架构比较基准线画在了2012年3月推出的“Sandy Bridge”Xeon E5-2600处理器上,这是英特尔架构上的一个重要飞跃,顺便说一下,由于设计和32nm制造工艺的问题,该器件的高端产品有22.6亿个晶体管和核心,因此出现了一些延迟。Skylake和Cascade LakeXeon SP处理器,以及那些经过改进的14nm处理器,内置28个内核,以及大量“非核”电路,总共80亿个晶体管。 但市场上的差异比这些基本的“进料和速度”所暗示的更为深刻,正如Steiner所示:

Steiner在一次关于Cascade Lake处理器架构的简报中解释说: “从那时起,情况发生了很大的变化。 公共云才刚刚开始。 我们有很多客户真的很担心节能、规格和其他测量指标,但今天客户真正困扰我们的是我们如何才能提高他们系统的吞吐量,并真正利用我们正在进行的一切投资。 因此,我们在系统中添加的很多功能与运行传统基准测试以及如何将系统使用到其峰值无关。 我记得我在2010年读过一些关于数据中心以20%的利用率运行的文章,如果我是一个财务人员,那么会让我非常生气。 如果客户真的以20%的利用率使用我们的系统,我们想知道如何使他们达到50%、60%、甚至70%、80%。 这一直是我们关注的重点之一。 ”

Steiner还说,在这七年里,高性能计算的本质也发生了很大变化。 “我们在市场的其他部分看到了更多的计算量,随着AI和其他一些分析工作负载的增加,许多高性能的计算特性正在扩展到其他用例。 这只是刚开始,但我们认为这在未来将会继续发展。 ”在客户的敦促下,英特尔在CPU市场引发的另一个重大变化是定制化。 第一个定制的英特尔CPU是在Sandy Bridge时代,就像Steiner所言,现在英特尔有“成堆”的定制CPU。 对Cascade Lake生产线的快速回顾显示了大规模定制是如何进行的,英特尔在处理器上进行各种调节来激活或禁用处理器特性,并调高或降低时钟速度来调整特定工作负载的性能,这是一种常态。 下图是一个简易的图表,展示了Cascade Lake产品线中主要SKU的散点图,英特尔将其称为可扩展处理器(Scalable Processor):

标准的Cascade Lake Xeon SP部件有53个,包括Platinum系列的中型和大型内存变体,其中不包括英特尔仍在为企业、HPC、云和超级销售部门的终端用户客户为OEM和ODM生产的定制部件。 正如我们之前所指出的,Skylake和Cascade Lake Xeon SP处理器实际上有三种不同版本——低核心数(LCC)、高核心数(HCC)和极限核心数(XCC)变体,它们分别有10、18和28个核心。

相比之下,2009年的Nehalem Xeons来自相同的芯片设计,它们都有4个核心,都有8MB的L3缓存,它们的主要区别在于时钟速度,从2.26 GHz到2.93 GHz不等。 由于登纳德缩放比例定律(Dennard Scaling)的结束,时钟速度没有太大变化,在2006年左右开始崩溃。 我们可以想象,由于核心流水线、缓存结构和其他调整的变化,整数工作负载的每个时钟周期所执行的指令数(IPC)在Nehalem和Skylake代之间增加了41%,并且考虑到Cascade Lake core是Skylake设计的衍生产品,具有针对Spectre/Meltdown的安全措施,调整向量引擎以运行用于机器学习推理的8位整数指令(INT8),以及允许Optane PMM内存在系统上运行的更改,我们不认为英特尔已经改变了通过从Skylake迁移到Cascade Lake的核心算术逻辑单元(ALU)运行的整数工作的IPC。 这就是英特尔从2009年的4核Nehalem处理器转向2011年的6核Westmere处理器时所发生的情况。 但英特尔确实把核心计数、时钟速度、温度和价格混在了一起,从Westmere Xeons开始,这个过程一直在扩大Xeon产品线中SKU的数量。

英特尔一直在逐步提高每个插槽的内存带宽,方法是通过向系统中添加更快的DDR3和DDR4内存,以及增加每个插槽的内存控制器,就像其他芯片制造商一直在做的那样。

Nehalem Xeons在芯片上集成了一个内存控制器(在此之前,AMD在Opterons上也是这样做的),支持两个或三个DIMM用于双插槽服务器。 对于Westmere Xeons,双插槽机器具有相同的内存控制器,但在四插槽的变体中,内存控制器可以在每个插槽上驱动四个内存插槽。 对于Sandy Bridge Xeons,四插槽机器和一些双插槽机器在集成在芯片上的单个控制器上有四个内存插槽,而另一些则有三个内存插槽,这种内存方案仍然适用于后续的“Ivy Bridge” Xeons(2013年),但英特尔将芯片上12个内核的环形互连增加了一倍,因此每个芯片的内存控制器翻了一倍(每个内存控制器有两个通道)。 在2014年的“Haswell”Xeons中,更多的核心挂在连接芯片上的核心和缓存的一对环路上,但内存控制器和存储通道的数量与Ivy Bridge相同; 内存速度略有加快。 随着2016年的“Broadwell”Xeons的推出,环路再次变大,但内存保持在两个控制器和每个控制器两个通道,总共四个通道,每个通道可选择三个DDR4 DIMM,运行频率为1.6GHz; 或两个每个通道的DIMM以2.4GHz的较高时钟速度运行。 凭借2017年的Skylake Xeon SP,英特尔在芯片上的网状互连中有两个DDR4内存控制器,每个都有三个通道,客户可以以高达2.67 GHz的频率运行内存,理论上这对Xeon处理器来说应该是一个很大的内存带宽提升,但每个通道只有两个DIMM,而Broadwell最多有三个DIMM。 这一代的所有其他芯片——IBM Power 9、AMD Epyc和Marvell ThunderX 2——每个插槽有8个DDR4内存通道,因此在相同的内存速度下,Broadwells和Skylakes的带宽优势为33%。

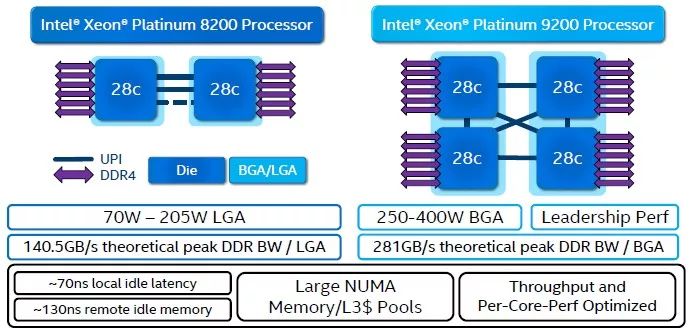

随着Cascade Lake Xeon SP芯片刚刚推出,英特尔对于库存芯片仍然使用每插槽6个内存通道,但在双倍Cascade Lake-AP中,它将两个完整的Cascade Lake芯片塞到同一个BGA表面贴装封装上(像一个巨大的嵌入式芯片,而不是用于服务器处理器的更标准的LGA插槽)。 通过这样做,英特尔可以把它放入插槽的内容加倍,但每个人都知道,双插槽服务器实际上是一个时髦的四插槽服务器。

如果在不必重新调整整个芯片布局和插槽设计的情况下为插槽添加更多电源引脚并不困难,那么英特尔就会在Skylake或Cascade Lake代际中添加更多或更强大的内存控制器,似乎我们必须等到Ice Lake这一代才能看到这一点。 人们期待的是一对内存控制器,每个插槽可提供8个通道,每个通道最多可提供两个DIMM,但英特尔尚未对Ice Lake提供任何承诺。 据我们所知,在2020年之前,没有人会比这做得更好,但如果所有人都不增加更多内存,那么内存与核心比率将会失控。 这就是为什么英特尔一直寄希望于使用3DXPoint内存扩展每个DIMM的内存容量,这可以从目前使用昂贵的128 GB DDR 4 DIMM(最高768 GB)内存通过Cascade Lake Xeon SP插槽提升到L内存扩展的Platinum 版本处理器的4.5 TB。 这种FAT配置使用DDR 4和OPTAN PMM内存的混合。 顺便说一下,该配置使用了四个128 GB的DDR 4 DIMM和8个512 GB的光学PMMS。

扩展和更精细的粒度矢量引擎

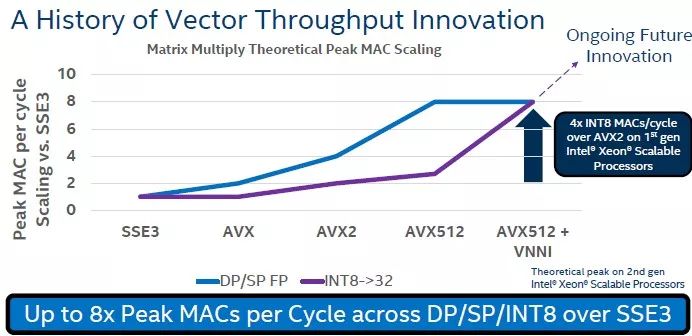

由于受到GPU的威胁,以及在较小程度上采用卸载方式的FPGA加速,英特尔受到传统HPC空间以及从Westmere产品线开始的超大规模用户和云建设者空间的威胁,英特尔的回应是通过连续的Xeon代际增加更强大的浮点能力。

过去十年,英特尔一直致力于在Xeon产品线上扩展单精度和双精度浮点运算。 Steiner承认,英特尔对增强这些矢量单元的整数运算能力并不十分感兴趣——直到机器学习训练算法的兴起,随着时间的推移,这些算法正在使用越来越小的INT数据格式。

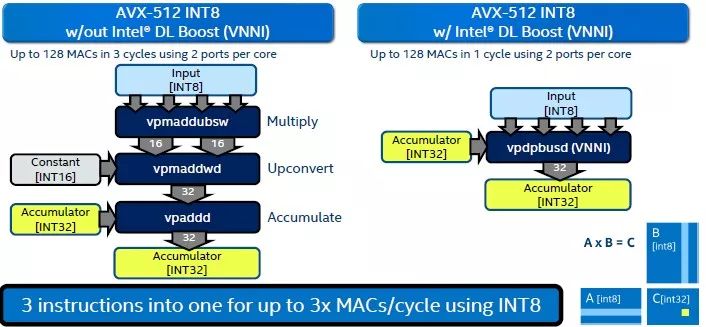

Haswell Xeons在其AVX 2矢量单元中有INT的运算支持,但乘法累加(MAC)操作不是焦点,因为8位INT 8格式的动态范围很小,只有256个数值,而单精度FP32格式表示的是2128个可能的数值。 但是,INT 8的精度和动态范围(有些人甚至会认为INT 4)对于某些机器学习训练推理例程来说已经足够了,因此英特尔将其添加到Cascade Lake Xeon SP处理器中的AVX-512矢量引擎中。 我们进入了矢量神经网络指令(VNNI)的架构,有时称为深度学习增强(DL Boost),它于2018年8月随Cascade Lake首次亮相,但下图更好地概括了它:

利用Skylake架构,对8位整数进行矩阵乘法,并将它们累加到32位整数寄存器中(这是为了避免因8位数字范围有限而导致溢出,FP16或FP32由于这些数据格式的动态范围很大而很容易处理)。 这在过去需要三个步骤,现在Cascade Lake只需要一步,完整的AVX-512单元(意味着两个端口都被激活)可以在每个时钟周期完成128个这样的步骤。 这比ALU中的整数单元(每次64位)所能处理的多很多。

Steiner表示: “实际工作负载可能无法通过DL Boost获得3倍的性能,但这没关系。 我们的目标并不是要在所有方面最大化TOPS峰值。 我们正在尝试将正确的基元构建到硬件中,以便更复杂的软件能够获得尽可能多的性能提升。 这就是我们追求的很多‘2X’的地方。 ”

这意味着在矢量整数格式上获得类似的扩展,就像过去十年矢量浮点格式发生的情况一样,下面是一张简易的图表,展示了随着时间的推移,Xeon系列的SIMD引擎中的浮点和整数在架构上的飞跃:

虽然客户并不像过去那样痴迷于功耗,但设计Cascade Lake的团队仍然关注当前常用的各种推理基准测试中功耗和性能的相互作用,这张图表展示了DL Boost是如何在Skylake Xeons中使用FP32和传统INT 8方法实现的:

根据Steiner的说法,在Skylake Xeon SP芯片上,从FP32到INT 8,每个时钟周期峰值Mac的性能提高了大约33%,而且由于数据量较小,处理器的缓存和内存带宽压力也有所缓解。 与FP32相比,Skylake上的INT8计算效率更高。 现在,从Skylake芯片中的传统INT8转移到Cascade Lake芯片中的DL Boost指令导致每个时钟周期峰值MAC增加3倍,并且对缓存或内存带宽没有影响(数据格式相同,处理器上的缓存层次结构相同),此外INT8操作的功率效率再一次得到了提升。

这是一般性陈述,但如果使用真正的推理工作负载,对照的结果则是下图的样子:

如图所示,传统的INT8方法使用的功率要低得多,性能也有所提升,但是DL Boost的重点是用相同的功率提供更高的吞吐量,就像在FP32模式中进行相同的推理一样。 可能还有其他工作负载可以使用此INT 8及其配套的INT 16功能,但到目前为止还没有出现。 但是现在硬件已经在这里了,也许有人会想出聪明的方法来使用它。

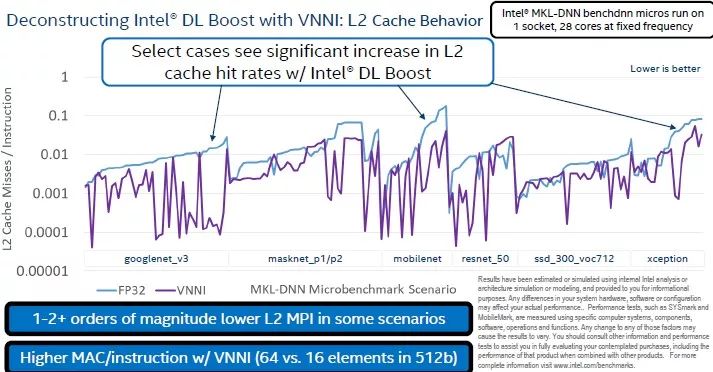

如下图所示,与FP32相比,使用DL Boost时L2缓存的性能要好得多:

也许同样重要的是,当运行推理工作负载时,系统的内存带宽压力从FP32转移到DL Boost:

这又回到了超大规模用户和高频交易商以及超级计算机客户甚至在他们告诉系统制造商很长一段时间之前的老生常谈的观点: 在实际工作负载上,可预测的延迟和一致的性能比某些理论工作负载上的一些峰值吞吐量重要得多。

-

- 半导体行业观察

-

- 摩尔芯闻