IMEC计划革命传统SoC

在全球记忆体不振的冲击下,近来半导体市场需求疲软,2019 年全球半导体市场销售随之下跌7.2%,不过在一片低迷的IC 市场中,一些新兴的晶圆、芯片、电机体层叠技术,将为芯片市场带来创新发展。

于比利时安特卫普(ANTWERP) 举行的Imec 年度技术论坛(Imec Technology Forum,ITF) 上,提出此项将传统SoC 系统整合芯片(System on a Chip) 进行彻底改造的技术,不过未来在元件校准和冷却方面,将会是挑战,

全新改版的SoC 芯片值得一提的是,此新版SoC 可望能将功率耗散(thermals) 达到500W 以上。

Imec 将这种彻底改版的SoC 结构称为「序列3D」 (sequential 3D) ,能够替各种不同的电源、逻辑芯片和记忆体电路板,提供优化升级与设计。

其中一版本,是将电力传递电路,置放于已切薄至几百纳米厚度的晶圆片背后,以微小的矽穿孔(through-silicon vias) 进行连结。

Through-Silicon Vias,又称TSV,是一种让3D IC 封装遵循摩尔定律的互连技术,TSV 可堆叠多片芯片,其设计概念来自于印刷电路板(PCB), 在芯片钻出小洞,从底部填充入金属, 矽晶圆上以蚀刻或雷射方式钻孔(Via),再以导电材料如铜、多晶矽、钨等物质填满。

另一大胆的版本是将SRAM 快取记忆体,置放于搭载晶圆的核心电路上方,再以铜接合(copper-to-copper bonding)。

而最后的「序列3D」将会是一个三明治结构:SRAM 阵列在最底部、电源电路在最上方,核心逻辑夹在中间

如此一来,能将SRAM 最大化,同时又能降低成本。

此一技术替整合各种元件,开启了更多可能性,尽管Imec 一开始打造的5 纳米制程示范,并不包含任何主动结构。

Imec 逻辑制程微缩专案总监Julien Ryckaert 说道:「这开启了一个新的领域,将有许多创新的技术蓝图出现,所以摩尔定律还能继续实现」

不过在迈向1 至2 纳米节点的过程中,工程师会需要换掉铜与钴,很可能会改用钌(ruthenium),这种材料能让晶圆设计师将目前用以避免金属扩散至矽氧化层的金属屏障薄化。

除了芯片制程,研究人员也讨论了一些封装技术,例如Imec 正在研发英特尔(Intel) 嵌入式多芯片互连桥接技术(EMIB) 的「廉价版」,也就是将桥接基板整合至封装中。其他技术选项包括利用数百微米、数十纳米尺寸的互连。

晶圆片、裸晶与晶体管封装选项涵盖很多微米到几纳米的范围。

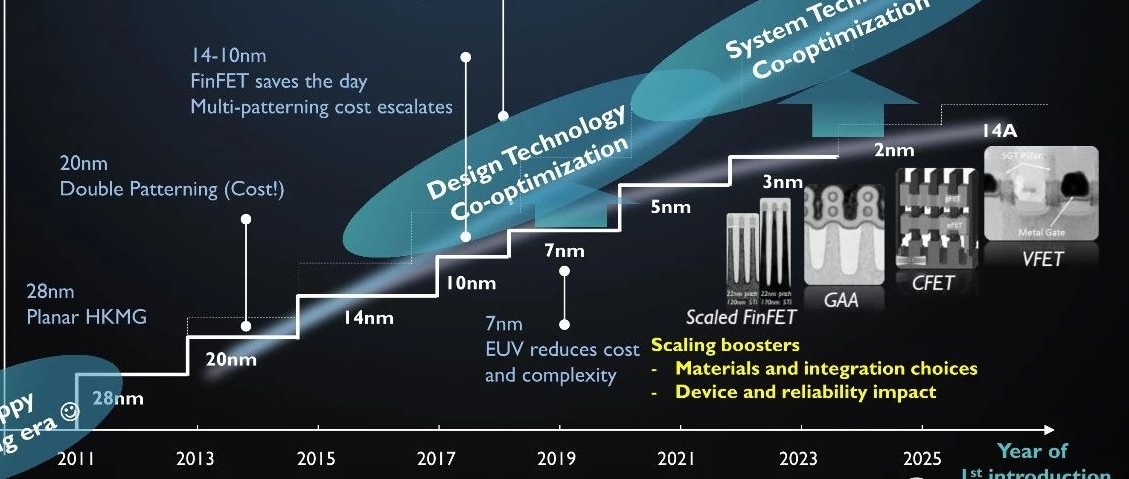

(图片: EE Times)

负责3D 芯片专案的Imec 研究院士Eric Beyne 表示,其封装技术蓝图仍面临一些设备功能上的差距,由于密集的芯片层叠,会产生大量功率耗散元件,目前还在开发液态冷却方法,而且支援完整签核功能的EDA 工具也还没到位。

「但我们已经看到不错的进展。」Beyne 说道。

新旧技术整合

就像英特尔技术长Mike Mayberry 在专题演讲里提到,芯片技术的各种创新和改革,象征着传统半导体正在演化而非终结。

旧的处理器将会与新一代加速器针对特定领域共存,像是微软(Microsoft) 资料中心利用x86 处理器与FPGA 的整合方案。

目前分析师看好2019 下半年,半导体市场将有强劲发展。虽然当前半导体销售额下滑,不过IC 市场的创新暗示着市场仍有发展潜力。

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 培风图南:手握3D TCAD利器,剑指虚拟晶圆厂

- 2 芯启源与浙江大学集成电路学院签署战略合作协议 共启数智“芯”征程

- 3 罗姆与芯驰科技联合开发出车载SoC参考设计, 配备罗姆的PMIC和SerDes IC等产品,助力智能座舱普及!

- 4 华强电子网携手腾讯企点重磅发布电子行业解决方案——芯采通