EDA究竟难在哪里?

因为美国对华为禁运,国内掀起了一股集成电路产业科普。很多之前甚至连听都没听过集成电路这个词的群众开始对这个本来相对低调的行业产生了巨大兴趣,EDA就是当中重要的一环。为了让大家对全球EDA和本土EDA产业有深入的了解,我们转载了“芯思想”公众号署名为“邱志雄”的文章,让大家对这个行业有更深入的了解。

以下为文章正文:

三大EDA公司主要有哪些软件产品?为什么芯片设计行业无法脱离EDA工具?

不知道是否还有人记得这张照片,2017年3月3日,在小米5C手机和小米自主SoC芯片澎湃S1的发布会结束时,雷军公布了这张致谢图。图中红色框的即是EDA领域的三大巨头:Synopsys、Cadence、Mentor,绿色框是我们国产EDA公司华大九天。印象中,这是EDA公司第一次出现在消费类电子产品的发布现场。

三巨头几乎都可以提供芯片设计全流程工具,但是Synopsys的优势在于数字芯片和FPAG逻辑综合相关工具,其逻辑综合工具DesignCompiler、静态时序分析工具PrimeTime、调试工具Verdi在业界具有近乎垄断性的地位,2019年6月Synopsys在SNUG2019也推出了更为先进的工具;Cadence在模拟IC全流程工具方面具有绝对优势,而且近几年旗下的数字布局布线工具Innovus攻城略地,获得了非常好的市场份额;Mentor目前已经被德国西门子收购,虽然在全流程方面相对较弱,但是Calibre signoff和DFT方面一骑绝尘。

芯片设计是一个准入门槛极高的领域,对产品可靠性和历史口碑要求到极其苛刻,在虚拟仿真阶段任何微小错误都有可能造成芯片流片失败,流片失败则意味着数年的工作毁于一旦,公司面临市场失守的悲惨境地。因此,在芯片设计领域,全球几乎没有任何一家EDA公司有和三大巨头掰手腕的实力。在EDA领域,创业最成功的结局就是被上述三大巨头收购。

因此,三大巨头的EDA工具几乎是Fabless公司的唯一选择。

EDA工具的研究难在哪里?

如前所述,芯片设计环节繁多、精细且复杂,EDA工具在其中承载了极为重要作用:①将复杂物理问题用数学模型高度精确化表述,在虚拟软件中重现芯片制造过程中的各种物理效应和问题;②在确保逻辑功能正确的前提下,利用数学工具解决多目标多约束的最优化问题,求得特定半导体工艺条件下,性能、功耗、面积、电气特性、成本等的最优解;③验证模型一致性问题,确保芯片在多个设计环节的迭代中逻辑功能一致。

(1)先进工艺节点:“晶圆厂+Fabless+EDA”协同推进的成果

首先,SOI、FinFET等新器件结构的发明将带来晶体管电学和物理特性的变革;其次,在半导体工艺制造方面,摩尔定律的演进伴随着众多不可预知的物理问题逐渐浮现。处于摩尔定律推进一线的晶圆厂从材料、化学、工艺过程控制等各种制造细节来创新、调试和求证。而EDA公司借助晶圆厂积累的大量测试数据探索物理效应和工艺实施细节的准确和高精度模型化。然而,这并不意味着新工艺节点研发的终点,顶尖Fabless公司将基于此模型和工具进行芯片设计与试产,并且依托强大和丰富的芯片设计不断发现和排除新工艺节点在模型和制造中的各种量产问题。在此期间,芯片设计工程师、EDA公司的AE、晶圆厂工程师等等往往长年累月在一起办公,集中攻破新问题,修复新bug。晶圆厂、Fabless、EDA三者通力合作,反复迭代,如此才能最终将达到商用和量产要求的工艺节点推向市场。一旦有一个环节出题,前功尽弃。

因此,摩尔定律任何一代最先进工艺节点,无一不是由拥有最先进工艺制造条件的晶圆厂、顶尖EDA团队和设计经验丰富的Fabless公司三者协力共同推进的成果。这也是为什么台积电最先进制程的第一批产品总是由苹果、高通、华为来发布,只有顶尖的Fabless公司才具备参与调试最先进工艺节点的能力。这也是为什么三大EDA巨头始终把控细分市场的一个重要的原因。

(2)数学问题

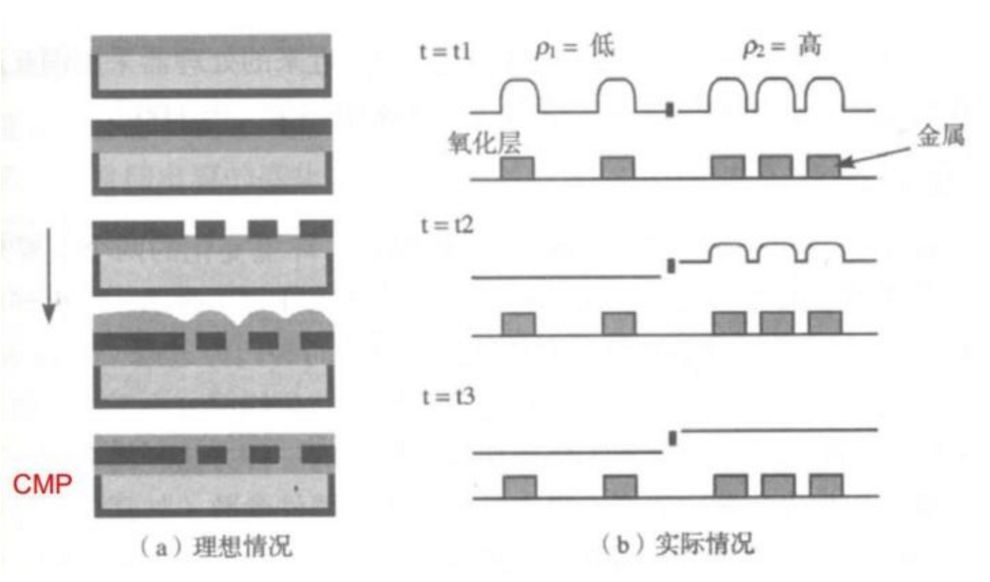

以一个铝互连时代工艺过程中经典的互连线偏差问题为例,在形成铝互连线时二氧化硅层夹在互连图形的金属层之间,氧化物淀积在已经成形的金属层上,一般都会留下一些台阶高度或者表面形貌,在理想情况下,采用CMP方法对层间电介质进行厚度剖平后如图a所示。

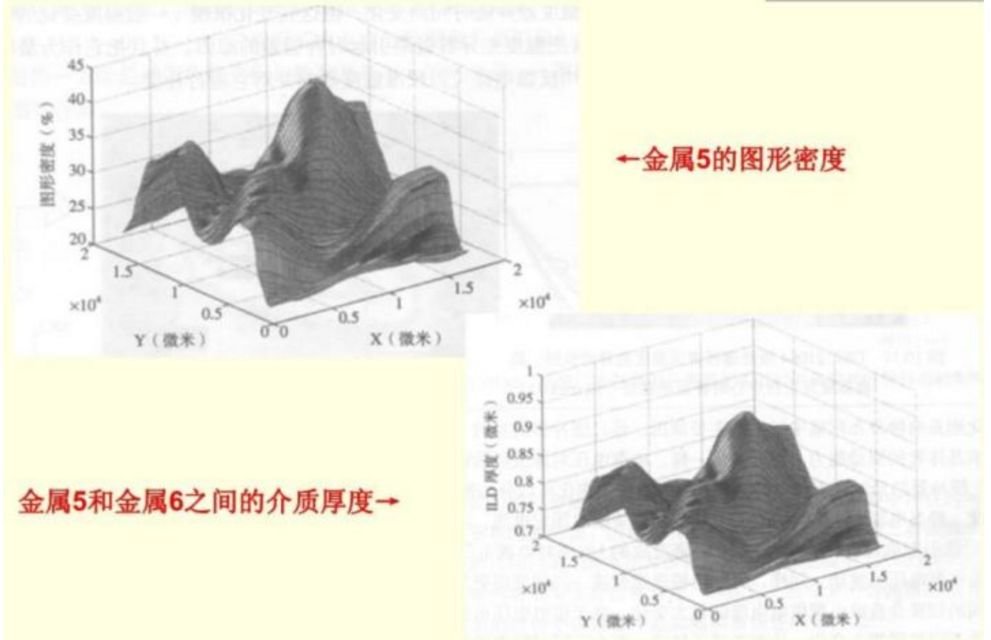

但实际的情况是,虽然在特定范围内能够达到很高的平整度,但从整个芯片范围上来讲平整度就很有限,如图所示,不同的厚度又对电介质的电容等电特性产生不同的影响。

EDA工具要做的事就是尽可能高精度地在虚拟的软件世界中重新和拟合类似上述现实中的物理和工艺问题,以期望在芯片设计阶段将其纳入考虑范围之内,以系统性的方法和预测性的裕量来应对和纠正,最终保证芯片设计仿真结果同流片结果一致。

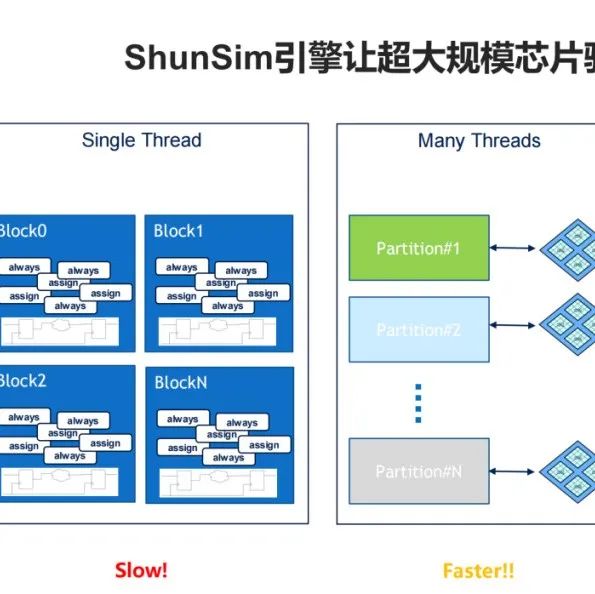

同时,EDA工具需要对数千种情境进行快速设计探索,以求得性能、功耗、面积、成本等芯片物理指标和经济指标的平衡。随着集成电路制造工艺进入7nm以下,数字芯片中标准单元数量已经达到亿数量级,EDA算法已经成为典型的数据密集型计算的典型代表。且现有布局布线方法大都采用组合优化算法,可接受的计算时间内,不一定能得到局部最优解,甚至有可能得到一个劣解,算法复杂度较高。以上两点导致EDA算法的计算时间非常冗长,以小时计。

以一个简单的布线算法示意图为例,以下动图为EDA工具在寻求源点和终点之间的金属走线方案。试想一下,芯片内部单元以亿级数量计,内部布线金属层多达数层,如何从一个点在只能走直线和90度拐弯的限定下,经过各种不可布线的障碍并不断做出前行的抉择,穿过层层金属,最终准备到达芯片中的另一个点,期间探索方案的计算空间需求巨大,且整体还要满足时序和总线长最小的目标,并必须考虑上文所述的工艺偏差。

(3)半导体、数学、芯片设计三者交叉学科人才培养问题。

EDA算法问题起点和终点是半导体工艺等物理问题,解决工具是数学问题,应用对象是芯片设计实现具体问题。一般来说本科生很难如此既宽泛又具体的知识储备和体系,因此,三大EDA巨头公司研发工程师的平均学历都很高。同时,在硕士和博士阶段,单独从事数学、芯片设计、半导体器件和工艺的人较多,但是三者兼具的人又非常少。

我国当前仅有清华大学、复旦大学、浙江大学、北京航空航天大学、电子科技大学、西安电子科技大学、福州大学等少数学校从事EDA方向的研究和人才培养。尤其是清华大学计算机系在1970年代就开始相关研究,为我国国产熊猫EDA工具(华大前身)、华大九天EDA工具的研发做出了很大的贡献,而且培养了大量的EDA算法人才。

值得欣喜的是,国内EDA的研发力量近几年也有长足的进步。2017年6月在集成电路计算机辅助设计领域的旗舰会议--第54届设计自动会议(ACM/IEEE Design Automation Conference 2017)上,福州大学陈建利老师的论文Toward Optimal Legalization for Mixed-Cell-Height Circuit Designs获得最佳论文奖(作者:Jianli Chen, Ziran Zhu, Wenxing Zhu, Yao-wen Chang)。这是54年来中国大陆作者第一次以第一单位/第一作者获得该会议最佳论文奖。

国产EDA公司的机遇

如本文在第一节所述,国产EDA工具目前还主要以点工具为主,只有华大九天有模拟IC设计的全流程工具。但是,也不乏亮点。在过去的几年,华大九天的Xtime物理设计时序优化与Sign-off工具和解决方案,得到了业界一线工程师的一致好评,已经成功打入全球一流芯片设计公司中,成为数字全流程中的重要一环。而且,华大九天是全球是全球唯一可提供液晶平板显示全流程EDA设计解决方案的提供商,国内市场占有率超过90%。

此困境之下,国产EDA工具将进入国内Fabless的视野,取得扩大市场份额的契机,进而获得与拥有先进制程的晶圆厂合作机会,国产EDA元年或将就此开启。

作者简介:

邸志雄,博士,硕士研究生导师,西南交通大学信息学院电子工程系副系主任。CCF会员、中国图象图形学学会军民融合专委会成员、新工科联盟“可定制计算”专委会成员。研究方向为高性能图像编解码芯片技术研究、AI布局布线算法研究。近年来主持国家自然科学基金青年项目、四川省科技厅项高新重点项目等项目,参与完成了我国自主研制的首颗宇航级高速图像压缩芯片“雅芯-天图”。指导硕士生和本科生多次获得全国研电赛集成电路专项赛、全国大学生集成电路创新创业大赛国家级奖项。

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 象帝先计算技术与鸿合科技在第83届中国教育装备展示会上举行战略签约

- 2 从芯来到“香山”,芯华章助力国产RISC-V生态做了哪些事?

- 3 四年17颗芯片,思特威实现CIS高端手机应用突围

- 4 Arm发布新一代NPU,助力边缘AI腾飞