[原创] 英特尔揭开了他们先进封装的神秘面纱

英特尔之前推出了其用于创建三维芯片封装和其他将多个芯片组合在一起的解决方案的封装创新方案,但并没有披露太多细节。 在日前于旧金山举行的Semicon West会议上,英特尔分享了其最新封装技术的更多细节。

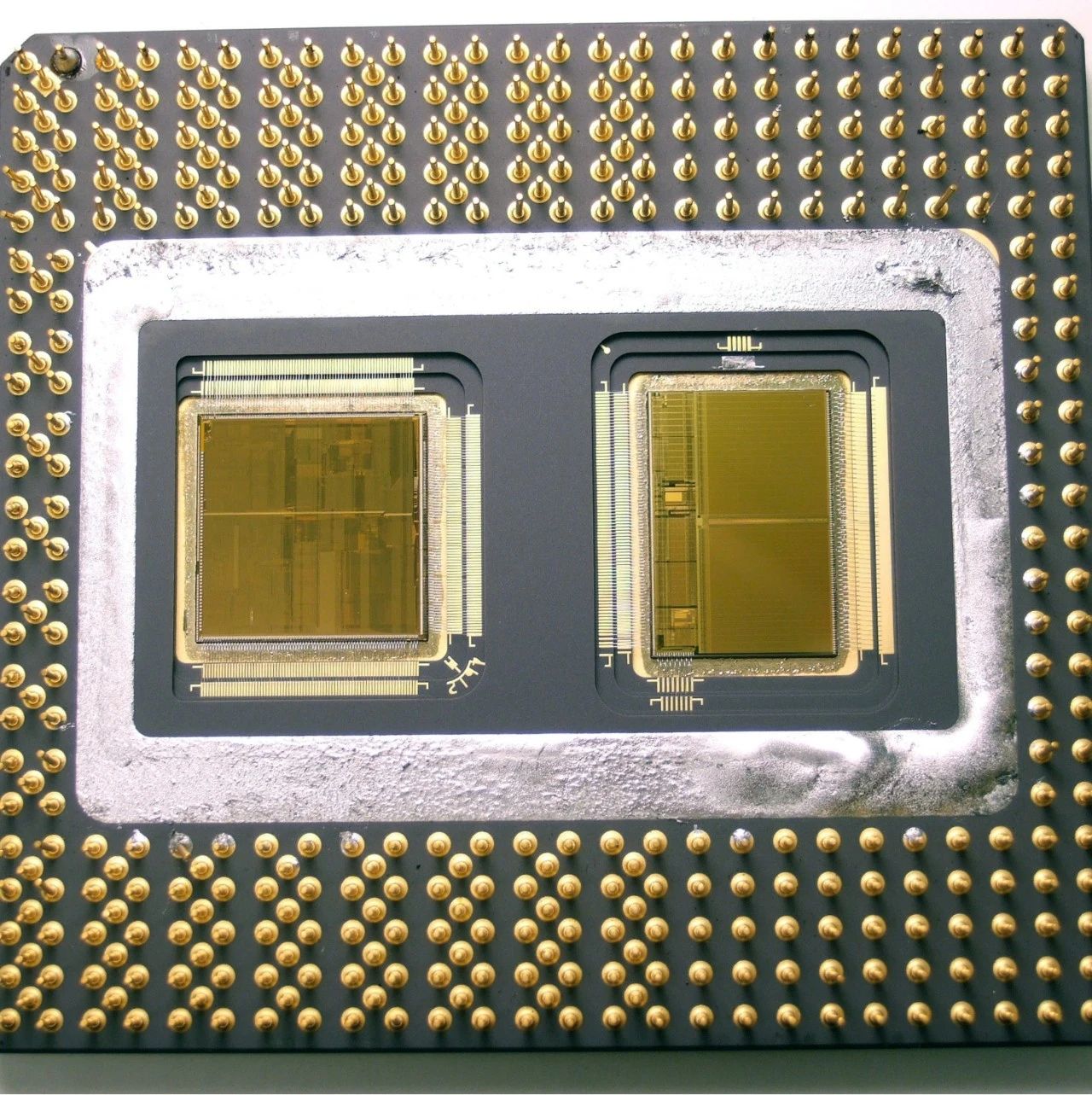

英特尔表示,芯片封装在电子供应链中一直扮演着至关重要的角色。 作为处理器和主板之间的物理接口,封装为芯片的电信号和电源提供着陆区。 随着电子行业向数据中心转型,先进封装将发挥比以往更大的作用。

封装不仅仅是制造过程的最后一步,它正在成为产品创新的催化剂。 先进的封装技术允许跨多种工艺技术集成各种计算引擎,其性能参数类似于单个芯片,但其平台范围远远超过单芯片集成的芯片尺寸限制。 英特尔表示,这些技术将提高产品级性能,功耗和面积,同时能够全面重新思考系统架构。

第一个披露是英特尔称之为EMI-EMIB。

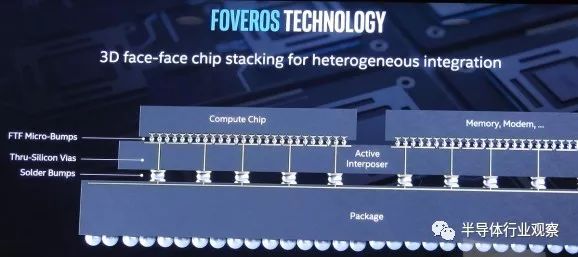

据Intel介绍,Co-EMIB汇集了EMIB和Foveros技术,该技术已经被应用到的产品包括英特尔Stratix 10现场可编程门阵列(FPGA)和带有Radeon Graphics的第8代英特尔酷睿处理器,以及即将推出的Lakefield 10纳米混合CPU架构。

intel方面指出,嵌入式多芯片互连桥(EMIB)可以连接两个或多个Foveros(3D堆叠芯片)元件,从而创建一个基本上作为单个芯片运行的芯片组。 这些Foveros元件还可以连接到具有非常高带宽和非常低低功耗的模拟,存储器和其他器件。 这使得co-EMIB封装技术成为大模具高性能应用的理想选择,否则这些应用可能受到掩模版尺寸的限制。

英特尔还展示了全向互连(Omni-Directional Interconnec: 简称ODI)技术的预览。 作为EMI-EMIB之后的下一步,ODI将汇集最好的EMIB和Foveros,以及额外的技术创新,为封装中的芯片之间的通信提供更大的灵活性。

简而言之,堆栈中的顶部芯片可以与其他小芯片(chiplet)水平通信,类似于EMIB。 它也可以通过下面基模中的TSV连接垂直通信,类似于Foveros。 另外,ODI利用大的垂直通孔( large vias)以允许直接从封装衬底向顶部管芯供电。

据介绍,大通孔( large vias)比传统TSV大得多,且具有较低的电阻。 Intel表示,它可为高性能数据中心工作负载(如AI和超级计算)提供更强大的功率传输,更高的带宽和更低的延迟。 英特尔表示,他们是业界第一个开发这种封装技术并开始准备将其纳入制造流程的公司。

最后,英特尔还分享了有关称为管理数据输入/输出(Management Data Input/Output,简称MDIO)的新型芯片到芯片接口的更多细节,这是一种控制芯片之间接口的PHY级通信协议。 该公司表示,MDIO可提供更高的电源效率,并能将其当前的高级接口总线技术提供的引脚速度和带宽密度提高一倍以上,这个技术计划在2020年实现可用性。

“我们的愿景是开发领先技术,将芯片和芯片连接在一个封装中,以匹配单片片上系统的功能,”英特尔公司测试和装配技术开发副总裁Babak Sabi在一份声明中表示。 “异构方法为我们的芯片架构师提供了前所未有的灵活性,他们可以将IP模块、工艺技术与新设备外形中的各种存储器和I / O元件进行混合和匹配。 英特尔的垂直整合结构在异构集成时代提供了优势,为我们提供了无与伦比的共同优化架构,流程和封装的能力,这可以支撑我们持续提供领先的产品。 ”

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 澜起科技率先试产DDR5时钟驱动器(CKD)芯片

- 2 UWB"上车"加速,国产芯片大有可为

- 3 BEYOND Expo 2024国际芯片及应用产品展将于5月23日在澳门拉开帷幕

- 4 见格局、见匠心,紫光国微开启第二增长曲线