破解卡脖子新思路,CCF容错大会发布OpenBELT开源EDA倡议

8月15日-17日,由中国计算机学会(CCF)主办、中国计算机学会容错计算专业委员会、清华大学和北京启迪清云智慧能源有限公司共同承办的CCF CFTC 2019在北京九华山庄隆重召开。

本次大会主题是“容错护航硬科技发展”,就芯片、软件、系统等领域的硬科技技术进行了广泛、深入的学术交流,吸引了来自学术界和工业界500余人参加了本次大会。 在本次大会上,讨论了诸多集成电路领域的热门话题,像芯片安全、开源EDA和开源IP、存储容错和存储计算等,最为有兴趣的是北京大学罗国杰博士介绍的关于开源EDA方面的工作。

在8月14日的大会特邀报告上,宣布了由国内自主发起的一个开源EDA框架——OpenBelt倡议,倡议者、北京大学高能效计算与应用中心(CEDA)的罗国杰副教授在大会的特邀报告中详细介绍了OpenBelt的设计动机和思路。 OpenBelt是由北京大学、中科院计算所、清华大学、复旦大学等EDA领域研究优势单位合作发起的一个开源EDA框架,目的是通过联合国内在EDA领域的学术界和工业界力量,构建自主、创新、满足后摩尔时代芯片设计的新型设计方法学生态和社区。

OpenBelt开源EDA框架

罗国杰博士“OpenBELT: 开源 EDA 端到端框架的设想”大会报告

罗博士的大会报告首先从开发技术领先、成熟EDA需要的人才开始。 参考EDA巨头的研发投入,Synopsys和Cadence两家公司在2018年度的研发费用均已达60至70多亿人民币,每年至少需要3000名研发工程师才能达到和巨头们类似的创新研发能力。 然而,目前国内EDA领域的人才培养还相当滞后,数量严重不足。 罗博士在报告中做了初步估算: 假设国内学生在EDA领域顶级期刊IEEE TCAD的投稿中占比六分之一,也就是每年约30篇,再假设博士生在校时每五年需要发3篇论文,则估算出国内EDA领域的在校博士生只有约50名。 这和人力需求相比,还有很大的差距。 一方面,如何高效培养EDA领域人才来弥补这一巨大的差距是一个亟待解决的问题。 同时,也说明我们要在现有技术基础上,开发和当前领先的EDA工具相似水平的工具,首先要解决人才储备不足的问题。

图: Cadence和Synopsys的年度研发费用(CDNS: Cadence,SNPS: Synopsys)

参考互联网和人工智能领域近年的进展,开源技术及社区促进了开发人员和领域技术的快速增长。 现在最流行的深度学习库,很多都实现了开源。 通用开发者社区Stack Overflow,GitHub提供了非常多的代码以及问题解决方案,非正式的技术讨论平台arxiv和quora也会分享一些初步研究成果和观点。 开源技术和社区降低了领域的门槛,使得更多领域外的研究者可以接触到更前沿、更具体的问题及其解决方案,也可以做出一定贡献,推动领域的发展。

罗博士的报告接着分析了设计开源端到端EDA工具链的重要意义。 EDA开发者教育和培训的规模化、以开放的社区消除专业技术交流壁垒、以端到端的开源工具链吸纳社会资源,其中通过定制芯片开发来吸收自然科学和工程探索领域的部分政府经费、通过便利技术需求的表达与技术成果的评测交付来吸收校企合作经费、以降低小团队独立创业和生存的难度来吸收风险投资。

当然,与传统软件不同,开源EDA有其自身的难度。 EDA 技能跨越算法层面和物理层面涉及众多复杂专业知识、开发完整的EDA工具链需要众多社区开发者的支持与维护、以及运行大规模设计的EDA工具的需要大量的高性能服务器。

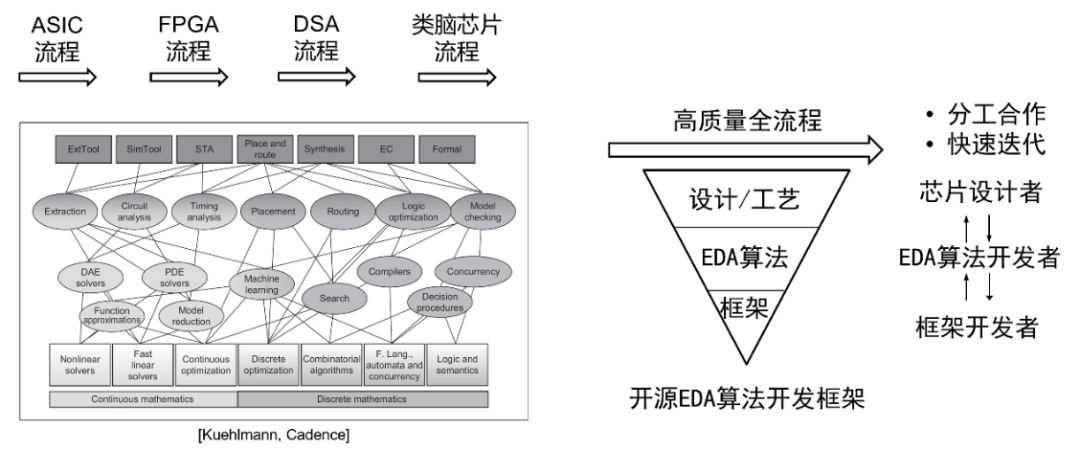

在整个EDA领域的开发过程中,软件复杂度问题可以通过智能、层次化和功能重用解决。 一套完整的EDA开发流程往往可以分为以下几个层次: 具体点工具(如ExtTool、STA、P&R、synthesis等)、专用求解器(如DAE solvers、PDE solvers、Machine learning、Compilers等)、通用求解器(如Nonlinear solvers、Fast linear solvers、Discrete optimization等)、以及数学模型(连续数学和离散数学)。 如果能够通过层次化和功能重用搭建起一套高质量全流程的开源EDA算法框架,便可以针对ASIC流程、FPGA流程、定制体系结构流程、类脑芯片流程等诸多目标,在芯片设计者、EDA算法开发者、框架开发者间建立起一套能够快速迭代、分工明确的合作体系,合力解决复杂而繁琐的EDA问题。

图: 开源EDA算法开发框架

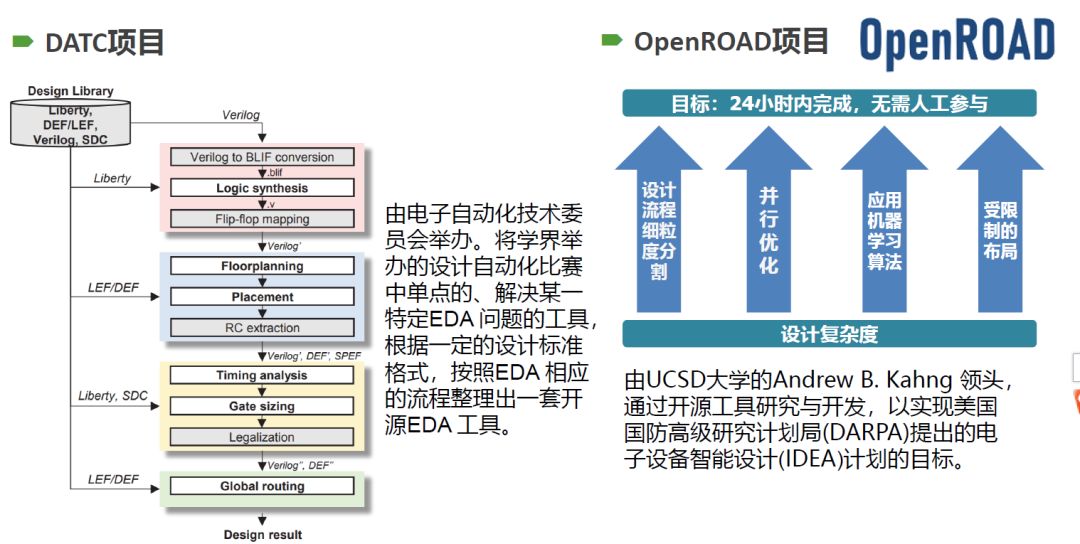

目前国外已经提出了一些开源EDA的框架与项目。 其中,IEEE CEDA提出了DATC项目,将学术界举办的设计自动化比赛中的单点工具,根据一定的设计标准格式,整理出一套开源EDA流程; 由美国国防高级研究计划局DARPA资助的OpenROAD项目,通过开源EDA工具研究与开发,以实现电子设备智能设计IDEA计划的目标,即24小时内无人参与完成芯片设计。 同时,DARPA电子复兴计划的一系列与开源硬件和EDA相关的计划,如开源硬件项目POSH、IP重用项目CHIPS、领域专用芯片项目DSSOC、以及软件定义硬件项目SDH等也与设计方法学创新密切相关。

图: 国外的开源EDA项目

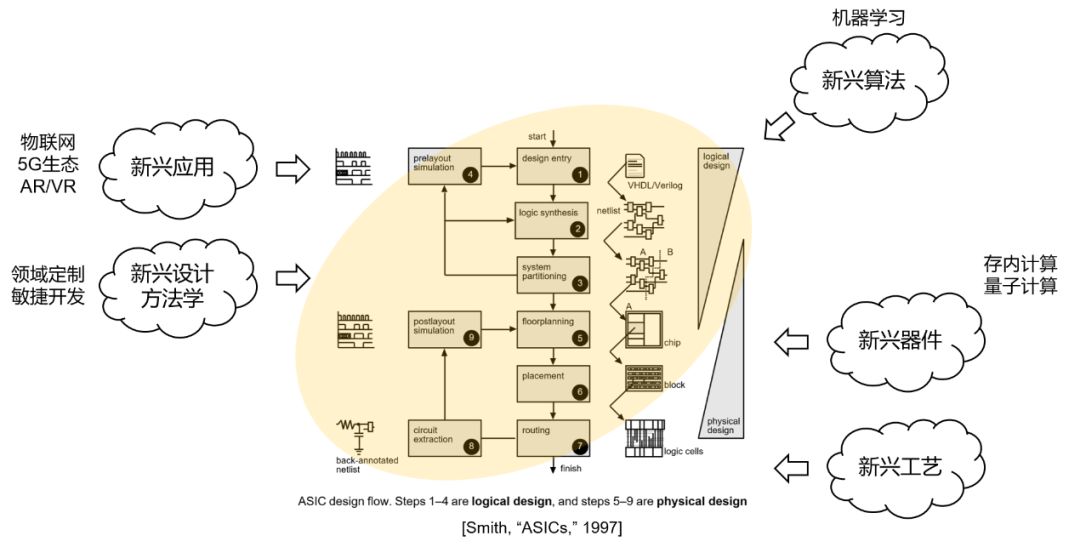

为了吸引更多的开发者加入EDA领域,EDA需要和其它新兴领域相结合,这主要包括三个方面。 一是和EDA领域的上游相结合,近年来新兴器件带来了许多特殊的EDA需求,如存内计算、量子计算等,传统的EDA流程不再适用,这就需要开发者们针对它们设计新的流程。 二是和EDA领域的下游相结合,近年来有许多新兴应用,如物联网、5G、AR/VR等,对性能和功耗有了更高的要求,通用的EDA流程无法满足,开发者们需要针对应用设计新的流程; 此外,EDA的设计过程和设计目标也需要根据新兴算法作出调整,机器学习算法就是一个很好的例子。 三是和EDA自身发展相结合,新兴的设计方法学,如敏捷开发,会帮助改进EDA领域开流程。

图: 开源EDA的新需求

罗博士最后表达了OpenBelt作为公共领域设想而不是具体项目,需要凝聚学界和业界的广泛力量来解决的问题。 期望框架能高效实现的算法和代码重用、点工具与流程的版本管理、分布式和云平台支持等功能。 目前,北京大学高能效计算与应用中心正在开展OpenBelt初步框架的搭建工作。

为了更进一步深入探讨开源EDA和开源IP的相关技术,CCF容错大会在16号和17号两天下午,分别组织了专题论坛,邀请了众多学者和业界嘉宾从AI EDA和开源IP等不同角度深入探讨开源EDA的可行性和具体技术路线,嘉宾和观众一直认为开源EDA可以降低EDA领域门槛,可以让学界减少重复性工作,对学术界甚至整个EDA领域发展非常有好处,但是如何激励和推行开源工作仍需要有深入的思路。

CCF容错专委秘书长、一直从事专用处理器芯片研究工作的中科院计算所韩银和研究员,也是OpenBelt的倡议者之一,在论坛中表达了OpenBelt应该和敏捷开发相结合的思路。 开源首要的是可帮助降低成本,但当前芯片设计而言,设计复杂度和设计周期过长,是更为急迫的刚需。 如果说目前这一代的设计方法学(DA)解决了大规模设计的问题,满足了通用计算芯片设计规模更大、运行频率更高等需求; 下一代设计方法学可能需要关注快速设计的问题,也即敏捷开发的问题,满足人机物三元时代专用芯片种类更多、设计周期更短、单片人力投入更少等需求。 OpenBelt框架在设计之初,就可构建在类似Chisel等新的设计语言上,设计开源的中间文件交换格式,这样就可以很好的整合当前算法界和系统界在图计算优化方面的最新成果,设计更快、功能更强的仿真、综合等工具。 同时,通过开源,吸引更多人工智能方面的最新研究进展,使得整个EDA框架更加自动化。 同时,通过设计复用开源IP,可以大幅加速芯片设计的周期,OpenBelt应融合这方便的优势。

开源EDA框架要想成功,需要学术界和产业界的共同努力,非常不容易,CCF容错专委会持续举行活动,推动国内主导的开源EDA框架的尝试。

2019 CCF集成电路Early Career Award揭晓,上海交大蒋力副教授获此殊荣

大会的另一个重头戏是揭晓今年的CCF 集成电路 Early Career Award。 中国计算机学会 CCF 集成电路 Early Career Award 针对工作不超过 6 年的青年学者设立, 为从事集成电路方向的青年学者早期职业生涯提供支持。 这是中国计算机学会体系内目前唯一的一个集成电路专业奖项,去年启动首届评选,今年已是第二年。

经过7名国际国内同行专家的三轮评审,最终,上海交通大学的蒋力副教授获得其项殊荣,以表彰他在后摩尔时代集成电路测试容错设计方面领域所做的学术贡献。

蒋力副教授一直专注于从事集成电路测试和电路容错技术研究,他针对三维芯片高成本问题,率先提出三维芯片“绑定前测试”架构设计与优化方法,被引入IEEE 标准P1838。 针对 3D IC中TSV的高故障率,率先设计了极为高效的TSV 修复架构和三维存储器中相邻晶片上冗余资源共享技术,刷新了三维存储器修复效率的记录。

图: 评奖主席汪玉教授主持蒋力博士的获奖仪式

摩尔精英公司连续两年赞助了CCF 集成电路 Early Career Award。 人才是半导体产业发展的引擎,摩尔精英董事长兼CEO张竞扬表示,能不能持续吸引像蒋力副教授这样的优秀青年加入行业,并充分实现他们的个人价值,对整个产业来说至关重要。 同时,通过一站式芯片服务平台,可以加速研发成果转化,促进产业发展,这也正是摩尔精英成立四年来所做的探索,为1500家芯片公司提供芯片设计服务、流片封测服务、人才服务和企业孵化服务,同时积极探索SiP, Chiplet和EDA/IP上云等创新模式,帮助提升芯片创新的启动率、实现效率和成功率,最终目标是用1/10的资金、1/10的时间和1/10的团队,完成芯片产品研发,投入市场。 摩尔精英的使命是,让中国没有难做的芯片,我们正在不断努力,一步步往这个目标迈进。

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 6月5-7日,南京见!2024南京国际半导体博览会邀您共赴盛会

- 2 一文看懂封装基板

- 3 从芯来到“香山”,芯华章助力国产RISC-V生态做了哪些事?

- 4 Wi-Fi 7射频IP验证系统发布!思尔芯EDA助力Sirius Wireless加速芯片设计