来源:

本文由公众号半导体行业观察(ID:

icbank)翻译自「jbpress」,谢谢。

大多数读者应该知道Intel 的处理器、TSMC生产的SoC(System on Chip)等逻辑半导体的相关工艺,也明白到这些规则只不过对产品的命名罢了。那么,DRAM中提到的1X(18nm)、1Y(17nm)、1Z(16nm)等又都意味着什么?

在本文中,我们就此讨论一下所谓的“XXnm”的DRAM的真正意义。那么,所谓“XXnm”指的是哪里的尺寸呢?在谈论这个之前,我们先来聊一下当下的DRAM现状。

现在是2019年的下半年,最先进的DRAM正在由1X(18nm)向1Y(17nm)推进。而且,预计在2019年末量产1Z(16nm)。也就是说,DRAM是1nm1

nm

地实现微缩,为什么DRAM厂家执着于这“1nm的微缩”呢?

先说结论,“1nm微缩”如果“登场”得晚的话,年度销售额将会有1兆日元(约人民币670亿元)的差异。要理解这个,我们要首先理解DRAM的构造和变迁。

DRAM的构造和变迁

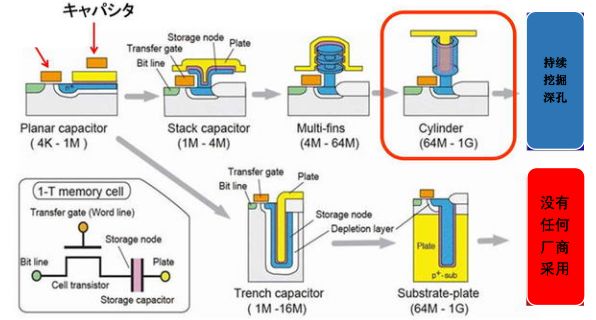

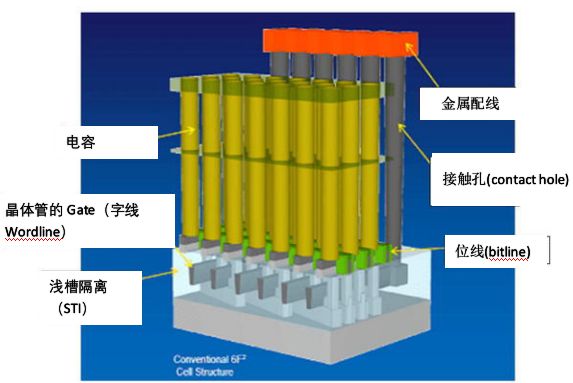

如图1所示,DRAM 是由一个晶体管和一个电容(Capacitor)构成的,晶体管处于“ON”的状态,电容储存电荷。也就是说,根据电容是否有电荷,进行“1”或者“0”的存储动作。

图1,DRAM的构造及变迁。(图片出自:《日本半导体历史馆》)

如图1 所示,4K-1M比特的DRAM是平面型(Planar型),然而,大于1M比特的话,电容就会变成像蘑菇形状一样的“堆栈型”(Stack型)、或者3层鳍状(Fin)构造(图1 的上半部分)、或者“沟槽型”(Trench型),即在晶体管下面的硅基板上凿孔,把侧壁当做晶体管(图1 的下半部分),由此就产生了下面的内容。

DRAM也遵循摩尔定律,每两年集成度就会扩大2倍。因此,晶体管、电容分别微缩了70%。但是,即使有微缩,电容也需要存储一定量的电荷。如果电荷过少,“1”和“0”的区别就会变得模糊,会对存储功能产生影响。

也就是说,DRAM的微缩难就难在--“即使实现微缩,也要保证电容存储的电荷保持一定”。为此,把平面型改为“堆栈型”、“沟槽型”,通过确保电容的面积从而保持一定的电荷量。

目前,DRAM市场被韩国三星电子、SK海力士(SK Hynix)、美国的美光科技(Micron Technology)三家公司垄断。这三家公司都采用了图1中右上角的“气缸型(sylinder )”,已经没有任何一家厂商采用“沟槽型”了。

也就是说,三家DRAM厂商都在晶体管上堆积绝缘膜、凿孔、形成电容。其结果,由于“即使微缩、也要存储一定的电荷”的缘故,对于DRAM厂商来说,每年“深挖细微孔”都是他们最重大的技术研发。

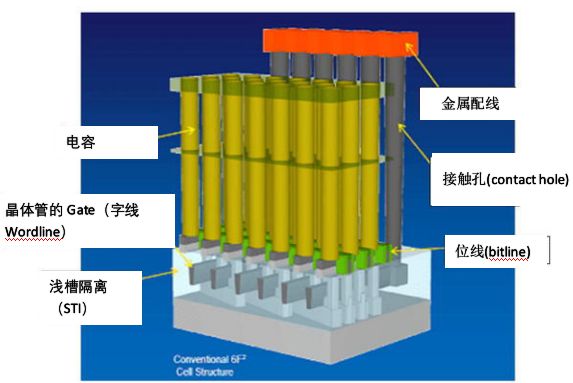

现在的DRAM构造和最细微的地方

现在的DRAM 构造如图2所示。笔者在2000年前后,曾在日立、Elpida(尔必达)从事256M-1G比特DRAM的研发工作,电容孔的直径、深度(高度)比(也就是“Aspect Ratio”,)曾是10-12。那时曾经“叫苦连天”地喊出“孔的加工太难了,已经极限了,已经不行了”!

图2 ,DRAM构造。(图片出自:Rick Merritt,《从折叠手机3D DRAM,SEMI event》(EE Times Japan、2019年1月21日),原始图片出自东京电子TEL.)

据说现在DRAM的“Aspect Ratio”(已经达到40-45。能够加工出深度(高度)比如此大的孔,深切感受到人类了不起的睿智!

在图2 的DRAM中,从下侧开始我们可以依次看到,分离各个cell的浅槽隔离(Shallow Trench Isolation)、晶体管的Gate(字线Wordline)、位线(bitline)、电容、接触孔(contact hole)、金属配线等。

其中,最细微的地方是哪里?如果说“18nm的DRAM”,18nm又在何处?

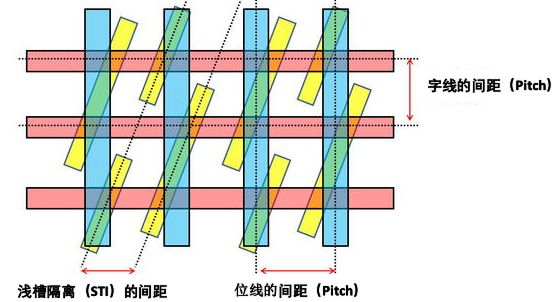

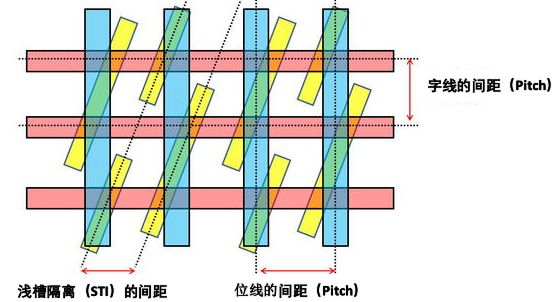

问题的答案通过图3中的DRAM的平面图来说明。首先,在硅上挖出沟槽,用绝缘膜填充沟槽后形成浅槽隔离(Shallow Trench Isolation)。其次,形成作为晶体管Gate的字线(Wordline)。接着,继续形成位线(bitline)。

图3,DRAM的平面图。(图片出自:jbpress)

其中,最细微的部分是浅槽隔离(Shallow Trench Isolation,STI),“18nm的DRAM”其实指的就是相当于“浅槽隔离(STI)”的间距的1/2(称为“Half Pitch”)的尺寸。也就是说,说起“○○nm的DRAM”,DRAM的“浅槽隔离(STI)”的1/2间距才是真正的nm尺寸。

DRAM的微缩推移及未来预测

图4,DRAM的微缩推移、未来的预测。(图片出自;笔者根据ITRS、IRDS的数据编纂而成。)

截止到2016年,以美国半导体工业协会(SIA)、日本的电子信息技术产业协会(JEITA)为中心,策划了“国际半导体技术蓝图(ITRS:International Technology Roadmap for Semiconductors)”,并且刊载了DRAM的细微性。

该技术蓝图被认为是为了Intel的处理器而制作的,背地里甚至曾被揶揄为“Intel Technology Roadmap for Semiconductors”!

ITRS在2016年寿终正寝,取而代之的是美国本土的电气电子工学学会(IEEE),并发布了名为“International Roadmap for Devices and Systems(IRDS)”的新技术蓝图。其中也登载了DRAM的微缩特性。

再看一下图4,截止到ITRS存在的2016年,从36nm到20nm,DRAM的微缩以对数函数的形式几乎呈现直线发展。但是,进入2017年以及以后的IRDS时代,可以看出,DRAM的微缩发展比ITRS的预测还要慢!

但是,尽管如此,据预测,DRAM还会以1-2nm的速度进行微缩的发展。那么,对于DRAM来说,1nm的微缩具有什么意义呢?

DRAM厂商拘泥于1nm的理由

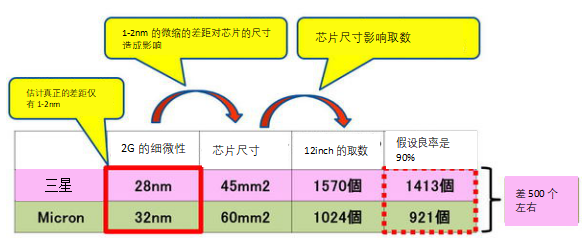

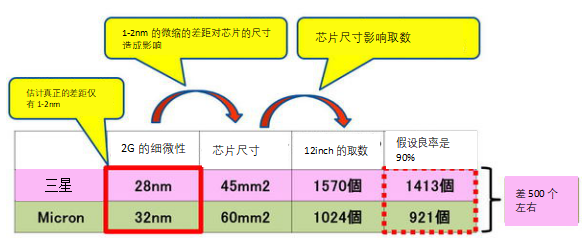

2012年-2013年期间,比较了三星电子和美光的2G比特的DRAM(如图5),同一时期,三星电子公布说“28nm”、美光公布说“32nm”。但是,怎么看三星都在数字上“打了马虎眼”,其实二者的细微差异仅仅只有1-2nm。

图5,三星电子和美光的2G比特的DRAM的比较。(图片出自:jbpress)

仅仅1-2nm的差距,就对DRAM的芯片尺寸造成了很大影响。实际上,三星电子的2G的DRAM是45m㎡,美光的是60m㎡。

于是,三星可以从直径为30cm(12inch)的硅晶圆上获得1570个DRAM, 美光可以获得1024个。假设两者的良率为90%,三星可以获得1413个芯片,美光可以取数921个芯片,其差约为500个左右。

假设一个DRAM为4美金,对于一颗硅晶圆,三星电子和美光的销售额差距约为2000美金。假设两家公司在月产能为50万颗硅晶圆的量产工厂生产DRAM,其差距就是10亿美金,1年(12个月)下来,其差异会扩大到120亿美金。1美金换算成110日元的话,一年就是1兆2,100亿日元。

总之,对于DRAM的1-2nm的细微性的差异,1年下来,就会产生超过1兆日元(约人民币670亿元)的销售额的差异。这就是DRAM厂商“拘泥”于这细微的1nm的理由!

实际上,这种情况也存在于处理器、SoC等逻辑半导体方面。因此,无论哪里的尖端半导体厂商,都“卯足了劲”要实现哪怕仅有1nm的微缩!

2016年以后,Intel停滞在14nm、没有进展,2019年下半年开始批量生产10nm工艺的处理器。这里的“14nm”、“10nm”都是Intel的“商品品名”。另一方面,三星电子、美光似乎也提前了IRDS,在2019年末预计要开始量产1Z(16nm)工艺的16G比特的DRAM。DRAM的浅槽隔离(STI)的“半间距(Half Pict)”其实是16nm。

最快在2020年上半年,可能会发布搭载了Intel的10nm处理器、16nm工艺的16G比特的DRAM的PC!

*点击文末阅读原文,可阅读

本文原文。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2093期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

AI|射频|

Chiplet

|中国芯|晶圆|制程工艺|存储|

快充芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!