观察:MRAM技术将走向何方

2019-12-02

14:00:14

来源: 半导体行业观察

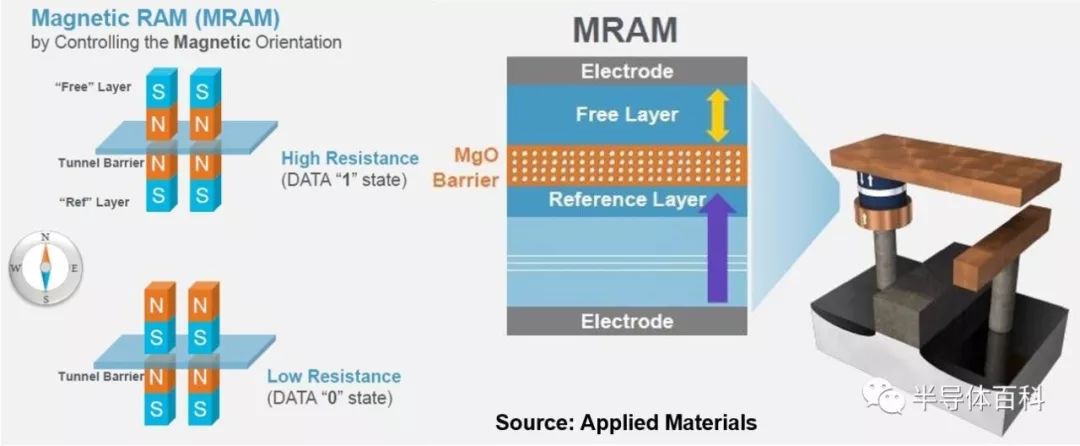

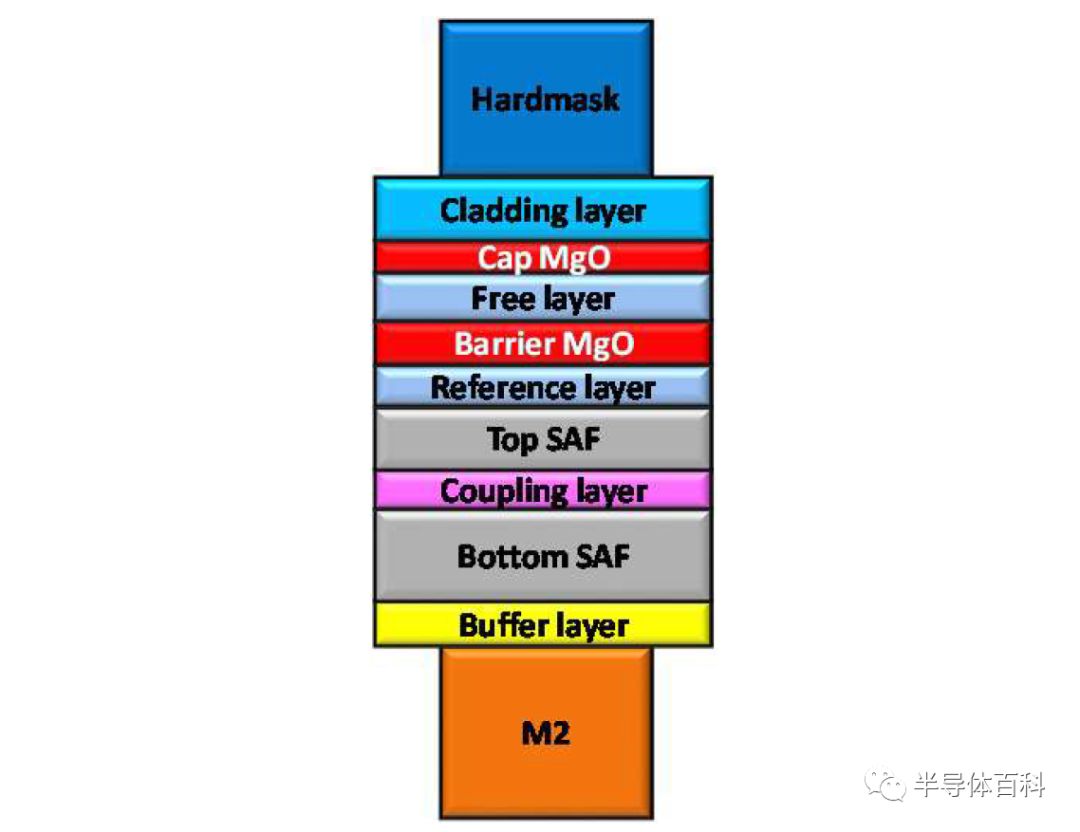

MTJ的数据存储依赖于由MgO和CoFeB层之间的界面各向异性产生的垂直磁各向异性(PMA)。电流可以将自由层的CoFeB磁性状态切换为与参考层平行(P)或反平行(AP)。如果是平行,则MTJ电阻较低,如果是反平行的,则电阻较高。施加写入电流,从一个方向流过MTJ使其从平行转变成反平行,而施加反向电流就又可以使其从反平行变成平行。

今年 IEDM的第2场分会(存储器技术–STT-MRAM)上会有一系列产业界的论文演讲。

首先是Everspin,这是为数不多的MRAM产品供应商之一。Sanjeev Aggarwal等人作题为“Demonstration of a Reliable 1 Gb Standalone Spin-Transfer Torque MRAM For Industrial Applications”的报告。

“我们展示了我们的1Gb独立STT-MRAM产品在-40 ℃至110 ℃的温度范围内的可靠运行。良好的4 sigma读写分布,使其可在85℃的情况下实现2E11个周期的耐久性和10年的数据保存寿命。”1 Gb芯片采用28nm技术制造,很可能在GLOBALFOUNDRIES的新加坡工厂生产。

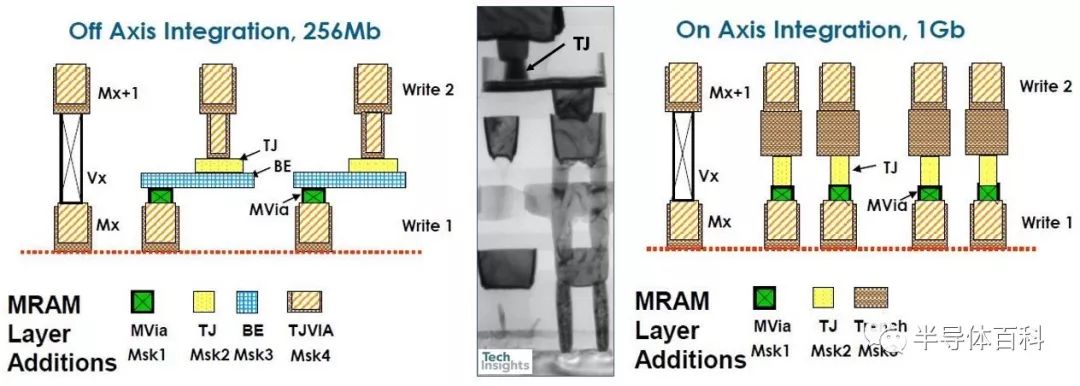

图2,Everspin 256Mb和1Gb STT-MRAM结构示意图,中间TEM为256-Mb的

今年8月的Flash Memory Summit上Everspin详细介绍了该器件[1],与256 Mb版本相比,似乎在结构上有所变化。新版本中,MTJ与write-1和write-2线共轴,而不是在早期版本中有所偏移。图中TJ层是隧道结层,通常称为磁隧道结(MTJ)。

此外,规格已从1.5V DDR3 VDD / VDDQ,JEDEC DDR3 ball configuration发展到1.2V DDR4 VDD / VDDQ,DDR4 ball configuration。上方示意图中,我很想知道沟槽(Trench)中的材料---某种额外的金属层?

紧接着是一系嵌入式MRAM的演讲,首先是三星,演讲者Kilho Lee,论文号2.2,题为“High Density Embedded STT-MRAM in 28nm FDSOI Technology”。

“成功展示了基于28nm FDSOI技术的高密度1Gb嵌入式STT-MRAM。该芯片基于高可靠性及可制造的eMRAM技术,在提供令人满意的读写性能和10年数据保存时间的情况下,达到了90%以上的高良率。与此同时,高达1E10个读写循环耐久性扩展了eMRAM的应用。”

早在IEDM 2016上,他们就提交了题为“Highly Functional and Reliable 8Mb STT-MRAM Embedded in 28nm Logic”的论文[2],该8Mb STT-MRAM基于其28nm LPP逻辑技术平台。由于MTJ堆叠集成到后段金属层中,因此前段可以是体硅或FD-SOI。以下我在这里为即将到来的演讲提供一些线索和想法。

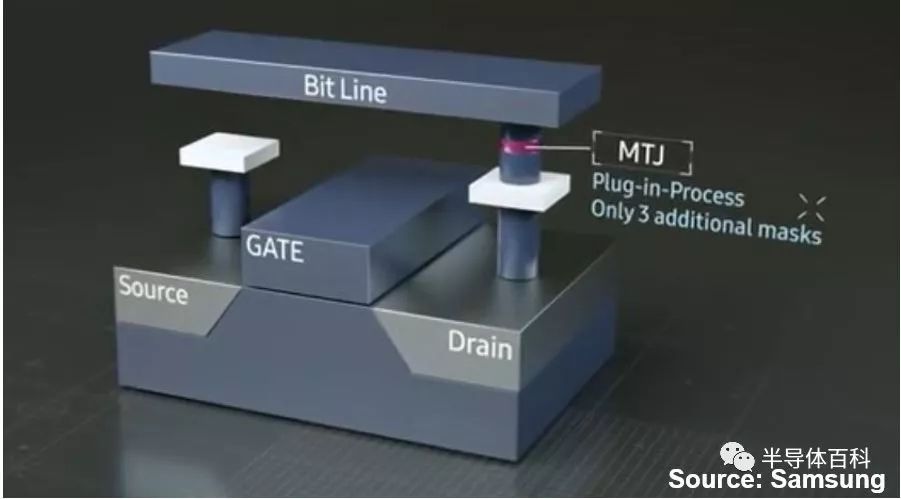

三星在2016年论文中的MRAM堆叠中使用了具有单个MgO和CoFeB(CFB)层的MTJ。MTJ的直径为38 – 45 nm,底部电极接触(BEC)为钨(从图像上也可以看到顶部接触)。

去年三月,三星宣布了基于其28FDS工艺的eMRAM规模量产,并称其写入速度比eflash快1000倍左右。因为MRAM不需要往介电层中推入电荷,所以操作电压更低,此外该e'MRAM仅需要三张光罩。

图4 三星介绍1T-1MTJ STT-MRAM的视频截图

在新闻稿中,他们没有讨论要出货的产品,但确实声明将要出货1Gb测试芯片,此演讲大概会提供更详细的信息。

Global Foundries一直在其22FDX工艺中推进MRAM,其论文号为2.3,Vinayak Bharat Naik等人作题为“Manufacturable 22nm FD-SOI Embedded MRAM Technology for Industrial grade MCU and IOT Applications”的报告。“我们展示了一款基于22nm FD-SOI的嵌入式MRAM,其在-40〜125°C的封装环节仍能实现功能和具有良好可靠性。该产品通过了LTOL,HTOL,1M耐久性和5次焊锡回流等可靠性测试。此外,我们验证了其具有超过500 Oe(编者注:Oe为高斯单位制磁场强度单位,1 Oe约为79.6 A/m)的抗磁场能力。”

他们去年的IEDM论文题目类似:“22 nm FD-SOI Embedded MRAM Technology for Low Power Automotive-Grade-1 MCU Applications”。该芯片通过了类似的测试,包括1M的耐久性和5次焊锡回流,对于Auto-G1等级,其温度范围推升至-40〜150°C。去年没有给出MTJ堆叠的详细信息,也许今年!

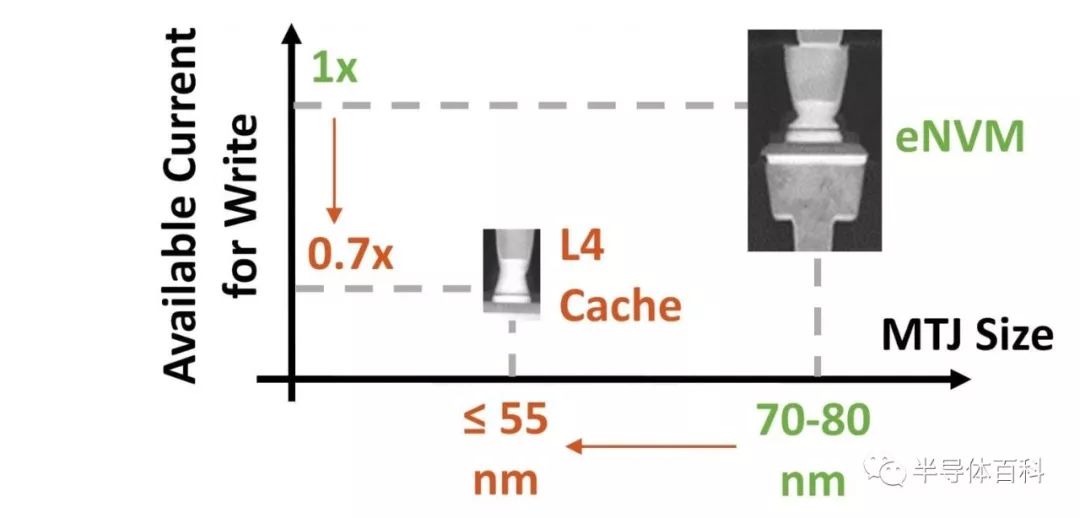

下一讲论文号为2.4,题为“2 MB Array-Level Demonstration of STT-MRAM Process and Performance Towards L4 Cache Applications”,作者是Juan G. Alzate等人。虽然先前英特尔已经宣布将MRAM集成到他们的22FFL工艺平台中[3],但此文中提到的MRAM是否基于22FFL工艺平台尚不清楚。鉴于文中MTJ尺寸已从〜80 nm减小到〜55 nm(〜70%),因此很容易推测该MRAM将用于1271 14 nm SoC工艺平台上。下图展示了微缩和改进的MTJ堆叠。

图5 Intel MTJ器件的TEM图像和微缩比例

在去年的IEDM[3]中,22FFL MTJ堆叠的示意图如下(图6):

英特尔在两层MgO之间放置了CoFeB自由层,从而增强了各向异性,进而提高了数据保留能力。合成反铁磁层(SAF)提高了热稳定性并稳定了参考层的磁化强度[4]。

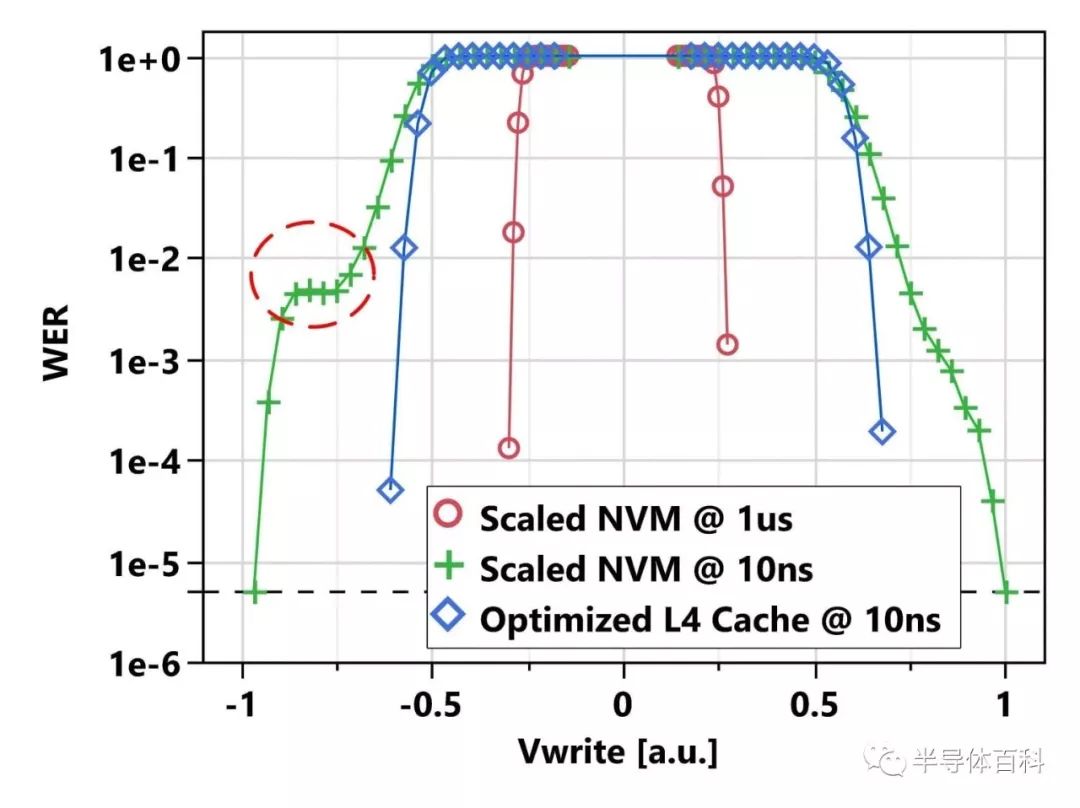

微缩MTJ尺寸可以减小写入电流,这听起来像是一个好主意,但这还与写入时间有关。在耐久性和写入错误率(WER)的约束下,需要同时权衡在较短的脉冲/较高的电流和较长的脉冲/较低的脉冲以及隧道氧化物的老化程度。

在研究中,英特尔工程师发现在写入时间为10 ns会电压“膨胀”现象(下图中的红色圆形虚线区域),这超出了L4缓存的WER规格限制。不过通过调整MTJ堆叠可以解决这个问题。

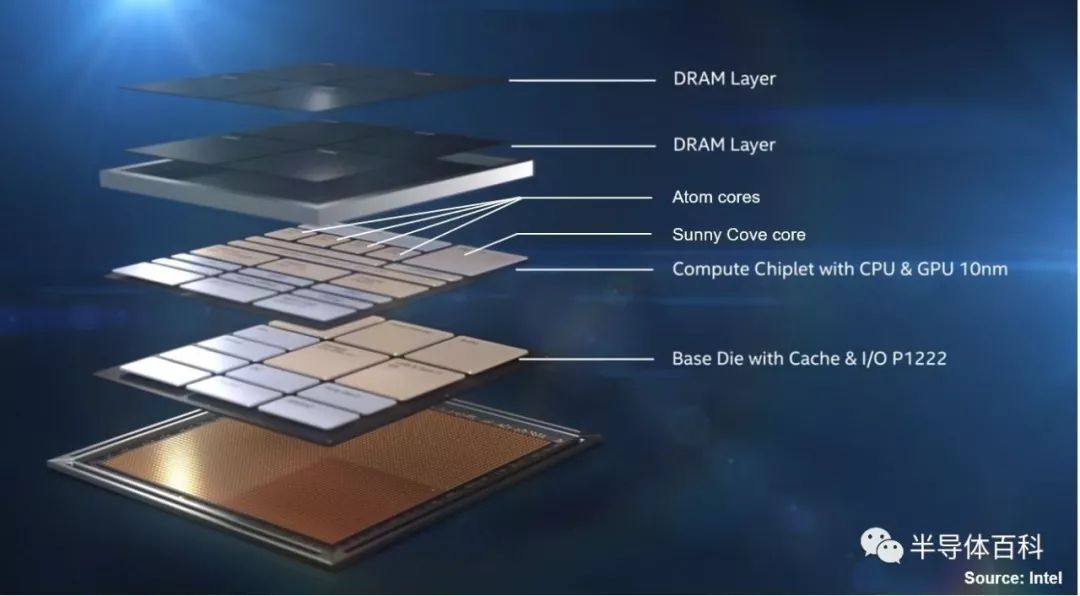

本文中的MRAM的目标是用作L4缓存,如果我没记错的话,它过去是由Intel的e-DRAM提供的。鉴于实际上该MRAM是在单独的芯片上,因此将其放在Foveros堆叠的基底芯片中也有一定可行性,如下图:

无论如何,英特尔都展示了2MB的可微缩MTJ器件阵列,“在所有正常运行温度下均符合L4缓存的技术规格。该MRAM在实现ECC校验的情况下拥有20 ns的写入时间,4 ns的读取时间,10E12次循环的耐久性以及在110℃的温度下能保持数据1秒。”

本文由Jason Jin翻译整理自Semiconductor Digest,

阅读原文

请点左下角。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2146期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

中美半导体|AI

|台积电

|英伟达

|

ASML

|

RISC-V

|

EDA|松下

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie