[原创] 三大晶圆厂的先进工艺进击之路

2019-12-13

14:00:05

来源: 半导体行业观察

先进工艺发展到今天,要拼的东西越来越多,尤其是5nm之后,不论是设备、材料、成本甚至是工艺本身都将发生质的飞跃。

例如在推进摩尔定律发展的过程中,EUV制造设备显得格外重要;

FinFET逐渐失效之后,GAA逐渐登上历史舞台。

只要摩尔定律不死,制程之战将永不停息。

这几年三星和台积电打的火热,英特尔则在一旁暗自蓄力。

近日,ASML在IEDM会议上“误读”英特尔的工艺路线图,更是吸引了读者面对晶圆制造商未来发展的巨大兴趣。

下面我们看一下三大晶圆厂台积电、三星和英特尔的工艺路线图。

众所周知,英特尔在10nm工艺技术上延迟多年,

不过近些时候他们似乎已经重回轨道。

相关报道指出,英特尔正在尝试尝试恢复通常的2年节奏,并已开始加速10nm工艺。

在IEDM会议上,ASML首席执行官Martin van den Brink还特意从设备供应商角度对英特尔的工艺路线图发表了自己的观点 。

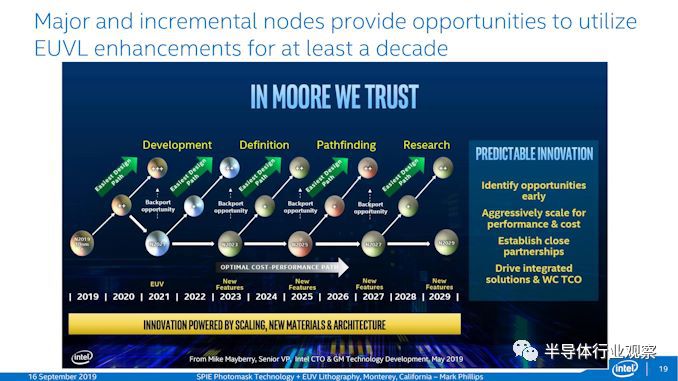

图注:

上图为ASML在英特尔原图的基础上增加了节点

首先我们需要强调一下,根据ANANDTECH的报道指出,ASML所演示的节点演进的ppt(上图)是在英特尔今年9月发布的内容的改版,ASML在幻灯片上添加了动画,使得日期的最下面一行对应于特定的节点。

而英特尔的原始幻灯片,没有详细说明哪个节点在哪一年。

英特尔预计其制造工艺节点技术将有两年的周期,从2019年的10nm开始,到2021年的7nm EUV,然后在2023年、2025年、2027年、2029年的每一年都有一个基本的新节点。

最后一个节点被ASML称为“1.4nm”,这也是第一次在有厂商提到1.4nm工艺。

但按照Intel所说,在每个流程节点之间,将会有迭代的+和++版本,以便从每个流程节点提取性能。

唯一的例外是10nm,因为它已经在10nm+上了,故明年会推10nm++,2021年推10nm+++。

英特尔相信,他们可以在一年的周期内做到这一点,但也有重叠的团队,以确保一个完整的进程节点可以与另一个节点重叠。

在IEDM会上,ASML还提到了向后移植。

何谓向后移植?

这是芯片在设计时考虑到一个进程节点的能力,但可能由于延迟,需要在相同的时间内在一个较老的“++”版本的进程节点上重新设计。

尽管Intel声明他们正在将芯片设计从流程节点技术中分离出来,但在某种程度上,为了在硅中开始布局,必须对流程节点做出承诺。

上图表明英特尔将允许这样一个工作流程,任何第一代7nm设计可以回移植到10nm+++,未来Intel的5nm来自于基础的7nm设计,3nm来自于5nm。

我们已经看到Intel的10nm需要很长一段时间才能完成,

所以期望Intel每年更新一次+,两年更新一次主要过程技术节点,将会是一个非常乐观和积极的节奏策略。

ANANDTECH还报道到,从上述中我们也可以看出,英特尔仍然相信摩尔定律,只是不要问它会花多少钱。

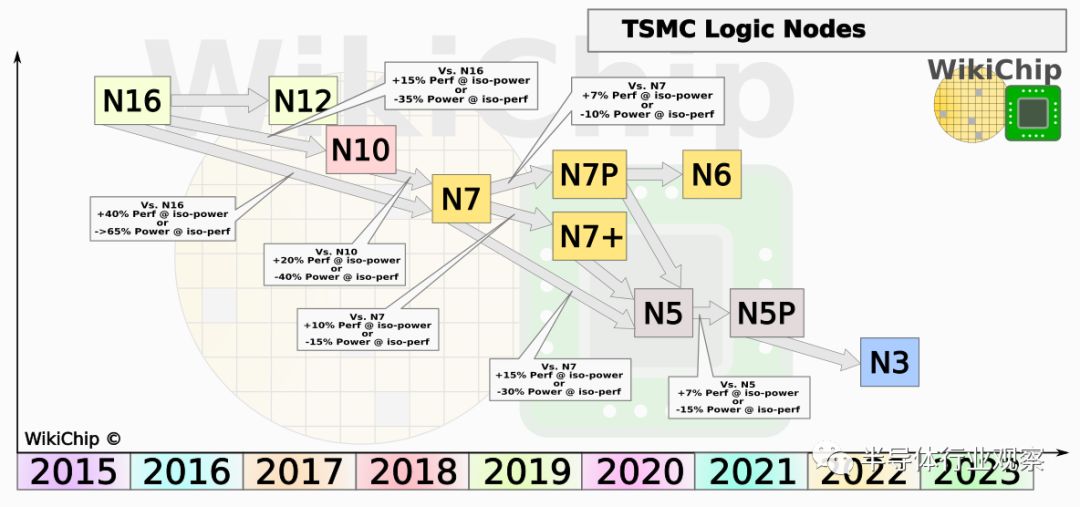

台积电的工艺研发速度在业界看来是很快的,尤其是对EUV工艺的掌握。

在晶圆代工领域,台积电毫无疑问是绝对的王者,而其工艺路线图的布局也是相当紧凑。

目前其5nm进入量产倒计时,3nm进展顺利,再往后就是2nm。

整体来看,据wikichip报道指出,台积电的10纳米节点(N10)节点被认为是一个寿命较短的节点,主要用于yield-learning。

台积电认为他们的7纳米节点是目前最先进的逻辑技术。

除了少数关键客户外,台积电的大部分客户据说都是从N16直接转到N7。

当从N16到N7时,N7提供3.3倍的路由门密度,以及大约35-40%的速度改进或降低65%的功率。

在N7基础上,台积电推出了N7P和N7+,N7P与N7+不能混淆。

N7P是一个优化的、基于DUV的流程,它使用相同的设计规则,并且与N7完全兼容。

N7P引入了FEOL和MOL优化,据说在等功率时性能提高7%,在等速度时性能降低10%。

N7 +是他们的第一批在某些关键层采用EUV的工艺技术。

与他们的N7工艺相比,N7 +的密度提高了约1.2倍。

据说N7 +在等功率情况下可提供10%的更高性能,或者在等功率情况下可降低15%的功率。

这样看来,N7+似乎比N7P更好一些。

N6的EUV相当于N7。

它计划比N7+使用更多的EUV层。

它既是设计规则,也是与N7兼容的ip,是大多数客户的主要迁移路径。

N7的设计可以重新粘贴到N6上,利用EUV掩模和保真度的改进,或者重新实现,利用poly over diffusion edge (PODE)和continuous diffusion (CNOD)标准单元基台规则,据说可以提供额外18%的密度改进。

值得强调的是,N6的独特之处在于,它将在明年年初进入风险生产阶段,并在2020年年底达到峰值。

这意味着它会在N5之后倾斜。

因此,台积电表示,N6是建立在N7+和N5 EUV的基础上的。

台积电5纳米制程是N7之后的下一个“完整节点”

。

N5同时使用深紫外线(DUV)和极紫外线(EUV)光刻技术。

N5可以在14层上使用EUVL来显著提高密度,N7+是在4个非关键层上使用EUVL,这可以说是一个切实的进步。

N5技术将允许芯片开发商将其设计的芯片面积缩小约45%,使晶体管密度提高约1.8倍。

它还能在相同的复杂性和功率下增加15%的频率或在相同的频率和复杂性下减少20%的功耗。

N5在今年第一季度进入风险生产,他们预计这一过程将在2020年上半年加速。

和N7一样,N5将有两种类型——移动客户端和高性能计算。

N5被规划为一个长期存在的节点,预计在收入方面,它将比N7增长得更快。

与他们的7纳米工艺一样,台积电将提供他们N5工艺的一个优化版本,称为N5性能增强版(N5P)。

这个过程使用相同的设计规则,并且与N5完全兼容。

通过FEOL和MOL优化,N5P在等功率时比N5的性能提高7%,在等功率时比N5的性能降低15%。

他们对N5P的时间表稍微模糊了一点,但他们有时会在2020年底或2021年初做出暗示。

台积电表示,他们的3纳米工艺进展顺利,已有客户参与进来。

台积电对外宣称,3nm是全新的节点,不是5nm的延伸。

另外,N3有望在2022年左右推出。

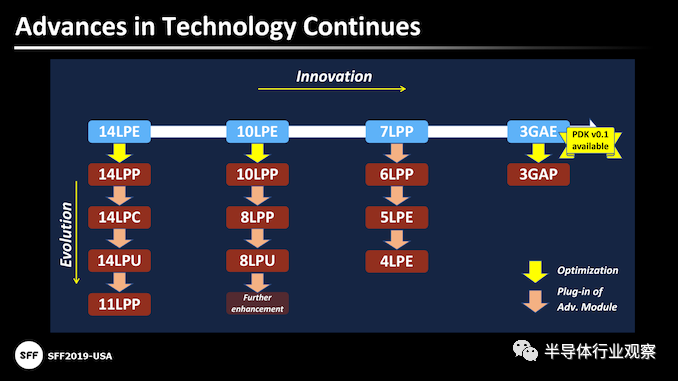

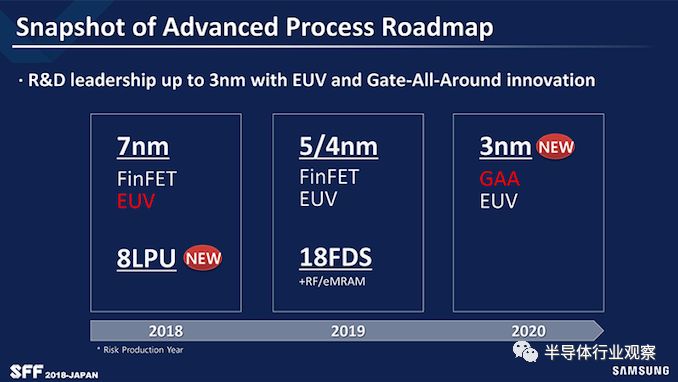

根据wikichip最新的报道,三星仍坚持他们几年前概述的战略——生产四个主要节点,即14nm、10nm、7nm以及3nm。

因其每个进化节点都是高度增量的,通常只引入单个更改。

这使得他们可以通过剥离一些之前引入的扩展助推器,并在后续节点上添加它们来降低新节点的风险。

但这样做的缺点是,三星的主要节点之间的间隔相当大,在PPA方面,它们落后于台积电。

例如在今年的路线图中的第一个修改是插入一个新的6纳米节点。

另一个变化是删除了4LPP节点,只在路线图上留下了4LPE。

最后,三星将3GAAE和3GAAP更名为3GAE和3GAP。

从路线图可以看出,三星主要在7LPP上下功夫,其中6LPP是三星7LPP的改进版,具有更高的晶体管密度,更低的功率,但可以重新使用最初为7LPP设计的IP。

然后就是5LPE,三星计划将5nm作为第二代EUV工艺。

但5LPE确实引入了一些新的增强功能。

根据wikichip的估计,三星5 nm节点UHD单元的密度已达到接近130 MTr /mm²,这是第一个超过英特尔10纳米节点和台积电7纳米节点的三星节点。

三星预计在今年下半年推出使用其5LPE技术的首批芯片,并预计在2020年上半年批量生产。

三星7LPP演进的顶峰将是公司的4LPE技术(可能4LPP不在最新的三星路线图中)。

三星将在今年下半年完成其开发,所以预计第一批流片将在2020年推出,并在2021年批量生产,ANANDTEC报道中指出。

真正发生重大变革的是3nm节点,因为3nm开始三星将放弃FinFET转向GAA晶体管,第一代是3GAE工艺,还有优化版3GAP工艺,后续还在继续优化改良中。

在这三家厂商的演进过程中,EUV光刻机是关键的一环,而台积电、三星和英特尔三家均计划在其生产路线图中采用EUV。

但台积电无疑是EUV光刻技术的领先者。

今年10月,台积电宣布其7nm plus(N7 +)节点已成为业界首个商业化的EUV技术。

N7 +是他们的第一批在某些关键层采用EUV的工艺技术。

Arete Research高级分析师Jim Fontanelli也表示,台积电在EUV领域处于领先地位,无论是所用的工具还是订购的工具,生产的商用EUV晶圆的数量,还是将EUV集成到他们未来的路线图中。

根据拓璞公布的数据预计,今年台积电的7nm(包括EUV)晶圆产能大概在10-11万片/月。

主要客户有:

AMD、海思、苹果、高通、赛灵思、英伟达等。

今年三星7nm LPP(EUV)工艺的晶圆产能大概在1万张/月,只有台积电的1/10左右。

三星在EUV上的布局也很早,早在2018年10月,三星就利用其7nm EUV工艺技术开始大规模生产芯片。

今年4月,三星宣布已经完成了其第一代5nm制造工艺(5LPE)的开发,该制造技术使用极紫外光刻(EUVL),与7nm工艺(称为7LPP)相比,可以提供显着的性能,功率和面积优势。

三星预计,到2020年,5nm将成为其主要的EUVL节点,这可能是因为该技术能够为多种应用提供众多好处,而三星的EUV收益率将会更高,这主要是因为三星在华城建造EUV生产线后,在未来几个月将拥有更多的EUV产能,该工厂耗资46.15亿美元,预计2020年开始大批量生产。

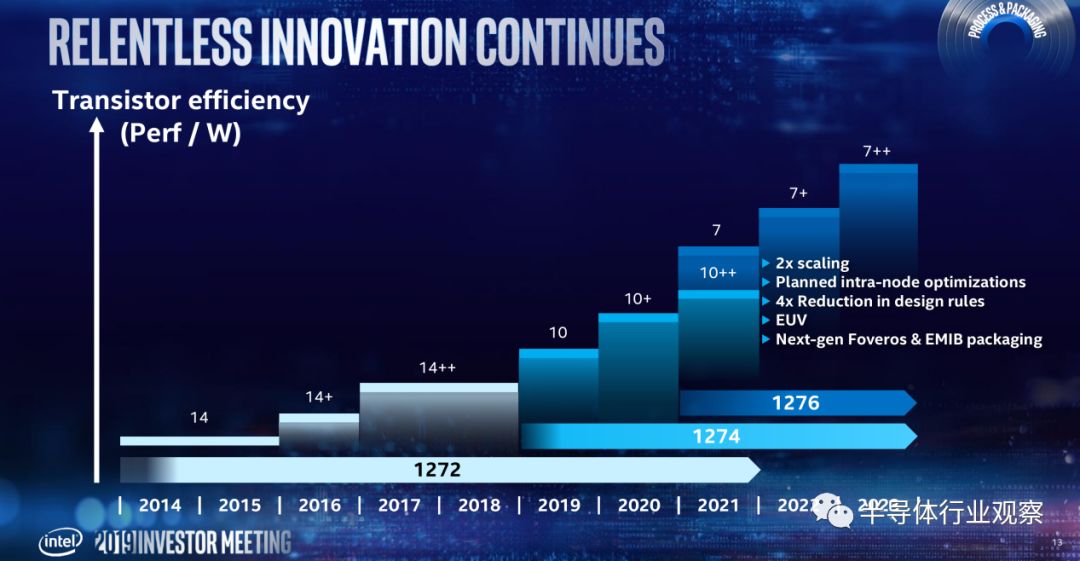

这些年来,英特尔在EUV研究方面一直是最积极的。

在最近的IEDM会议上,ASML首席执行官Martin van den Brink所披露的英特尔的工艺路线中,5nm被列为2023年的节点,大约在这个时候,ASML将开始销售其“High NA”EUV机器,以帮助英特尔在制造过程中更好地定义路径。

此前VLSI Research首席执行官Dan Hutcheson曾表示:“在这三家公司中,英特尔是一个谜,因为它没有销售方面的理由来宣传自己在做什么,而英特尔一向擅长把自己的litho工具推向一个节点。

他们在确信EUV已经准备好投入生产之前不会宣布。

”

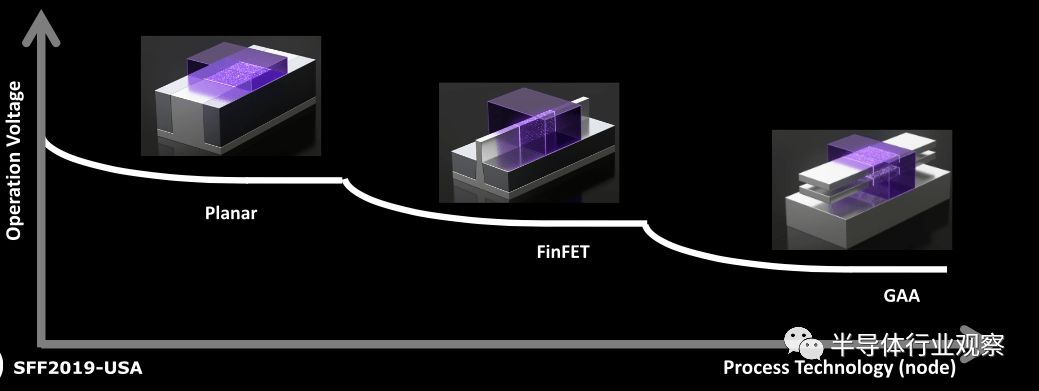

半导体工艺制程在进入32nm以下的节点后,每一步都艰辛无比。

首先是平面晶体管的失效,从技术发展角度来看,平面晶体管在尺寸缩小至22nm后,势垒隧道效应导致了电流泄露,漏电流控制将变得很困难。

而FinFET无疑是一个巨大的成功,尽管FinFET的发明要早于10多年,但它最早是在2011年由英特尔、三星、台积电等公司在22nm节点上商业化推出的。

从那时起,在摩尔定律定标的最后阶段,它就成了前沿硅逻辑的主力。

但随着尺寸减小,来到5nm和3nm以后,FinFET也不能胜任这项任务,FinFET本身的尺寸已经缩小至极限,无论是鳍片距离、短沟道效应、还是漏电和材料极限都使得晶体管制造难上加难,甚至物理结构都无法完成。

此时新型晶体管如GAA、二维晶体管、纳米片晶体管成为业界考虑的新方向。

其中GAA技术已经受到三星、台积电、英特尔的青睐,并且有的已开始试产。

平面晶体管与finFET与纳米片FET。

资料来源:

三星

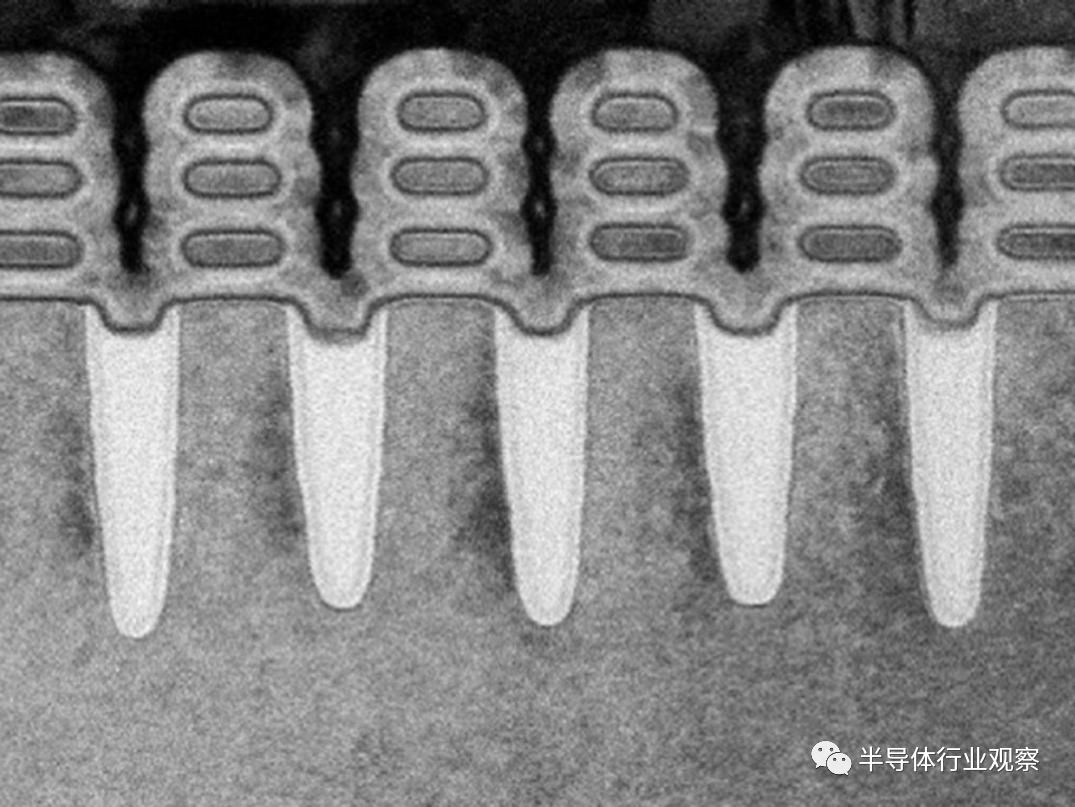

在GAA方面,三星表现最为突出,三星认为3纳米是其下一个主要工艺技术节点,计划将基于纳米片的Gate-All-Around MBCFET晶体管用于自己的3nm(3GAAE)工艺技术,这也是首个将使用GAA工艺的节点。

今年4月份,三星为其3纳米GAA工艺发布了其首个工艺设计套件(PDK)-版本0.1,预期2021年量产。

国际商业战略首席执行官Handel Jones表示,由于三星对包括石墨烯在内的先进材料的研发投入巨大,三星在台积电方面的GAA领先优势约为一年。

Jones说:

“三星在3纳米GAA中处于领先地位,其主要优势是由于内部可获取纳米片结构材料。

”

台积电虽然没有像三星那样直接给出官方说明,但是也已经开始GAA相关技术的研发和试产。

台积电计划在5纳米节点上推出其GAA技术版本,但尚未宣布将该技术投入生产的目标日期。

业内人士表示,台积电也已经完成了环绕式闸级结构晶体管的生产,但是采用的是圆形鳍柱,其典型尺寸比现有工艺缩小了30%。

二维晶体管也被看做是延续摩尔定律的最佳候选之一。

根据Nature自然科研的报道分析,因三维晶体管普遍面临着相同的问题,电子一般难以在纳米厚度的沟道内迁移,沟道表面的缺陷也会导致电荷散射,减慢电子流动速度。

而单原子层的二维材料有望使晶体管进一步缩小,由于它们的“垂直”维度有限,且表面平整没有缺陷,因而电子不易发生散射,电荷也能相对自由地在其中流动。

IEEE SPECTRUM报道指出,

纳米片晶体管是摩尔定律的下一步,也许是最后一步

。

作者Peide Ye在文中写到,

Nanosheet设备计划于2021年用于3纳米节点

。

2006年,法国CEA-Leti的工程师们提出使用一堆薄薄的硅板来连接电源和排水管,而不是使用一堆纳米线。

这个想法是在一个更小的晶体管中增加通道的宽度,同时保持对泄漏电流的严格控制,从而提供一个性能更好、功率更低的器件。

2017年IBM进一步研究了这一概念,表明由堆叠纳米薄片制成的晶体管实际上比占同样芯片面积的FinFET提供更多的Weff。

同时堆叠的纳米片对于化合物半导体(如砷化铟镓)和硅替代品(如锗)也显示出了广阔的前景。

除此之外,纳米片的设计还提供了一个额外的好处:

它恢复了向FinFET过渡时失去的灵活性。

可以将片材变宽以增加电流,也可以做成窄的以限制功耗。

IBM Research已经将它们堆叠在一起,尺寸从8纳米到50纳米不等。

总而言之,堆叠纳米片似乎是未来制造电晶体的最佳方式。

芯片制造商已经对这项技术有足够的信心,可以在不远的将来将其纳入自己的路线图。

随着高迁移率半导体材料的集成,纳米片晶体管可以把我们带到任何人现在都能预见的遥远未来。

Peide Ye在文章中写到。

至于未来晶体管的发展方向如何,笔者的观点是“行到水穷处,坐看云起时”。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2157期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

日本半导体|AI

|台积电

|IC

|

亚马逊

|

RISC-V|高通|DRAM

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie