来源:文章转载自期刊《微纳电子与智能制造》

作者:张 波,章文通,蒲 松,乔 明,李肇基,谢谢。

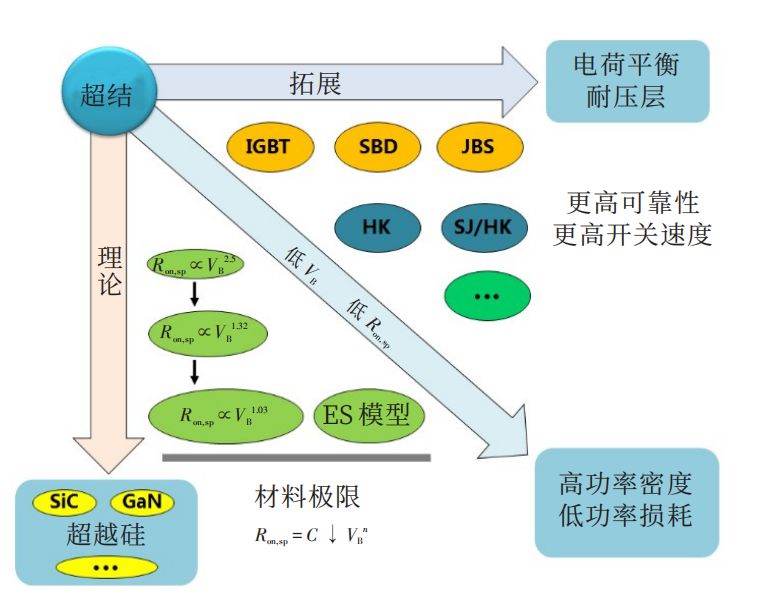

超结功率半导体器件是一类具有超结耐压层的重要器件,超结将PN结引入到常规“电阻型”耐压层中,使之质变为“结型耐压层”,这种质变突破传统功率器件比导通电阻和耐压之间的

R

on,sp

∝

V

B

2.5

“硅极限”关系,使之降低到

R

on,sp

∝

V

B

1.32

,甚至

R

on,sp

∝

V

B

1.03

,超结器件也因此被誉为功率半导体器件的“里程碑”。从耐压层角度回顾功率半导体40年发展的3个里程碑,综述了超结的发明、概念与机理、技术与新结构,并总结超结发展历程与趋势。

功率半导体器件是电能转换与控制的核心器件,所有电子产品均离不开功率半导体器件,无论是毫瓦级的便携式终端,还是兆瓦级的高铁。现代功率半导体技术已被广泛应用于国民经济的方方面面,从传统的工业电子、扩展到信息通讯、计算机、消费和汽车领域,新能源、轨道交通、电动汽车和智能电网正成为功率半导体市场增长的强大引擎。

在这些应用中,功率

MOS

和以其为核心的功率集成芯片在整个功率半导体市场份额占比高达

74%

,在

2016

年功率单管的

118

亿的销售中,功率

MOS

占比达

49%

(

IHS iSuppli Research

,

August 30

,

2017

)。超结的出现,使得器件比导通电阻大幅降,被国际上誉为“功率

MOS

器件的里程碑”,超结的优越特性也带来了巨大的市场需求,有人预计

2020

年市场规模将高达

22

亿美元,功率芯片已被视为中国半导体破局的重要领域。

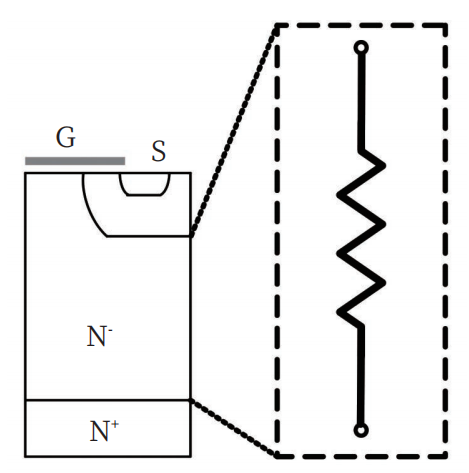

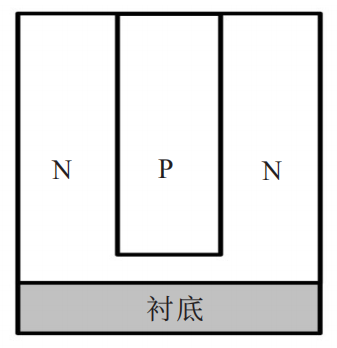

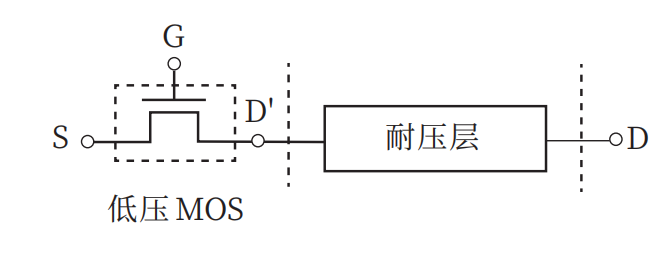

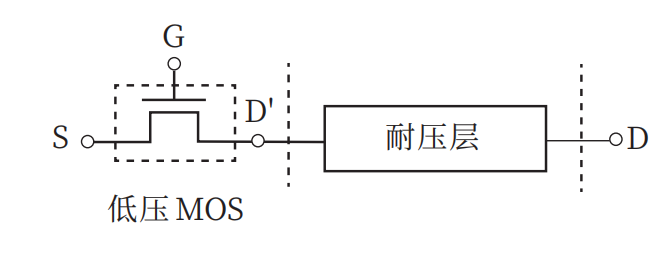

与低压半导体器件相比,功率半导体器件关态条件下需承受高电压,具有耐压层结构,可以看成低压控制器件与耐压层形成的复合结构。如图

1

所示,功率

MOS

器件可视为低压

MOS

漏端

D

与准漏端

D'

之间插入耐压层的复合结构,其控制部分工作机理与低压

MOS

基本相同。功率半导体器件设计的关键之一是耐压层的设计。

图1.功率半导体简化结构

理想的耐压层应在关态下承受高电压,在开态下导通大电流,并实现两者之间的快速转换。因此,其基本要求是高耐压、低导通电阻和高开关速度,其优化的本质就是实现特定应用场景下的最佳折衷。

20

世纪

70

年代发明的

VDMOS

,为承受高耐压采用具有单一导电型的“电阻型”耐压层,人们很快发现其比导通电阻和耐压之间存在

R

on,sp

∝

V

B

2.5

极限关系,使器件功耗随耐压剧增。大量研究致力于如何使器件性能尽可能接近甚至突破“硅极限”,从耐压层演变角度,需要在保证耐压前提下尽可能增加开态载流子浓度,功率半导体器件呈现了不同的发展阶段。

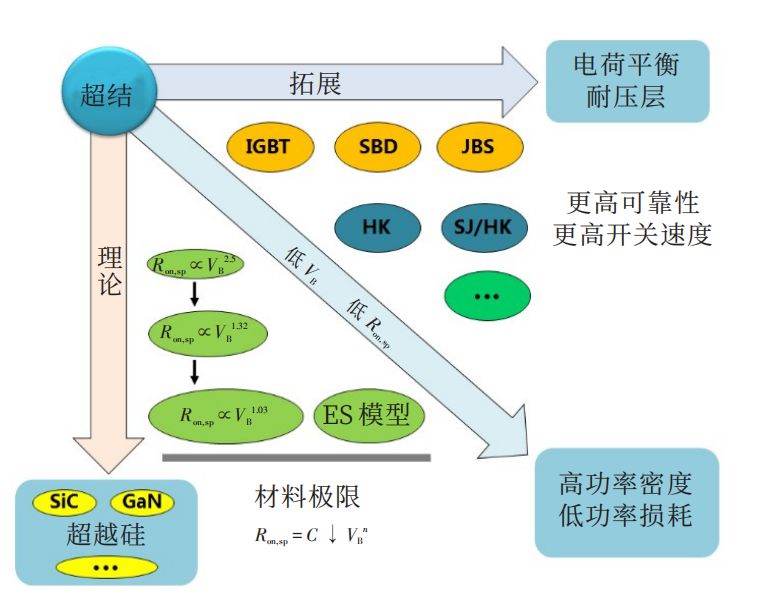

图

2

给出功率半导体

40

年发展的

3

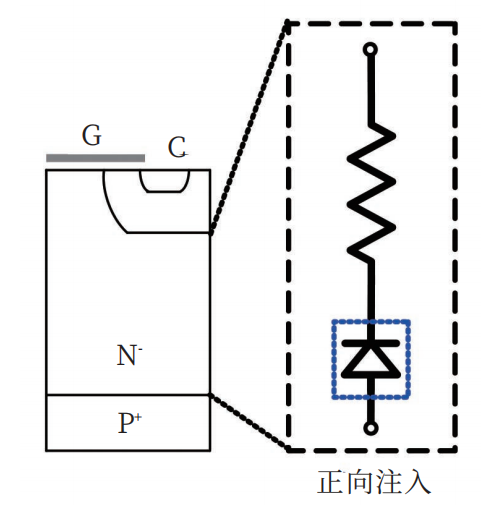

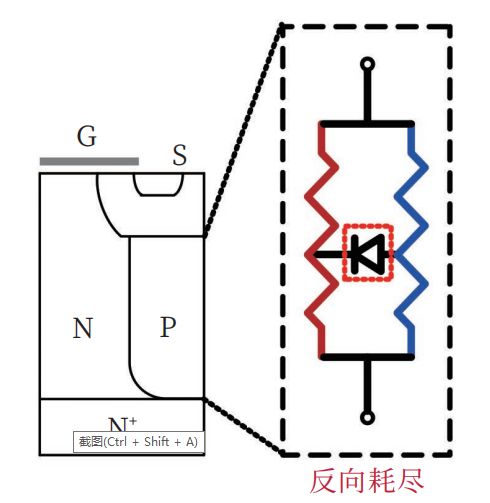

个里程碑:

(

a

)里程碑

I

阻型耐压层器件,器件耐压层为具有

N

或

P

单一导电类型的低掺杂半导体层,其特性受“硅极限”限制,典型结构为常规

VDMOS

器件;(

b

)里程碑

II

电导增强阻型耐压层,通过将

PN

结正向注入特性引入到阻型耐压层中,大注入非平衡载流子增加开态载流子浓度,典型结构为

IGBT

;(

c

)里程碑

III

结型耐压层,将异型掺杂引入到耐压层内部形成周期性交替掺杂的耐压层结构,其特点是将

PN

结反向耗尽特性引入到耐压层内部,实现两区之间的电荷平衡,典型结构为本文重点阐述的超结,耐压层从“阻型”到“结型”的转变为耐压层结构的一次质变。

图

2.

功率半导体器件

40

年发展的

3

个里程碑

图1.功率半导体简化结构

理想的耐压层应在关态下承受高电压,在开态下导通大电流,并实现两者之间的快速转换。因此,其基本要求是高耐压、低导通电阻和高开关速度,其优化的本质就是实现特定应用场景下的最佳折衷。

20

世纪

70

年代发明的

VDMOS

,为承受高耐压采用具有单一导电型的“电阻型”耐压层,人们很快发现其比导通电阻和耐压之间存在

R

on,sp

∝

V

B

2.5

极限关系,使器件功耗随耐压剧增。大量研究致力于如何使器件性能尽可能接近甚至突破“硅极限”,从耐压层演变角度,需要在保证耐压前提下尽可能增加开态载流子浓度,功率半导体器件呈现了不同的发展阶段。

图

2

给出功率半导体

40

年发展的

3

个里程碑:

(

a

)里程碑

I

阻型耐压层器件,器件耐压层为具有

N

或

P

单一导电类型的低掺杂半导体层,其特性受“硅极限”限制,典型结构为常规

VDMOS

器件;(

b

)里程碑

II

电导增强阻型耐压层,通过将

PN

结正向注入特性引入到阻型耐压层中,大注入非平衡载流子增加开态载流子浓度,典型结构为

IGBT

;(

c

)里程碑

III

结型耐压层,将异型掺杂引入到耐压层内部形成周期性交替掺杂的耐压层结构,其特点是将

PN

结反向耗尽特性引入到耐压层内部,实现两区之间的电荷平衡,典型结构为本文重点阐述的超结,耐压层从“阻型”到“结型”的转变为耐压层结构的一次质变。

图

2.

功率半导体器件

40

年发展的

3

个里程碑

从上面的论述可以看出,耐压层演变的特点是巧妙地将

PN

结的正向与反向特性引入常规阻型耐压层中,从而实现耐压层电阻降低。

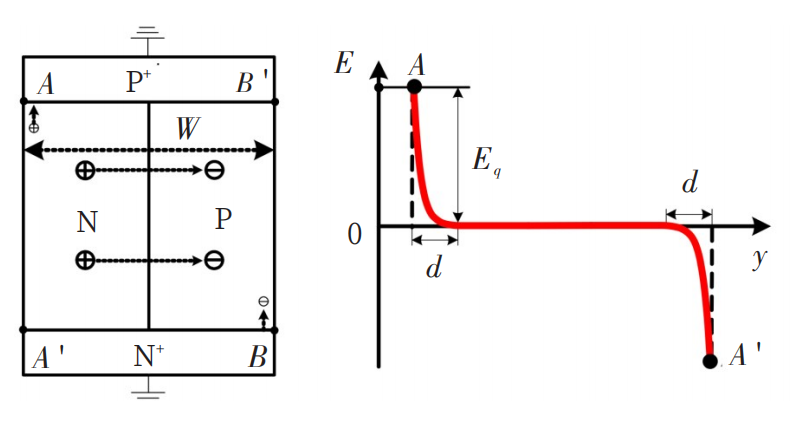

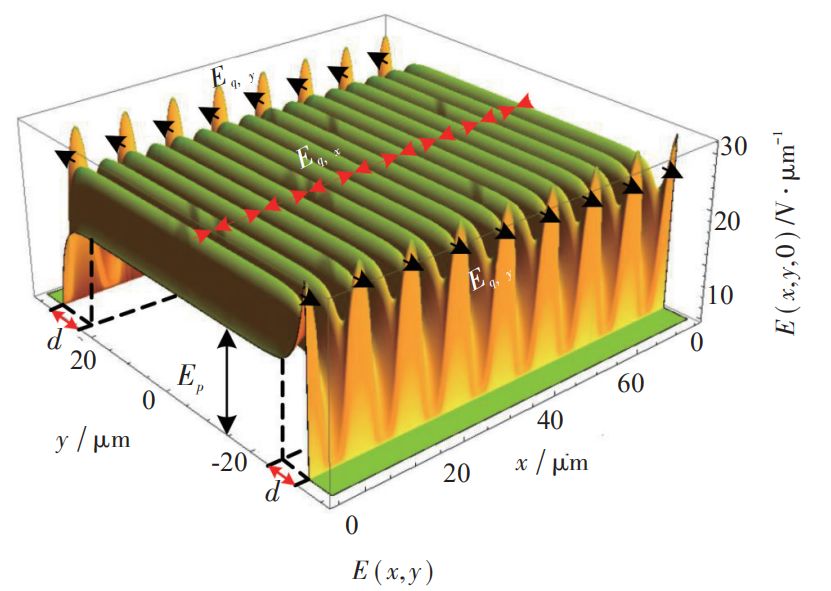

与阻型耐压层相比,超结结型耐压层由于内部引入

PN

结,关态条件下

N

区电离正电荷发出电场线大部分流向毗邻

P

区电离负电荷,在耐压层内部引入显著的二维场效应,这种复杂场调制极大降低器件表面电场峰值并优化了体内场分布。结型耐压层电场线与零电势边界条件下由电离电荷产生的电荷场

E

q

(

x

,

y

)

分布,如图

3

所示,其中

W

为超结条宽度,由于耐压层内部电场线横向流走,导致

AA

′

上大部分区域电离电荷产生纵向场为零,只有在表面

A

点所在

P+N

结位置产生局部电场分布,高电场在纵向很短的距离

d

(据笔者计算

d

≈0.78

W

)范围内以指数函数迅速衰减,由于对称性在

A

′

点产生负的电场峰值,

BB

′

线上电场可以类似分析。

上述横向电荷场对纵向电荷场调制使得超结关态条件下二维场分布如图

4

所示,结型耐压层内部电场呈周期函数分布,以耐压层纵向中线电场为例,峰值位于每个

PN

结面,谷值位于每个

P

条或

N

条中心位置。器件结型耐压层端面亦呈现周期性峰值分布,与内部不同,其波峰与波谷皆位于每个

P

条或

N

条中心位置上,峰值位于上表面

P

+

N

结或者下表面

N

+

P

结位置,而谷值位于

P

+

P

或

N

+

N

结位置。纵向高电场局限在

W

距离内,因此耐压层内部纵向场分布几乎不受影响。且随长度增加,高场区保持相同分布且与表面相对位置不变。

常规理论认为,理想的超结器件需满足耐压层内部电场线全部从

N

区指向

P

区,即满足电荷平衡条件以实现纵向场分量为矩形,电荷非平衡将导致器件耐压降低。然而笔者发现,在开态条件下,当考虑载流子电荷影响时,巧妙应用电荷非平衡可以降低器件损耗并增加器件的安全工作区。

超结器件出现后,不同研究者分别对其进行理论分析:一维近似法将超结在耐压方向上视为具有均匀场的一维

PIN

、垂直耐压方向上视为一维

PN

结,两个方向上电场同时达到

E

c

时最优。或者将超结电场看成耐压方向与垂直耐压方向上两个一维场的叠加,可得到类似结果。一维近似主要用于超结器件的概念分析或者参数估算。

超结二维场优化法建立在二维精确解析场分布的基础上,其二维精确解在超结发明后很长一段时间才于

1998

年由电子科技大学陈星弼院士率先提出,进一步将击穿时耐压层恰好全耗尽选为优化条件,从而获得经典

R

on,sp

∝

V

B

1.32

关系。此外,还提出一种分区求解二维泊松方程的方法,结论类似,不再赘述。

上述优化方法均未给出超结器件的最低比导通电阻

R

on,min

。由于超结二维场调制效应,研究发现击穿条件下图

3

中

A

′

和

B

′

局部非全耗尽时器件

R

on,sp

更低,笔者团队基于该特性提出超结非全耗尽(

nonfull depletion

,

NFD

)模式,通过全域

R

on,sp

优化寻求

R

on,min

,理论上证明新模式下平衡对称超结满足:

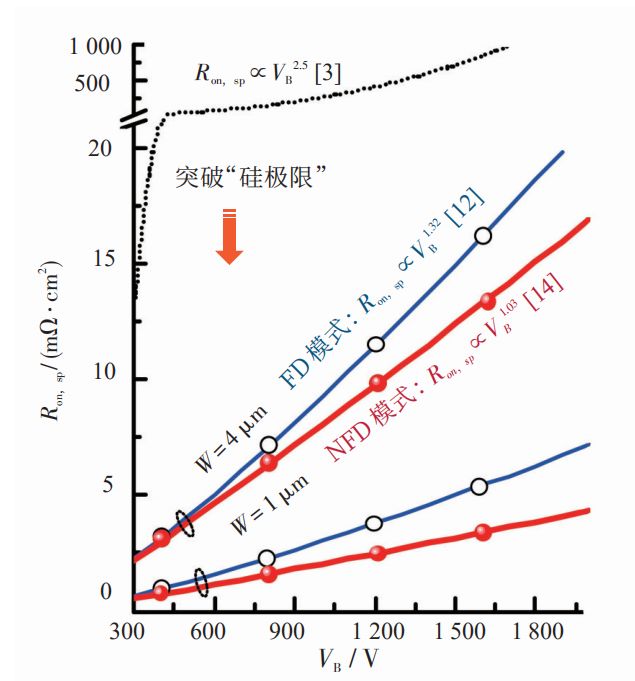

R

on

,

sp

=

1.437

×

10

-3

W

1

.108

V

B

1.03

(

m

Ω

·

cm

²

)(1)

图

5

给出超结

R

on

,

sp

-

V

B

关系与传统硅极限

R

on

,

sp

∝

V

B

2.5

关系比较,与传统“硅极限”相比,超结器件

R

on,sp

正比于超结条宽度

W

,依赖于元胞尺寸,因此在一定范围内(

W

>0.2μm

)可以通过工艺改进缩小元胞宽度增加掺杂浓度的形式进一步降低

R

on,sp

。

图

5.

超结与

R

on

,

sp

-

V

B

关系与传统“硅极限”比较

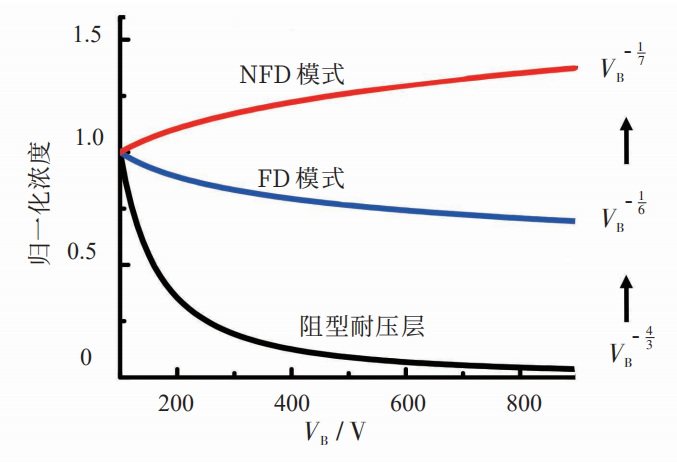

器件

R

on,sp

主要由耐压层长度与掺杂浓度决定,为实现高击穿电压,不同类型的耐压层长度无显著差异,因此超结突破常规“硅极限”的实质是突破了器件掺杂浓度与

V

B

的依赖关系。图

6

给出

NFD

、

FD

超结与常规阻型耐压层浓度变化规律,图中采用

100V

器件优化掺杂浓度进行归一化。由于阻型耐压层掺杂浓度依赖于耐压层长度,其优化掺杂浓度随

V

B

显著降低,而

NFD

超结掺杂浓度甚至随

V

B

略有增加。这种变化源于结型耐压层掺杂剂量由超结条宽度

W

决定,且几乎独立于耐压层长度。

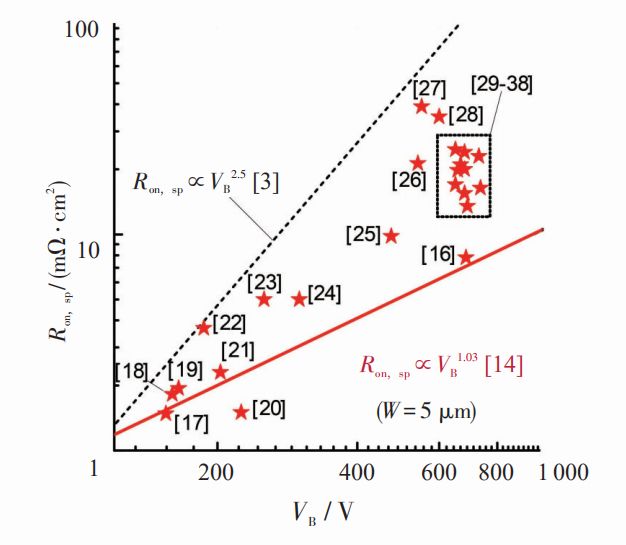

图

7

表明超结在不同耐压级别上都实现了对“硅极限”的突破。以文献中实验结果为例,分别采用宽度为

1.3μm

的

P

条和

1.7μm

的

N

条,实现

V

B

为

685V

,

R

on,sp

仅为

7.8

m

Ω

·

cm

²

,传统“硅极限”在相同

V

B

下

R

on,sp

为

101.9

m

Ω

·

cm

²

,超结器件

R

on,sp

降低了一个数量级。目前实验获得的超结

R

on,sp

主要位于式(

1

)中

W

为

5

μm

所对应关系以上。

超结概念也被引入到横向器件中以降低器件的功率损耗,由于横向超结可以通过表面注入形成且与常规

CMOS

工艺兼容,横向超结器件已成为高压功率集成技术的重要发展方向。与纵向超结器件不同,横向器件常常将超结置于

P

型衬底之上,表面超结区由于受到衬底辅助耗尽(

substrate-assisted depletion

,

SAD

)效应的影响,导致耐压降低。

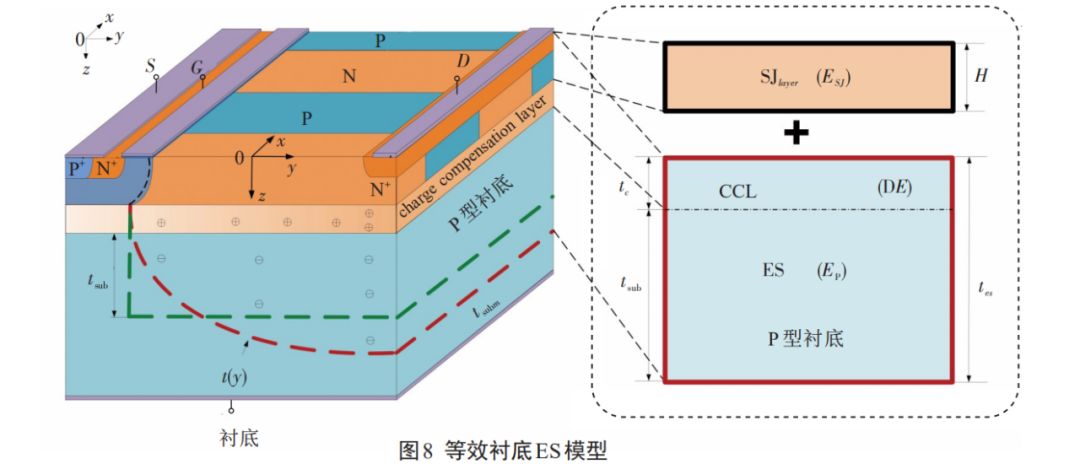

衬底辅助耗尽效应可以通过等效衬底(

equivalent substrate

,

ES

)模型描述 ,其原理如图

8

所示。将除超结之外的耐压结构,即电荷补偿层(

chargecompensation layer

,

CCL

)与衬底视为一个整体,定义为等效衬底

ES

,研究其整体对表面超结的调制作用。

ES

模型揭示了衬底辅助耗尽效应的本质是衬底电离电荷影响表面超结电荷平衡,致使

P

条非全耗尽而

N

条全耗尽,器件耐压降低。

为消除其影响,理论上

ES

层需满足的理想衬底条件:

(

a

)电中性条件:

ES

净电荷

Q

ES

→0

,等效衬底为准电中性,超结中

N

区和

P

区之间的电荷平衡得以满足。

(

b

)均匀表面场条件:

E

(

x

,

y

,0)

=

常数,等效衬底均匀表面场条件避免器件表面提前击穿。

一种实现理想衬底条件的版图如图

9

所示,在超结耐压方向上通过开不同窗口形成优化掺杂分布使得

CCL

与衬底保持电荷平衡,同时调制

ES

电场实现矩形分布。

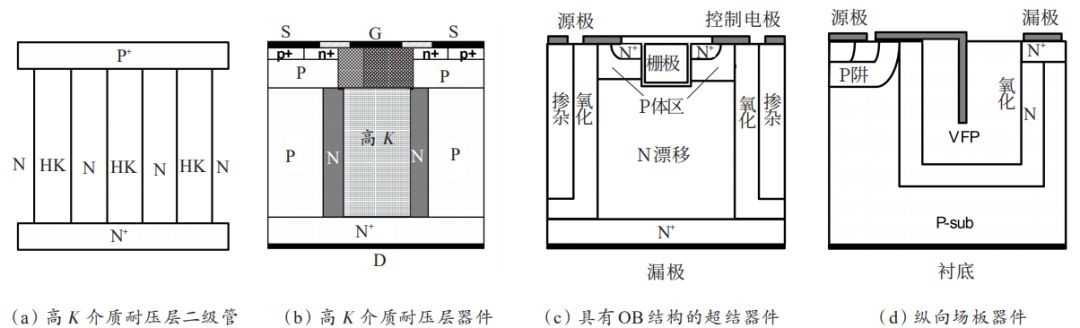

由于结型耐压层实现难度较大,很长一段时间内对超结器件的研究主要体现在工艺上,包括耐压层实现技术与终端技术。同时将超结耐压层用于不同的功率半导体器件中,实现特性改善或形成新型功率半导体器件。

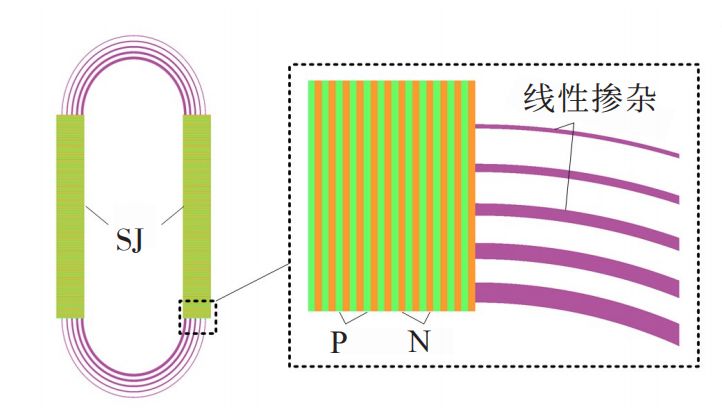

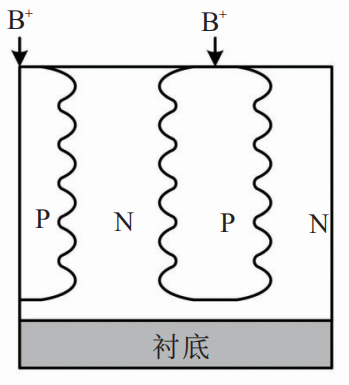

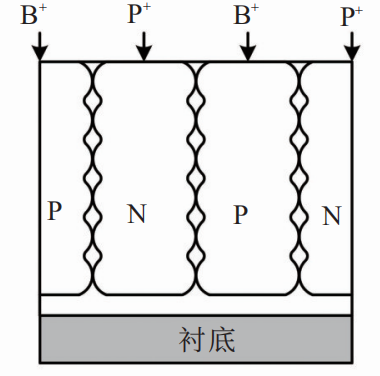

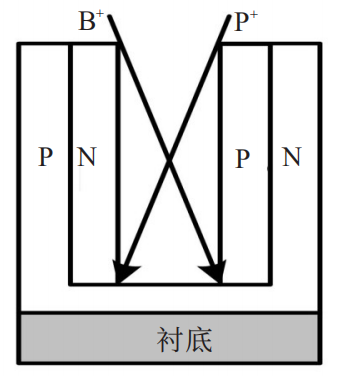

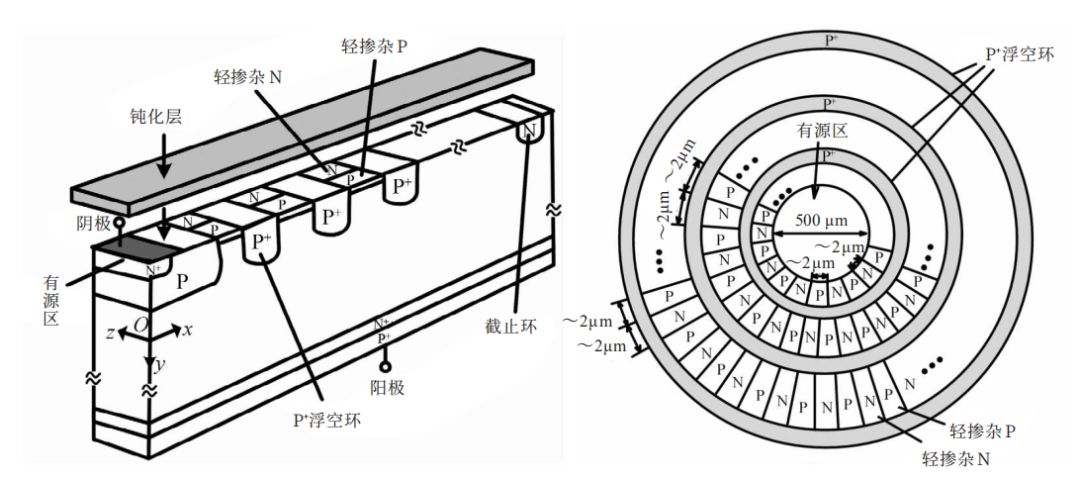

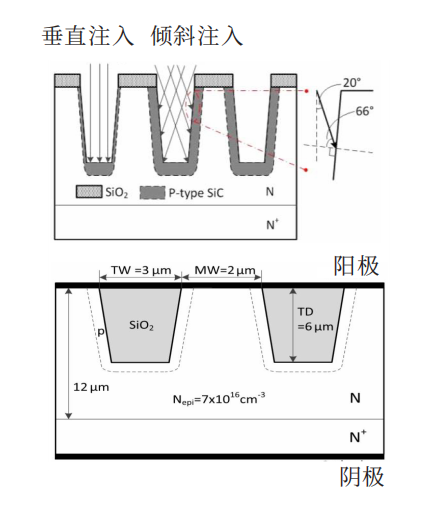

超结工艺的难点是如何在耐压层内部引入周期性的异型掺杂,如图

10

所示为多次外延掺杂工艺,其中第一种方法通过多次外延一定浓度的

N

型区,然后仅采用

P

型注入补偿形成超结

P

区;第二种方法是每次外延浓度较低,然后同时引入

N

和

P

型注入,分别形成超结的

N

区和

P

区,第二种工艺可以控制更好的均匀性,但工艺上需增加一次光刻与注入。此类工艺的优点是形成超结耐压层的晶格质量较好,缺陷与界面态少。然而为形成较好超结形貌,每次外延层厚度相对固定且较薄,外延次数将随着器件耐压增大而增多,导致成本增加。

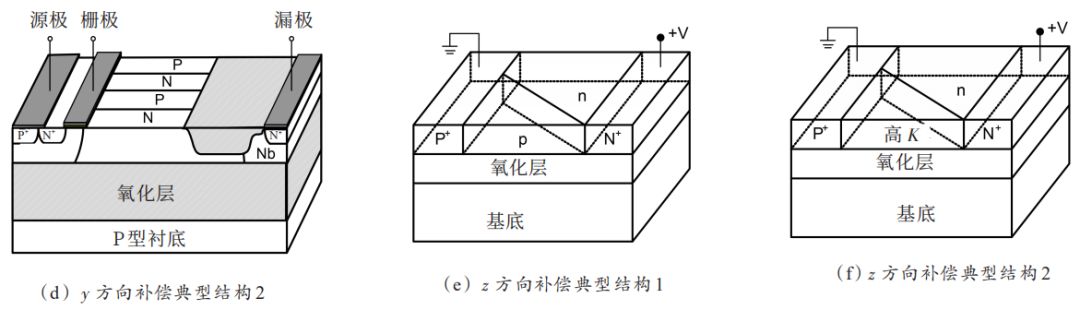

另一种结型耐压层实现工艺基于深槽刻蚀,如图

11

所示,其中图

11

(

a

)给出具有刻蚀槽的耐压层结构。通过在超结耐压层中刻蚀形成一定深宽比的槽,再对槽内部掺杂。第一种方式是在槽内外延填充

P

型硅,然后采用化学机械抛光平坦化实现超结耐压层,抛光后耐压层如图

11

(

b

)所示。还可以在槽壁上形成薄氧化层结构,再进行多晶硅填充形成耐压层;第

2

种方式是采用倾斜注入分别在槽壁上形成

N

区和

P

区,这样可以控制

N

和

P

型杂质的注入剂量来实现电荷平衡,如图

11

(

c

)所 示;第

3

种方式通过对槽壁气相掺杂形成

P

型区,如图

11

(

d

)所示。此外,还可以在槽壁选择性外延薄层

N

与

P

型硅或者是直接通过

P

型杂质扩散形成超结耐压层。采用刻槽填充工艺实现的超结耐压层较多次外延技术更易实现较小的深宽比,同时形成的超结

N

区与

P

区掺杂分布也较均匀,有利于降低

R

on,sp

。

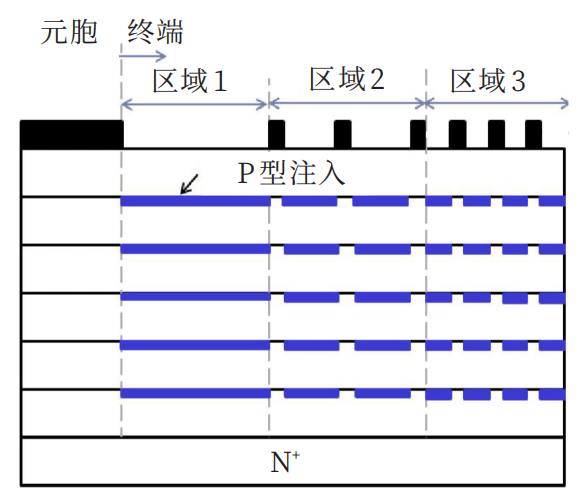

为实现超结器件终端区高耐压,有两种典型超结器件终端结构,如图

12

所示。图

12

(

a

)表示具有变掺杂的终端结构,对多外延型工艺,可以改变

P

型注入区窗口,

P

型掺杂浓度从元胞到终端方向逐渐降低,保持终端区新的电荷平衡。基于深槽刻蚀的超结器件则主要通过优化终端区刻蚀窗口来实现类似变掺杂终端。图

12

(

b

)给出采用常规表面终端技术的超结器件终端结构,其特点是将结型耐压层埋入器件体内,减少超结内部

PN

结对器件表面场的影响,同时在器件终端区表面采用常规结终端技术实现高耐压。

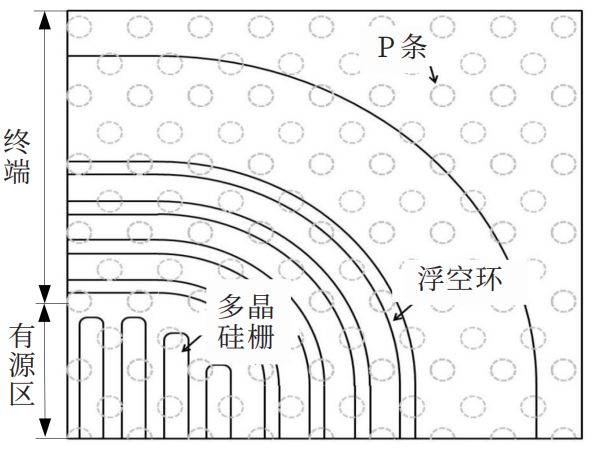

超结不仅可以用来降低器件比导通电阻,同时可用以优化电场分布,如图

13

所示为基于超结的终端结构,在常规浮空场限环间引入表面超结,建立新的电荷平衡,削弱了界面寄生电荷的影响,缩小终端区面积。

对横向叉指型超结器件而言,由于表面超结结深较浅,容易在终端指尖位置提前击穿,为解决此问题,作者团队提出如图

14

所示的衬底终端技术,通过将部分衬底电荷引入到器件表面,降低曲率效应,实现终端区新的电荷平衡,提高器件耐压,且具有工艺兼容的优点。

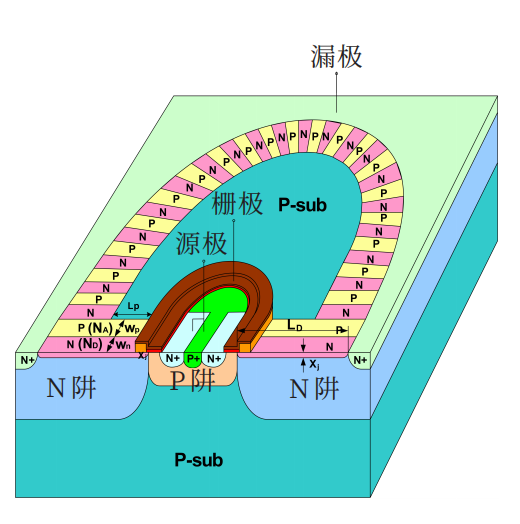

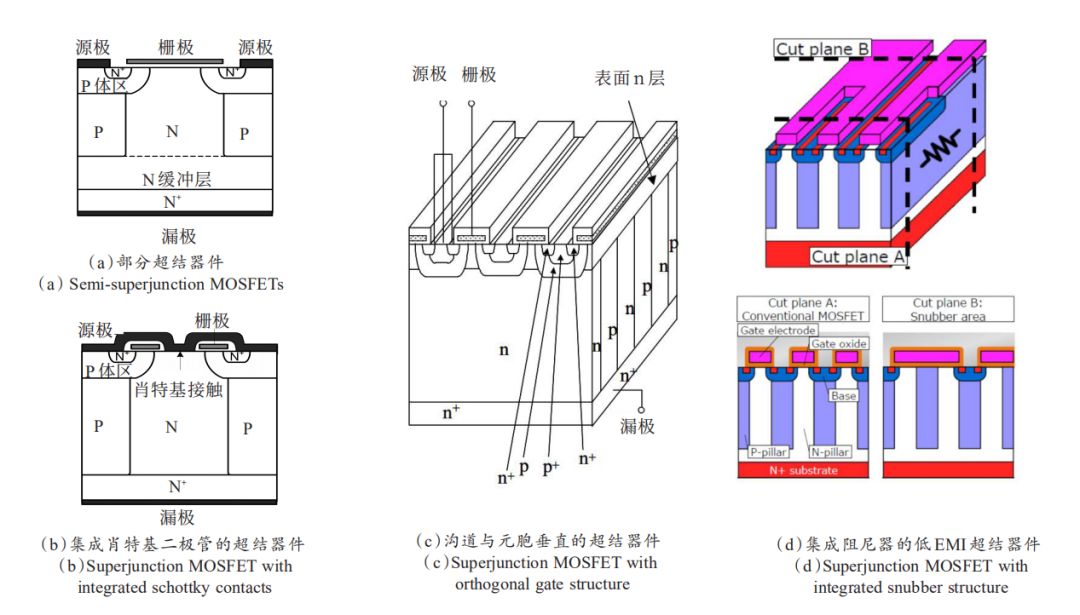

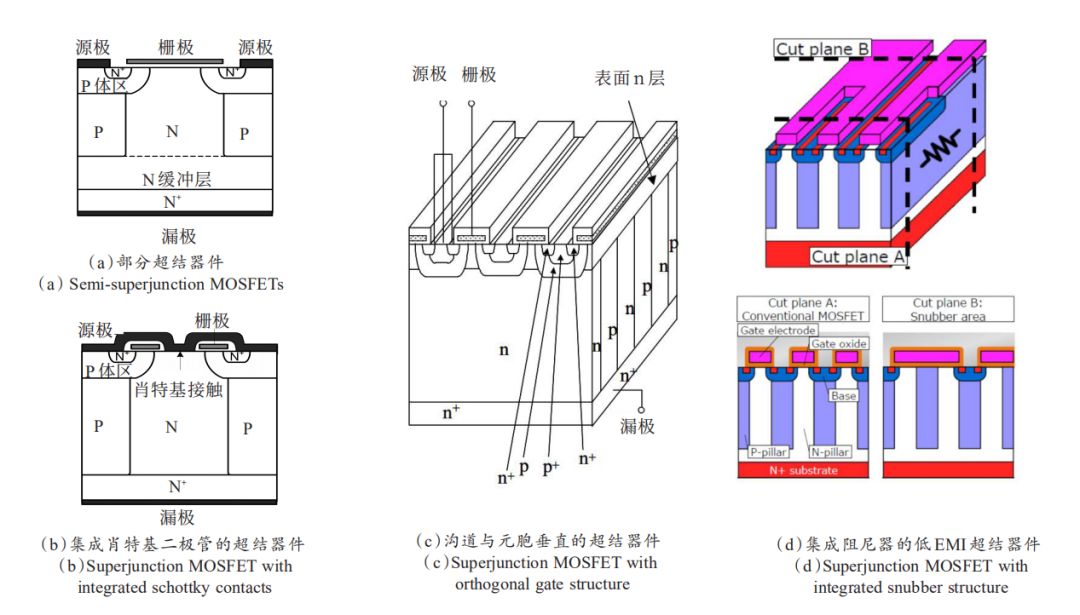

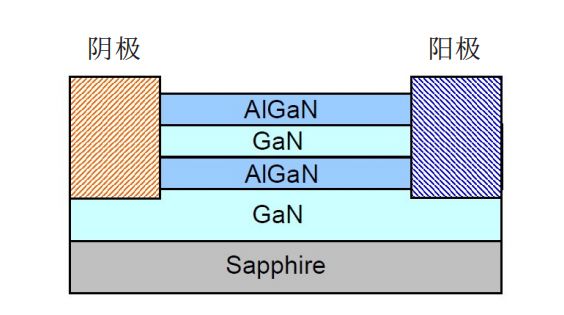

对超结功率

MOS

器件而言,大量新结构致力于如何利用兼容工艺改善器件特性,图

15

给出几种改善器件特性的典型结构。图

15

(

a

)为部分超结结构,超结器件给定元胞宽度下

N

区和

P

区的深宽比随器件

V

B

增加而增加,工艺难度增加。部分超结结构降低工艺难度,在相同深宽比条件下实现比全超结器件更低的

R

on,sp

且利于器件的反向恢复特性。

为了改善超结体二极管的反向恢复特性,通过集成肖特基二极管,提出如图

15

(

b

)所示的变形结构,通过肖特基结的反向抽取作用,削弱载流子存储效应;随着器件元胞宽度的进一步缩小,可能导致超结两个

P

条之间距离过小难以形成沟道区,因此提出如图

15

(

c

)所示的沟道与超结元胞相垂直的结构,该结构适用于窄元胞器件,减少沟道区工艺难度;此外还可以通过版图优化减少部分沟道区面积,以实现更低的电磁干扰(

EMI

)噪声。

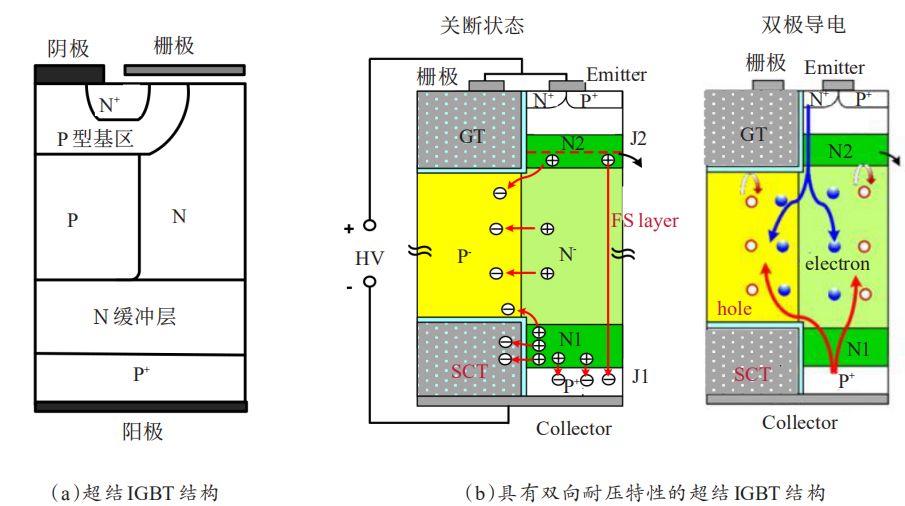

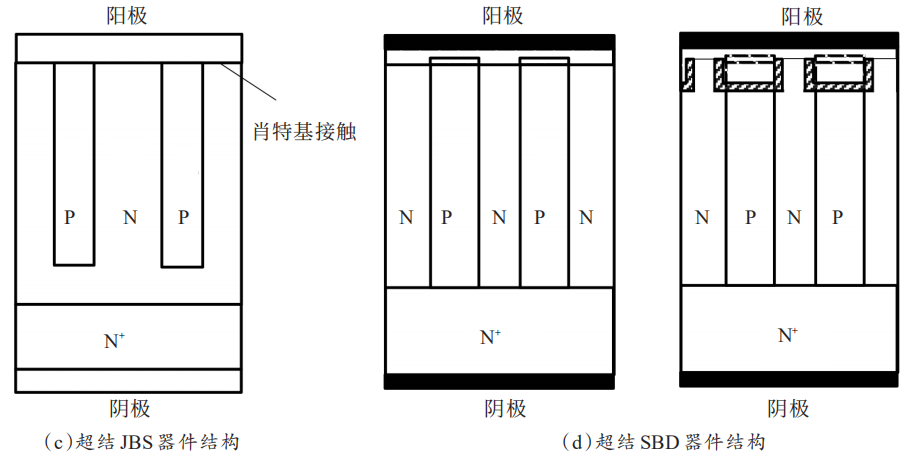

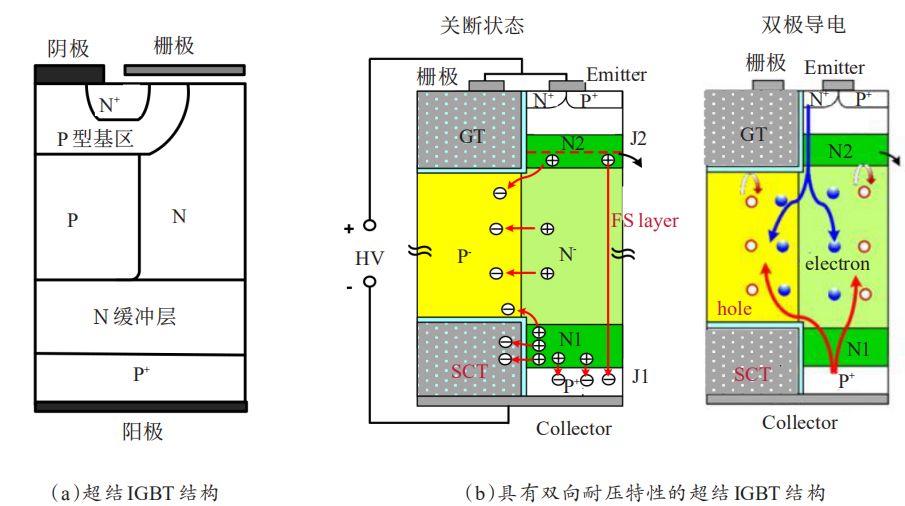

超结作为一种典型的结型耐压层结构,用于不同的器件可实现不同的功率半导体器件,典型结构如图

16

所示。图

16

(

a

)为超结

IGBT

结构,与传统

IGBT

相比,超结

IGBT

一方面通过电场调制缩小漂移区长度,另一方面还可以引入准单极传导模式,即大注入电子和空穴分别流经低阻的超结

N

区和

P

区,器件关断时通过内部

PN

结耗尽区扩展可以迅速抽取过剩载流子,实现快速关断;作者团队提出如图

16

(

b

)所示的具有双向耐压特性的超结

IGBT

结构,该结构打破了一般超结

IGBT

正向压降与超结区掺杂的依赖关系,实现开态双极高电导调制与关态准单极关断特性。如果将超结耐压层用于二极管结构,则形成图

16

(

c

)和

16

(

d

)所示的超结

junctionbarrier schottky rectifier

(

JBS

)和

schottky barrier diode

(

SBD

)器件结构,由于超结区的掺杂浓度很高,肖特基结开启后有更小的正向压降和更大的电流密度。同时由于反向阻断状态下

P

区之间的

N

型漂移区的耗尽层重叠形成势垒,使器件反向漏电流降低。超结

SBD

器件还可采用槽型电极结构来降低肖特基接触位置的电场,降低反向漏电。

图

16.

具有超结耐压层的新型功率半导体器件

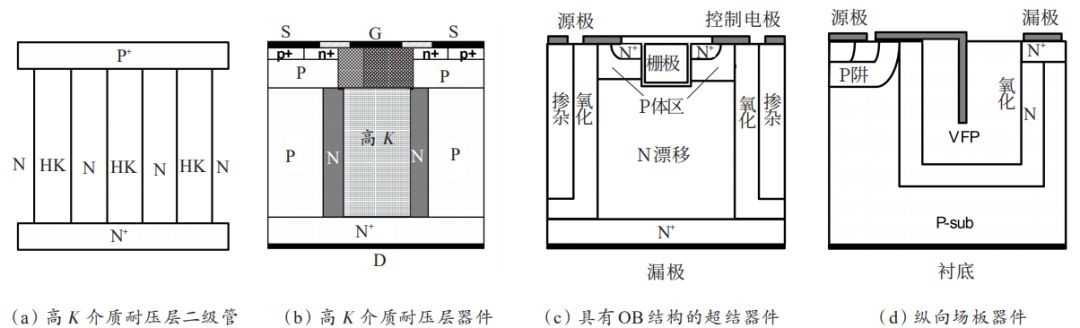

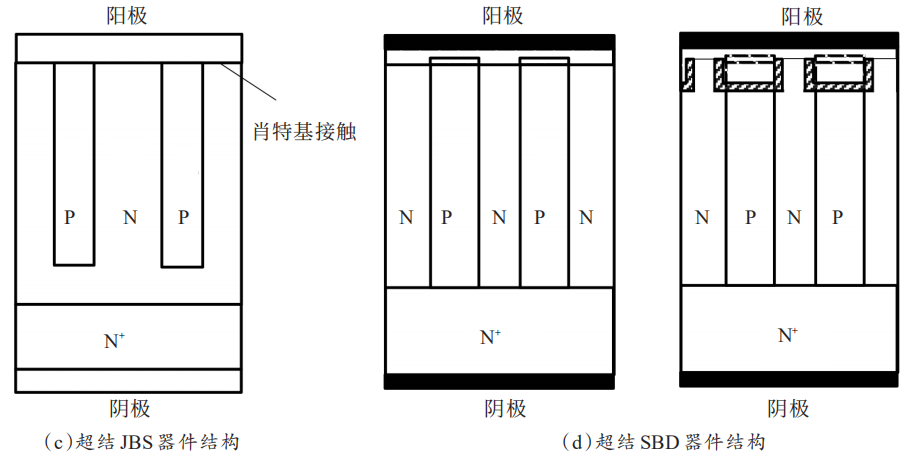

电荷平衡不仅可以通过

PN

结电离电荷实现,还可以通过金属绝缘层半导体(

metal insulator semiconductor

,

MIS

)介质耦合实现,如图

17

所示。其中图

17

(

a

)和图

17

(

b

)为具有高

K

介质的复合耐压层结构,器件耐压时大部分电通量通过高

K

介质流向表面,从而优化了硅层区电场;图

17

(

c

)和图

17

(

d

)为典型的体内场板结构,通过体内场板在耐压层内部引入电荷,与硅层电离电荷保持平衡,优化体内电场降低器件

R

on,sp

。

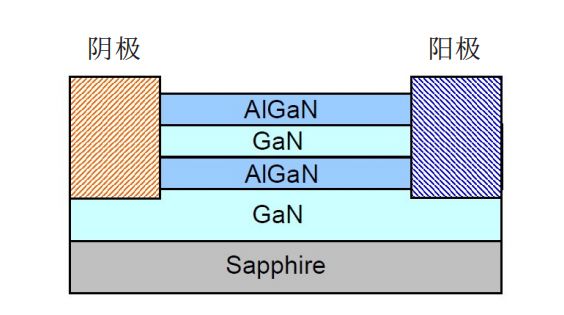

横向超结器件的发展主要集中在如何消除衬底辅助耗尽效应,典型方法有两种。第

1

种方法如图

18

所示,通过采用图

18

(

a

)蓝宝石衬底或者图

18

(

b

)刻蚀去除硅衬底,其共同点都是消除衬底电位对表面超结区的影响,解决纵向耐压低的问题。该方法可以很好地抑制衬底辅助耗尽效应,但具有工艺不兼容或者材料成本高的特点。

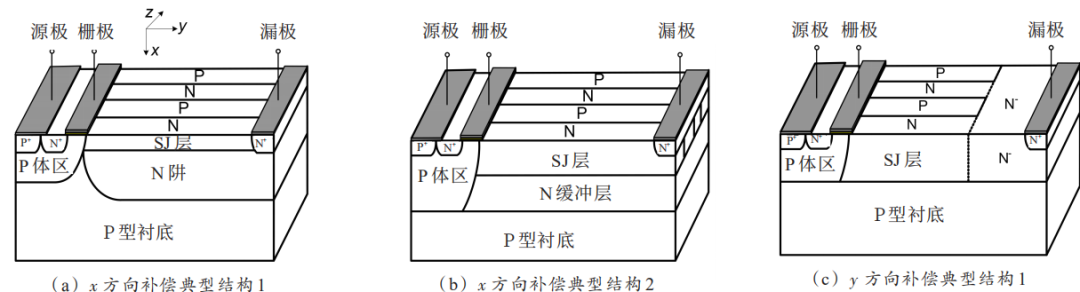

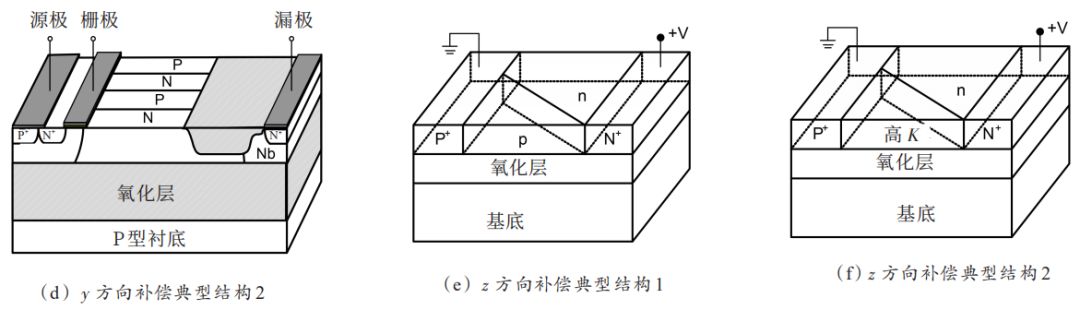

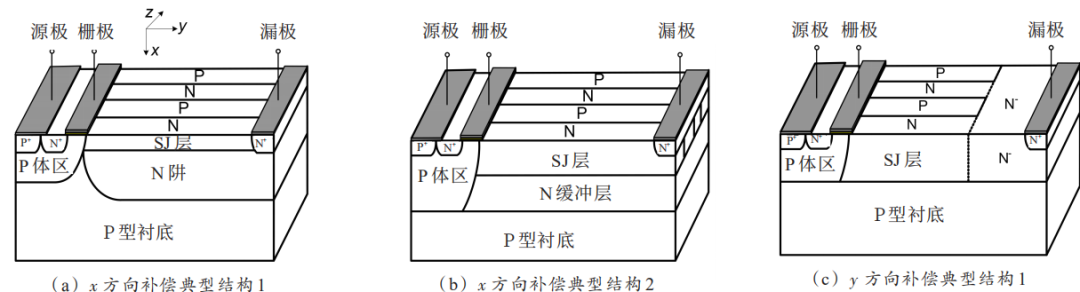

第

2

种方法如图

19

所示,其基本思想是电荷补偿,通过在耐压层中引入补偿电荷,与衬底电离电荷保持电荷平衡从而抑制衬底辅助耗尽效应的影响。从空间维度可以分为图

19

(

a

)、图

19

(

b

)

x

方向补偿,主要是通过在超结区下方添加深

N

阱或者

N

缓冲层的形式实现;图

19

(

c

)、图

19

(

d

)

y

方向补偿,超结区位于靠近源区,漏区为单一掺杂的

N

型掺杂,特别对

SOI

器件,为解决其耐压较低的问题,可以采用局部薄层结构;图

19

(

e

)、图

19

(

f

)

z

方向补偿,通过设计使超结

N

区和

P

区为非对称形状实现补偿,与纵向器件类似,

P

区亦可采用高

K

介质。

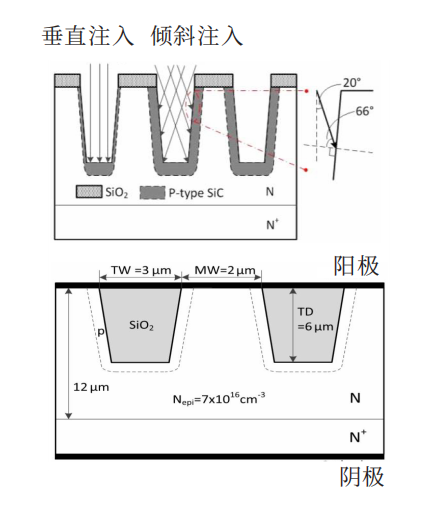

超结概念同样被应用到宽禁带半导体材料如

SiC

和

GaN

中,超结概念与理论完全适用,由于禁带宽度更大,相同深宽比条件下,宽禁带半导体超结器件对

R

on,sp

-

V

B

关系的贡献主要体现在系数项,可以降低约

3

个数量级,特别在超高压领域非常具有吸引力。

如图

20

所示是典型

SiC

基超结器件,采用与硅基类似的深槽刻蚀注入掺杂工艺实现,并且在槽内填充介质实现结型耐压层结构,该工艺比较容易实现较高深宽比的超结区。对

GaN

材料而言,可以通过异型掺杂形成一般结型耐压层结构,还可以利用叠层结构中电荷平衡极化电荷同时形成二维电子气与二维空穴气,典型结构如图

21

所示。器件开态时电子气和空穴气同时参与导电,降低器件导通电阻,关态时极化电荷自动满足电荷平衡,优化耐压层电场,从而形成新型的电荷平衡耐压层结构。

综上所述,超结发展历程如图

22

所示。超结结型耐压层高压低比导通电阻特性可实现高功率密度与低成本下的低损耗,理论上实现比导通电阻与耐压的从

R

on,sp

∝

V

B

2.5

关系降低到

R

on,sp ∝

V

B

1.32

甚至

R

on,sp ∝

V

B

1.03

关系,横向超结器件优化可由等效衬底模型统一描述。

随着元胞宽度进一步缩小,寄生

JFET

效应及齐纳击穿等变得更加显著,经笔者计算,齐纳击穿限制下硅基超结的条宽极限约为

0.1

~

0.2μm

;超结概念完全适用于

SiC

、

GaN

等其他半导体材料,突破对应“硅极限”关系;另一方面,超结概念还被拓展到

IGBT

、

SBD

等其他功率半导体器件中,实现电荷平衡的耐压层结构,并向着更高可靠性、更高开关速度的方向发展。

总结起来,目前在理论方面已经对超结器件做了较为深入的研究,获得了其理论最低

R

on,sp

。然而,在实验方面,超结器件特性仍有很大的提升空间,现有实验结果与

R

on,sp ∝

V

B

1.03

最低理论比导通电阻相比,在

W

为

5

~

10μm

范围内,

R

on,sp

可以再降低

20%

~

40%

,而在

W

宽度为

1

~

4μm

范围内,

R

on,sp

降低量达

60%

~

80%

,余量可观。横向超结器件是高压功率集成技术的重要发展方向,目前研究主要集中在如何消除衬底辅助耗尽效应提高耐压,然而超结本身优越的低阻特性尚待挖掘,特别采用具有纵向高深宽比的超结可以大幅降低

R

on,sp

,作者团队开发的具有

N-top

的横向超结器件以及多次注入形成的

NFD

横向超结器件,

R

on,sp

均较

Triple RESUF

器件更优。因此横向可集成超结器件有望成为

Triple RESUF

之后的下一代低阻可集成器件。

张波, 章文通, 蒲松,等. 超结功率半导体器件[J]. 微纳电子与智能制造, 2019, 1 (1): 5-19.

ZHANG Bo, ZHANG W T, PU S, et al. Superjunction power semiconductor devices[J]. Micro/nano Electronics and Intelligent Manufacturing, 2019, 1 (1): 5-19.

《微纳电子与智能制造》刊号:CN10-1594/TN

主办单位:北京市电子科技科技情报研究所 北京方略信息科技有限公司

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2224期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

“芯”系疫情

|AI

|TWS

|ARM

|

存储

|

CMOS|德州仪器|MEMS

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

图1.功率半导体简化结构

图1.功率半导体简化结构