来源:内容由半导体行业观察(icbank)编译,作者:Nadine Collaert ,比利时Leuven IMEC项目主任,谢谢。

对数据存储和处理(汽车应用)的需求越来越大。

多年来,人们一直在寻找一种结合了DRAM和NAND闪存优点的通用存储器,这种存储器成本低、性能可靠、用途广泛,有可能取代它们,满足带宽不断增长的需求并降低功耗。

在查看内存层次结构时(图1.3.6),并不缺少新的内存、材料和体系结构,这些新内存、材料和体系结构正在考虑取代内存层次结构中的各个层次。

虽然相变存储器(PCRAM或PCM)、电阻存储器(RRAM)、铁电场效应晶体管(FeFETs)和各种磁性存储器(MRAM)是过去几年研发的热点,但目前SRAM、DRAM和NAND闪存仍是主流。

为了取代SRAM L1缓存,结合了SRAM的速度和flflash的非易变性,考虑了Spin-Torque-Transfer MRAM (STT-MRAM)。

它是一种单晶体管结构,带有一个磁隧道结(MTJ)存储器单元,这可能是解决不断增加的对SRAM单元大小的不确定性的一个答案。

到目前为止,STT-MRAM对SRAM L3有一个清晰的价值定位,但它还不足以取代L1和L2缓存。

此外,由于共享的写/读行,内存单元遭受可靠性问题。

虽然仍处于研发阶段,Spin-Orbit-Torque MRAM (SOT-MRAM)在这方面可能是一个更好的选择。

SOT- mram在设备下集成了一个SOT层。

它通过向相邻的SOT层注入面内电流来诱导该层的切换。

读和写有两种不同的路径,其中读类似于STT,而写不是通过MTJ完成的。

这样做的好处是可以分别优化读和写路径。

通过在形成SOT的硬掩膜中集成铁磁体,可以在较低的功率下实现更快的开关。

另一种方法是将SRAM和逻辑这样的内存堆叠在一起。

这允许增加带宽,减少形式因素,并提高功率效率。

标准的3D通硅(TSV)和晶圆对晶圆的连接技术可以用于此目的,但也可以采用混合方法,即通过顺序3D处理实现设备与标准电池之间最短的互连,并通过标准3D技术在块级实现互连,从而在过程复杂性和功率性能增益方面进行最佳权衡。

它还允许为逻辑部分和SRAM部分(垂直设备或VFET)引入特定的设备架构和技术。

这就表明,VFET对于SRAM应用是非常有利的,这允许人们减小面积,尤其是当人们考虑堆叠它们时。

DRAM的微缩受到压力,在1nm处趋于稳定,要取代DRAM是非常困难的,大多数研究都集中在将DRAM堆叠到高带宽模块中,而该技术仍有望进一步缩放。

虽然没有取代NAND闪存和DRAM,但基于PCRAM(由英特尔于2015年推出)的3D XPoint在过去几年中获得了很多关注。

目前,128GB密度和20nm几何尺寸的两层堆叠架构,预计将在下一代进入四层堆叠,并将密度提高一倍。

FeFET是一种仍处于研发阶段的技术,在这种器件中,铁电材料被引入到标准MOSFET的栅极叠层中。

偶极子以非易失性方式改变晶体管的阈值电压。

虽然对于将其用作逻辑应用程序的steep-slope 设备仍存在激烈的争论,但它对存储器的好处更加明确:可伸缩性。

FJ能耗,读/写速度在10ns以内,高续航能力和保持性。

然而,从一个器件升级到需要以几乎相同的方式执行的数百万个存储单元,仍需要证明。

一般来说,甚至比逻辑应用程序更早,在内存中有一个持续的趋势,那就是使用3D技术,并将更多的层堆叠在一起以增加带宽。

最后,在研究冷存储器时,DNA或更一般的分子存储器是更具有探索性的途径之一。

这个想法是利用分子来储存大量的数据。

挑战与书写和阅读有关,在生命科学应用的基础上,可以使用特定的排序技术。

在过去的几年里,人工智能(AI)的应用蓬勃发展,从图像处理到语音识别,再到诊断疾病和预测天气状况。

这些应用程序通常需要在云中进行高耗能的数据处理。

大多数实现基于GPU,有些基于FPGA,很少有基于专门为深度学习而构建的ASIC。

另一方面,与延迟、电力效率和隐私相关的问题要求这种处理在边缘完成,电池驱动的物联网(IoT)设备对能源效率和消耗提出了很高的要求,有时甚至在毫瓦级。

对于监督学习,参数仍然可以在云端进行处理,但是推理,决策需要交给传感器。

这需要在深度学习过程中训练记忆层,通过这些连续的层获取存储在记忆中的重复加权数据。

每个存储器阵列表示神经网络的一层。

将数据放在处理器附近可以减少延迟和功耗,这是内存中计算的前提。

为了存储学习权重的值,使用了模拟的非易失性设备,如电阻RAM (RRAM)技术,它曾被视为NAND闪存的替代品,但在人工智能环境中被重新定位为专门的人工智能存储技术。

在这种情况下,学习到的权值被编码到各个设备的电导中,电导随着写的数量的增加而变化,输入值被设置为RRAM阵列的字线(WL)电压。

然后,单元格的电流是权重和输入值的乘积,单词行的电流将是该行中单元格电流的总和。

这是在不改变权值的情况下实现卷积的有效方法。

一般来说,模拟计算只有在允许较低的精度、增加的可变性和系统误差的情况下才有意义。

当在足够高的电阻水平下操作时,这些典型的光纤RRAM单元中的变化通常太大,因此也在考虑其他存储器技术,如基于InGaZnO(IGZO)的2T-1C DRAM、SOT-MRAM和具有分离写入路径的PCM。

最后,利用自旋/电子作为量子信息载体并有望解决棘手计算问题的量子计算,直到几年前还只是物理学家的一个梦想。

在社区中已经获得了巨大的动力来推动这种全新的计算模式,其中的基本组成部分是q-bit,将其推向下一个层次,并使其成为技术现实。

令人鼓舞的是,更多的努力正在开发基于si的平台,用于快速和统计相关的寻路和基准测试,以解决量子计算中的关键挑战。

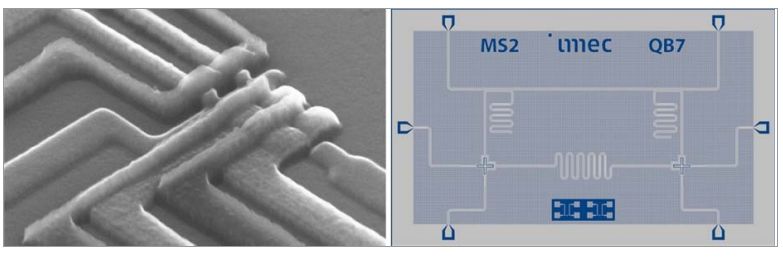

图:

(左)倾斜的Si q-bit实现的SEM图片和(右)超导谐振器的俯视图图片。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2226期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

“芯”系疫情

|AI

|TWS

|ARM

|

存储

|

CMOS|德州仪器|MEMS

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!