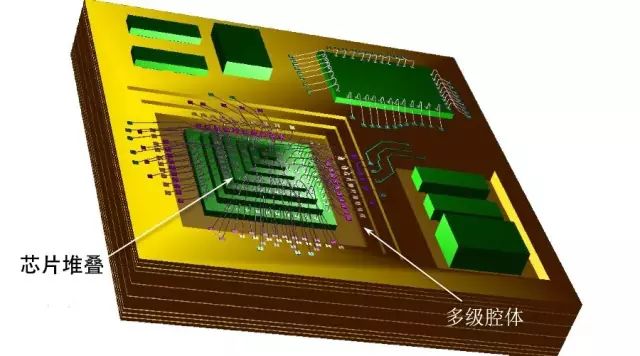

芯片堆叠技术在SiP中的应用

来源:内容来自公众号「SiP系统级封装技术」,作者:李扬,谢谢。

芯片堆叠技术在SiP中应用的非常普遍,通过芯片堆叠可以有效降低SiP基板的面积,缩小封装体积。

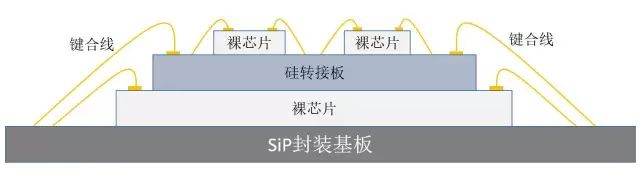

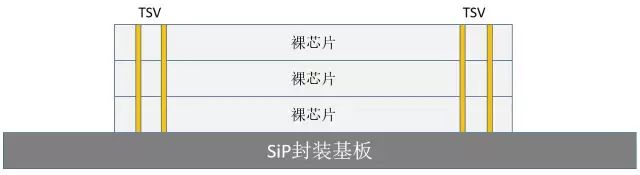

目前来看,芯片堆叠的主要形式有四种:金字塔型堆叠,悬臂型堆叠,并排型堆叠,硅通孔TSV型堆叠。

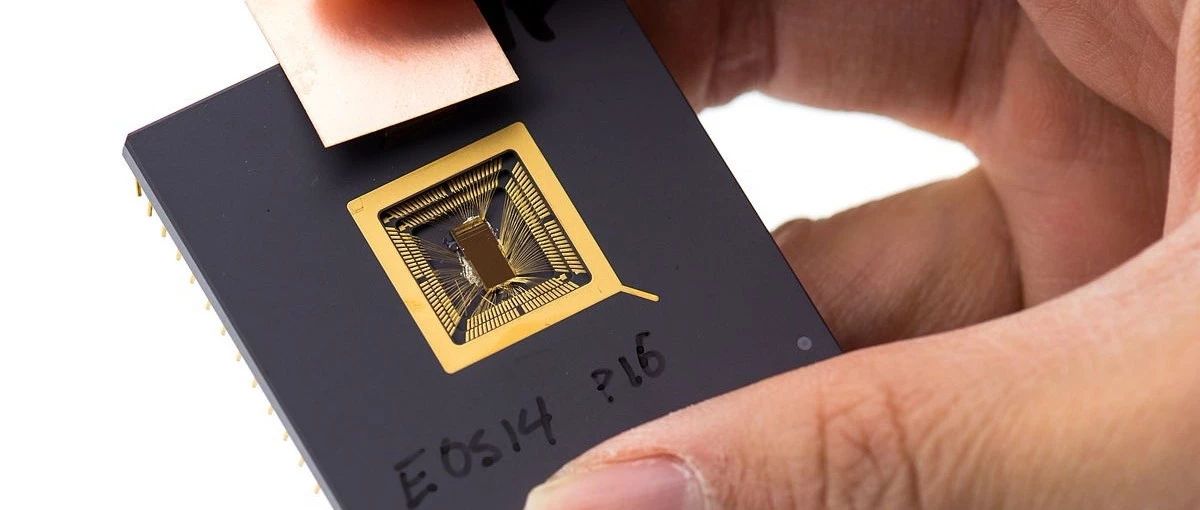

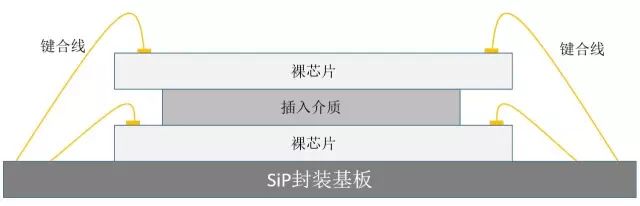

为什么芯片可以进行堆叠呢?这里面我们讲的主要是未经过封装的裸芯片。曾经有用户问我,封装好的芯片可不可以进行堆叠呢?一般来说是不可以的,因为封装好的芯片引脚在下表面直接焊接到基板上,而裸芯片的引脚一般在芯片上表面,通过键合的方式连接到基板。正是由于裸芯片引脚在上方,和基板的连接方式比较灵活,才有了芯片堆叠的可行性,参看下图。

金字塔型堆叠

悬臂型堆叠

并排型堆叠

硅通孔TSV型堆叠

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2228期内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

“芯”系疫情 |AI |TWS |ARM | 存储 | CMOS|德州仪器|MEMS

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻