半导体的3D时代

2020-03-06

14:00:15

来源: 半导体行业观察

每年在SPIE高级光刻会议召开之前的星期日,尼康都会举行其Litho Vision研讨会。我有幸连续第三年受邀发言,不幸的是,由于新冠肺炎的影响,该活动不得不取消。但是到活动宣布取消时,我已经完成了演讲文稿,所以在此分享。

我演讲的题目是“ Economics in the 3D Era”。在演讲中,我将讨论三个主要的行业领域,即3D NAND,逻辑和DRAM。对于每个部分,我都会讨论当前的状态,然后进入技术,掩模数量,密度和成本预测的各自路线图。所有状态和预测都将针对公司,并涵盖每个细分市场的领导者。此演示文稿的所有数据,技术,密度,掩模数量和成本预测均来自我们的 IC Knowledge–战略成本和价格模型– 2020 –修订版00模型。该模型基本上是一份详细的行业路线图,可以模拟成本,设备和材料要求。

3D NAND是业界最“ 3D”的细分市场,其层堆叠技术可通过在竖直方向上添加层来提高密度。

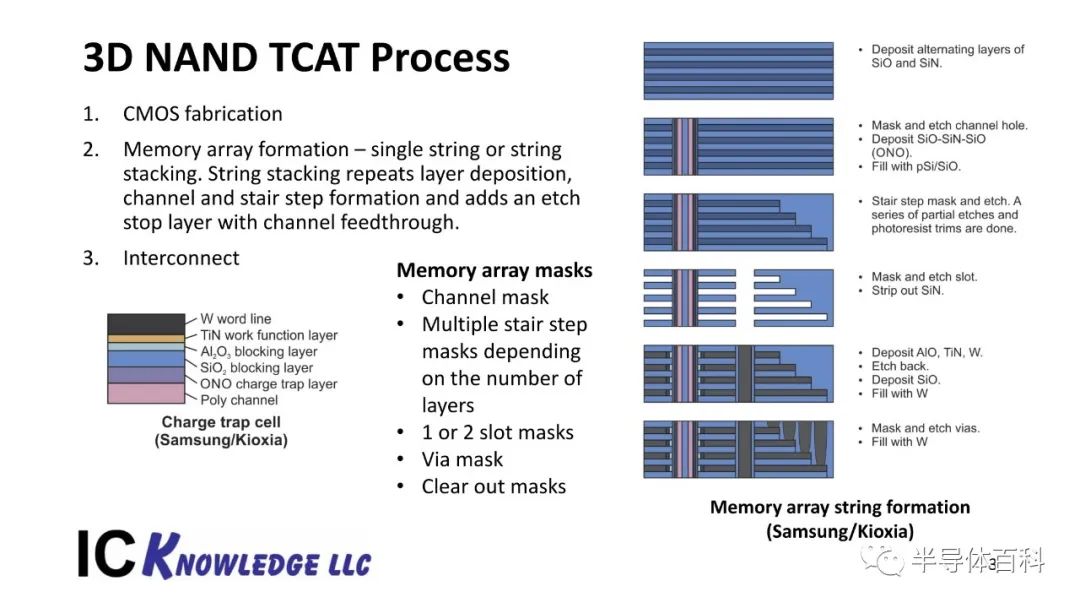

在3D NAND领域,市场领导者是三星,他们使用的是TCAT制程。市场上排名第二的是Kioxia(前身为Toshiba Memory),他们使用的工艺与三星基本相同。美光也正在采用电荷陷阱技术,我们希望其工艺类似于TCAT制程,从而使TCAT制程能够代表行业大多数。SK海力士使用不同的制程,但在许多关键要素上与TCAT制程相同。唯一不使用电荷陷阱技术的公司是英特尔美光公司,但由于英特尔和美光已经在3D NAND领域分道扬,,英特尔将是唯一一家仍然采用浮栅技术的公司。

-

制作CMOS –

这些CMOS用于写入,读取和擦除比特信息。最初,除英特尔-美光公司外,每家公司都在存储器阵列外围制造CMOS,而英特尔-美光公司在存储器阵列下方制造一些CMOS。随着时间的流逝,其他公司已经迁移到阵列下的CMOS,我们希望在几代之内,所有公司都将迁移到阵列下的CMOS,因为它提供了更好的裸片面积利用率。

-

制作存储阵列–

对于电荷陷阱技术,可通过沉积氧化物和氮化物的交替层来进行阵列制造。然后向下蚀刻穿过各层的沟道孔,并重新填充氧化硅/氮化硅/氧化硅(ONO)层,多晶硅管(沟道)并填充氧化物。然后使用光刻-蚀刻-收缩-蚀刻方法制造阶梯。然后穿过阵列向下蚀刻狭隙,并蚀刻掉氮化物膜。然后沉积阻挡层和钨以填充蚀刻氮化物的水平开口。最后,将通孔蚀刻停止到到钨的水平片上。

-

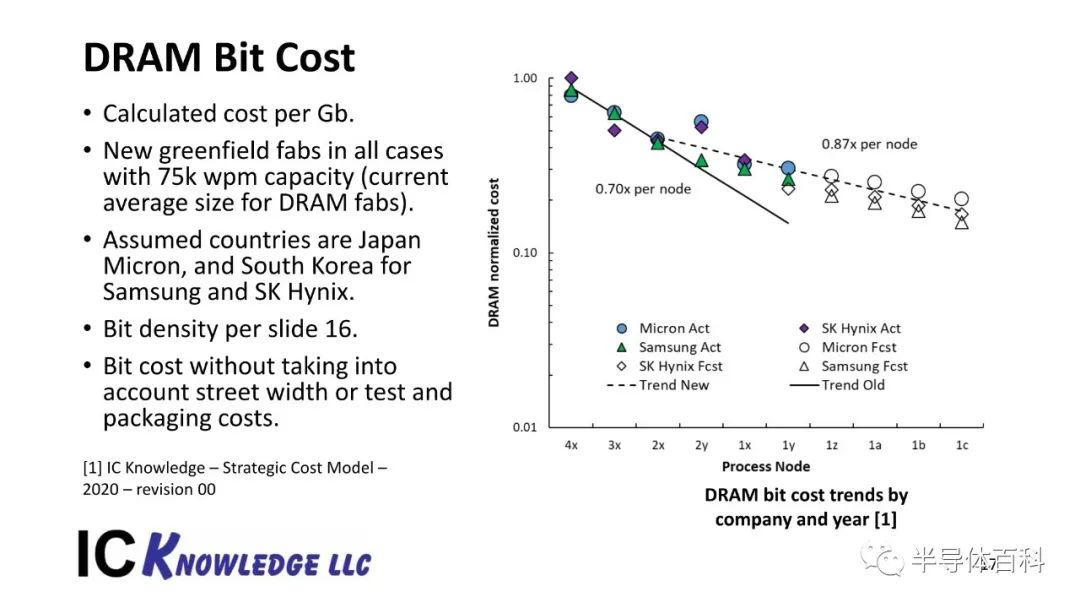

互连–

CMOS和存储器阵列然后互连。对于阵列下的CMOS,一些互连发生在存储器阵列制造之前。

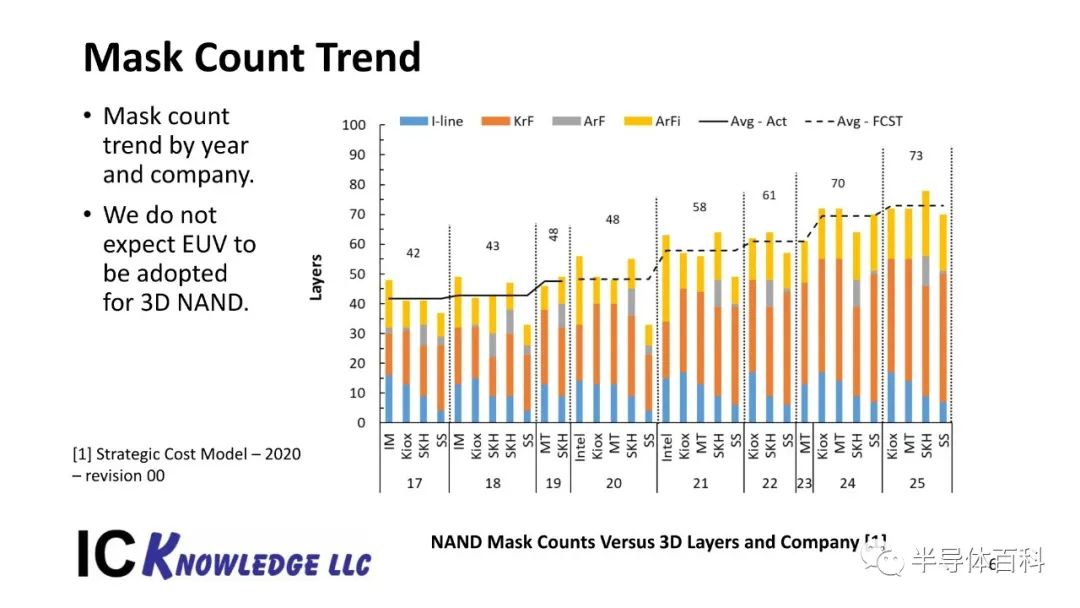

这种技术掩模使用效率非常高,因为可以用若干张掩模对很多层进行构图。整个制程只需要一张沟道孔掩模,若干张阶梯掩模(取决于层数和制程需求)。在早期的工艺中,单张掩模可以制作大约8层,但是如今某些工艺可以通过单张掩模做到32层。狭缝(slot)蚀刻需要一张掩模,有时还有另一个浅狭缝需要一张掩模,最后接触通孔也需要一张掩模。

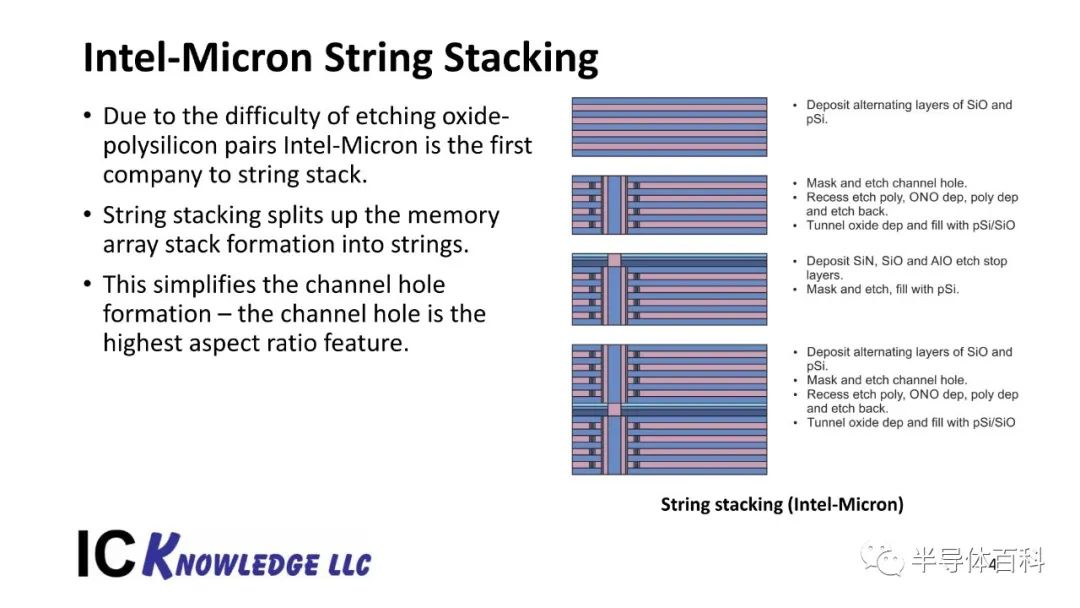

沟道孔蚀刻是非常难的高深宽比(HAR)蚀刻,一旦达到一定的最大层数,该制程就必须以所谓的“串堆叠”(string stacking)方式分成多个“串”(存储单元串)。基本上,在串堆叠中,沉积一组层,应用掩模,蚀刻,填充沟道。然后沉积另一组层,光刻,蚀刻和填充。理论上,这可以循环很多次。英特尔-美光科技公司使用浮栅工艺,该工艺使用的氧化硅/多晶硅层比氧化硅/氮化硅层更难蚀刻,所以他们是最早使用串堆叠技术的。

每家公司都有自己的沟道孔蚀刻方法,并且在串堆叠方面有自己的限制。因为使用氧化多晶硅层,所以Intel-Micron通过堆叠2次32层的串制作了64层芯片,然后通过堆叠2次48层的串量产了96层芯片。英特尔已经发布了144层存储芯片,预计将是3次堆叠48层。SK Hynix到72层时开始串堆叠,Kioxia是96层开始堆叠(都是电荷陷阱技术,都是氧化硅/氮化硅层)。三星是最后一个串堆叠技术的支持者,他们量产了一款92层的单串芯片,并发布了一款128层的单串器件。

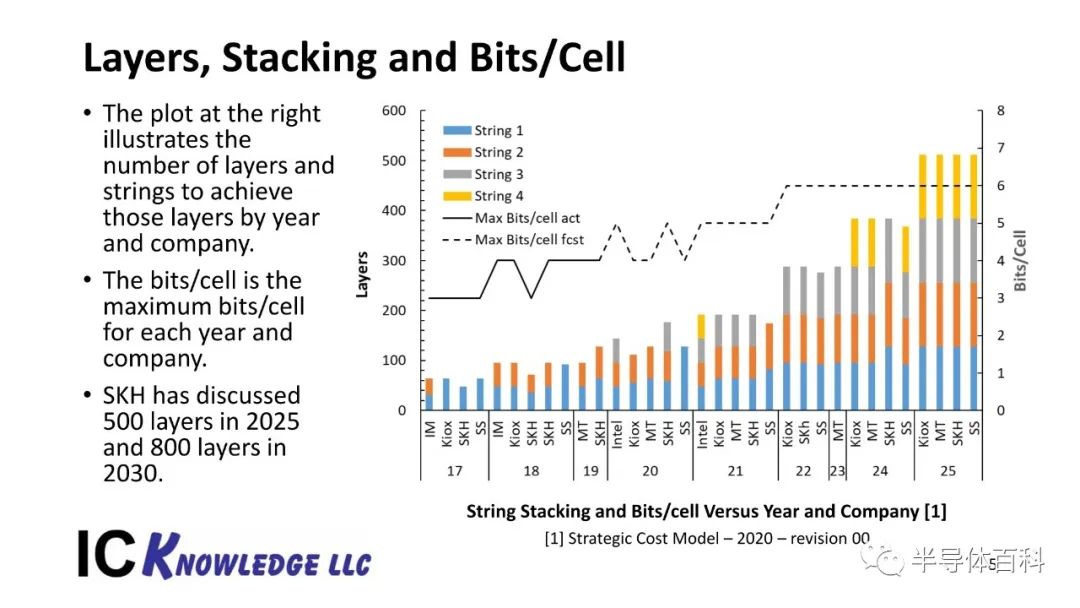

通过在一个单元中存储多个比特,也可以提高存储密度。NAND闪存已从单层单元(SLC)到2个比特的多层单元(MLC),再到3比特的三层单元(TLC),再到4比特的四层单元(QLC)。业界现在正准备推出5个比特的五层单元(PLC),甚至还有关于6比特的6层单元(HLC)的讨论。增加每个单元的比特数有助于提高密度,但收益却在降低,从SLC到MLC的比特数是2倍,从MLC到TLC的比特数是1.5x,TLC到QLC的比特数是1.33x,从QLC到PLC的比特数是1.25倍。如果业界达到了PLC,则接下来到HLC的比特数将只是1.20倍。

图3在左轴上显示了按年份和公司分类的串堆叠,在右轴上显示了每个单元的最大比特数。

图4展示了我们对按曝光类型,公司和年份划分的掩模数量的分析。虚线是每年的平均掩模数,从2017年的42张增加到2025年的73张,这与层数从2017年的平均60个增加到2025年的512个相对应。换句话说,掩模数量仅增加1.7倍就增加了8.5倍的层数以突出3D NAND工艺的掩模使用效率。

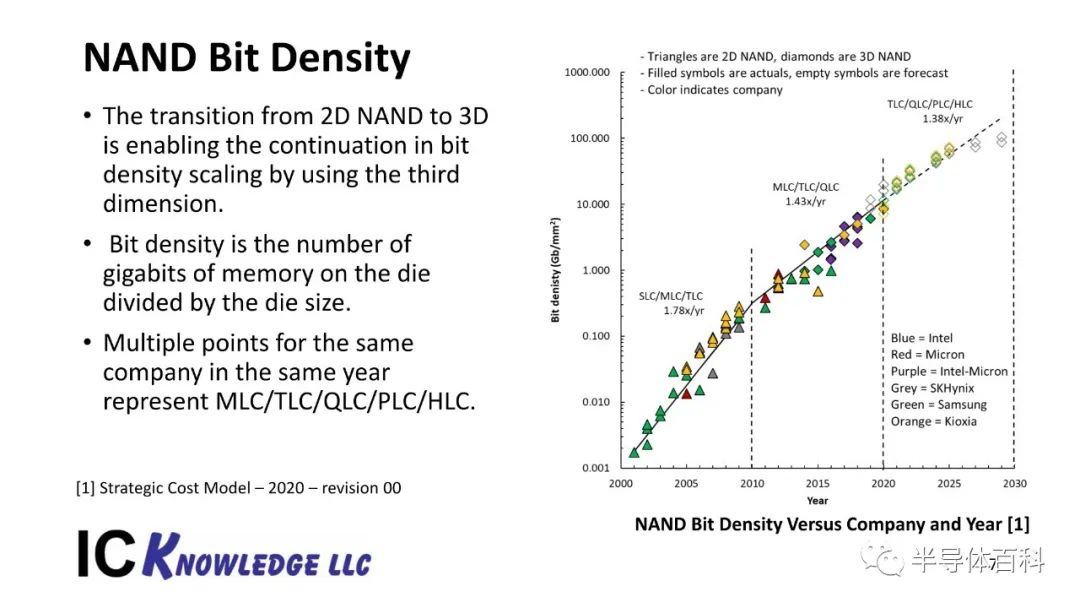

图5展示了各家公司2D NAND和3D NAND的实际和预测比特密度随年份变化的趋势。这里是整个芯片的比特密度,即芯片的容量除以芯片的尺寸。

从2000年到2010年,在光刻微缩的推动下,2D NAND比特密度每年增长1.78倍。大约在2010年左右,继续缩小2D NAND的难度导致增长减慢至1.43倍,直到2015年左右3D NAND成为驱动力并继续以每年1.43倍的速度增长。我们预计从2020年到2025年的年增长率将略有下降,为1.38倍。与去年相比,这是我们的预测的一项改进,因为我们看到这些公司推动该技术的速度超出了我们最初的预期。最后,SK海力士谈到了2025年的500层和2030年的800层,导致2025年之后的速度进一步放缓。

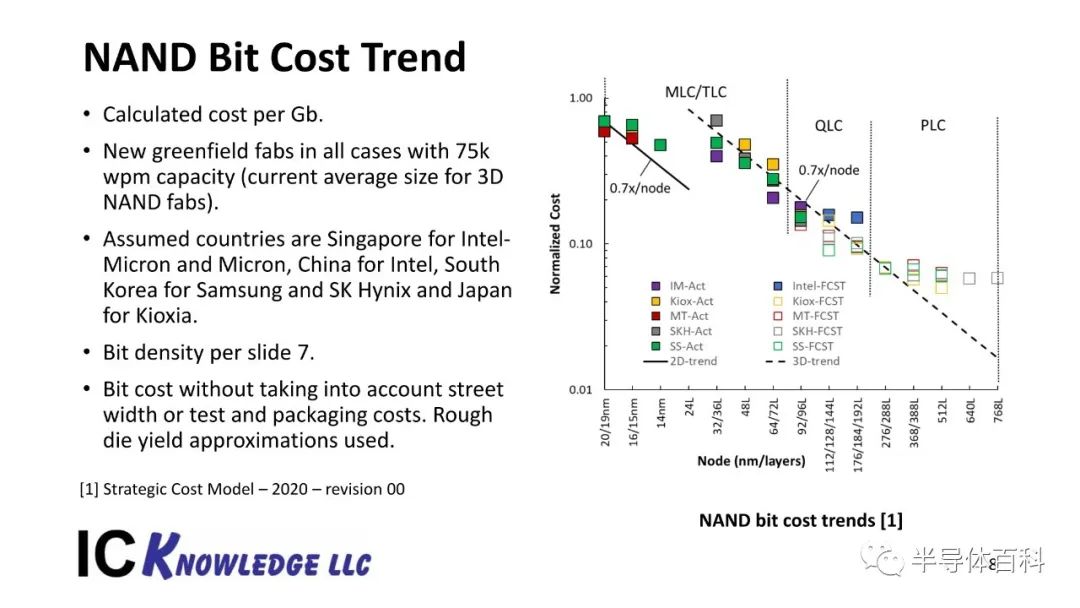

在该图中,我们采用了使用战略成本和价格模型计算出的晶圆成本,并将其与图5中的位密度相结合以产生单位比特成本趋势。在所有情况下,这些晶圆厂都是新建的月产能75,000片晶圆的工厂,因为这是NAND晶圆厂在2020年的平均产能。这些晶圆厂对应所在的国家分别是新加坡-英特尔美光,英特尔-中国,Kioxia-日本,三星和SK海力士-韩国。这些计算不包括封装和测试成本,不考虑划片槽宽度,并且仅包含粗略的芯片良率假设。

图表中的前三个节点是2D NAND,每个节点的成本趋势为0.7倍。随着向3D NAND的过渡,大多数公司的比特成本最初都增加了,但现在已降至2D NAND比特成本以下,并且每个节点的趋势为0.7倍,直到大约300到400层。我们预计单位比特成本会趋于平缓,除非在工艺或设备效率方面取得一些突破,否则该技术将面临成本极限。

对于3D NAND“节点”,可以轻松地根据物理层数进行定义,对于DRAM节点一般采用有源区的半节距,而逻辑节点几乎是公司营销人员称之为多少就是多少。

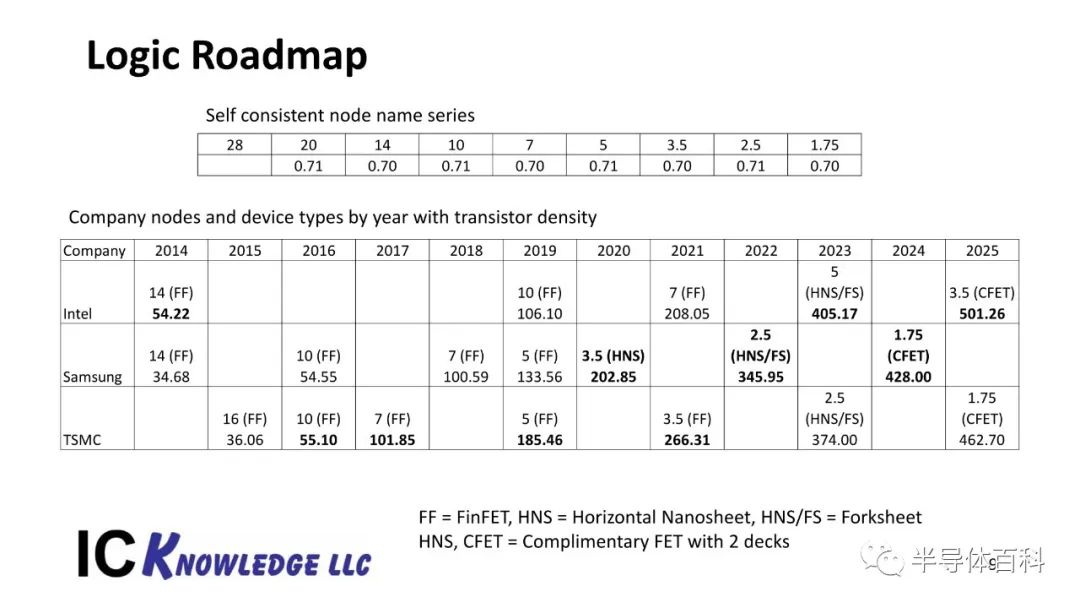

由于FinFET是3D结构,因此某些人认为当前的FinFET前沿工艺是3D,但在本次讨论中,我们认为3D是指器件堆叠,即允许堆叠多个有源层以创建器件堆叠的情况。在这种情况下,一旦采用CFET,3D逻辑器件将真正出现。图7列出了追求最新技术的3家公司的节点路线图。

由于英特尔与代工厂之间的分裂,此图中的节点比较变得复杂。英特尔遵循经典的节点名称,即45nm,32nm,22nm,14nm,而代工厂遵循的是“新”节点名称,分别为40nm,28nm,20nm,14nm。此外,英特尔在每个节点上微缩更多,因此Intel 14nm的密度与代工厂10nm类似,Intel 10nm的密度与代工厂7nm类似。

在图的顶部,我概述了基于交替的0.71和0.70倍微缩得到的节点名称系列。在图的底部,我按公司和年份列出了每个节点的晶体管密度。如前所述,晶体管密度是基于NAND和Flipflop单元的权重计算的。括号中每个节点的旁边是FF(FinFET),HNS(水平纳米片),HNS / FS(Forksheet,基于Imec的工作来提高密度)和CFET(互补堆叠的FET,其中nFET和pFET是垂直堆叠)。CFET量产之时,就是逻辑微缩从基于单层的微缩成为真正的3D解决方案之日,原则上CFET可以通过添加更多层来继续进行微缩。

图中粗体表示领先的密度或技术。2014年,英特尔凭借其14纳米工艺在密度上取得了领先地位。台积电在2016年以10纳米制程占据密度领先地位,并在2017年以7纳米制程保持领先地位。台积电和三星在7nm处的密度相似,但要达到5nm,台积电的微缩率要比三星大得多,2019年,台积电以其5nm技术保持工艺密度领先。如果三星在2020年实现HNS技术(我们称之为3.5纳米节点),那么他们可能会在密度上领先,并成为第一家制造HNS的公司。在2021年,TSMC的3.5纳米节点(我们称之为)可能会帮助他们返回到密度领先位置。如果英特尔能够实现他们通常目标的那种两年一次微缩的速度,我们相信他们可以在2023年在采用5纳米工艺时重新取得密度方面的领先。

图8给出了这些逻辑制程的掩模数量。EUV的引入减少了掩模数,如果没有EUV,我们可能会在此图表上看到100个以上的掩模。正如我们对NAND掩膜计数图所做的那样,虚线是平均掩膜数。我们还基于“相似”密度对工艺进行了分组,例如,将Intel 14nm与代工厂10nm工艺结合在一起,将Intel 10nm与代工厂7nm工艺结合在一起。

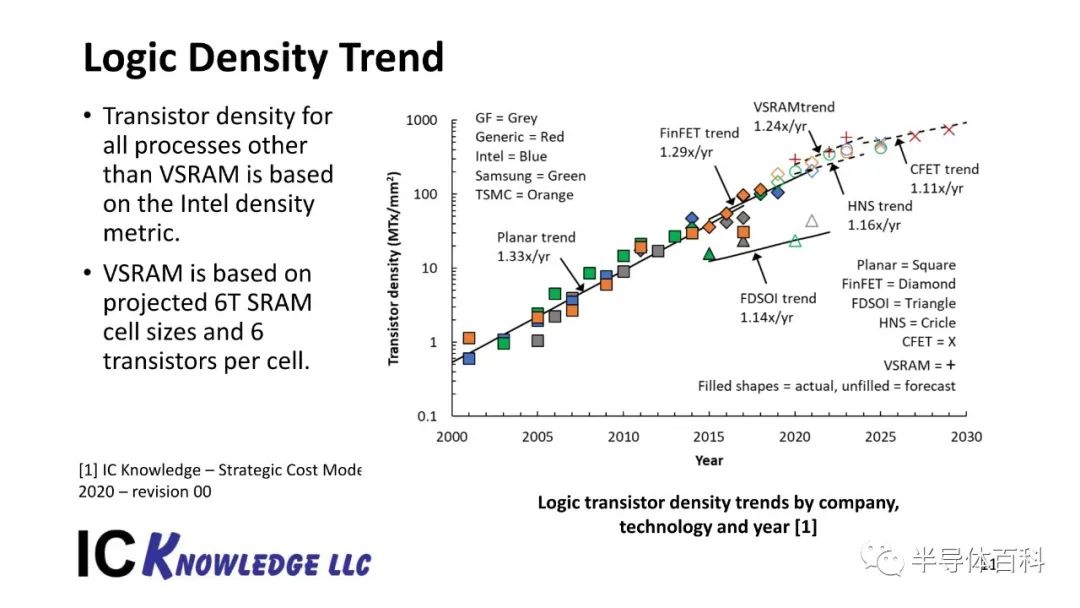

图9显示了基于前面提到的NAND /D触发器加权度量的每平方毫米晶体管的逻辑密度。

此图表上绘制了六种类型的制程。直到2014年左右,平面晶体管还是主要的前沿逻辑工艺,其密度每年提高1.33倍,FinFET接管了前沿技术,密度每年提高1.29倍。与FinFET并行,我们已经看到了FDSOI工艺的引入。FDSOI提供了更简单的工艺,更低的设计成本以及更好的模拟,RF和功耗,但无法与FinFET竞争密度或原始性能。当HNS从FinFET接管后,我们预计密度的提高速度将进一步放缓至每年1.16倍,最终CFET将接管并以每年1.11倍的速度增加密度。我们还根据IMEC的工作绘制了由垂直晶体管生产的SRAM,这些SRAM可能为高速缓存chiplet提供有效的解决方案。

图10通过将我们的战略成本和价格模型中的晶圆成本估算值与图9中的晶体管密度相结合,得出了每十亿个晶体管的成本。所有晶圆厂都是新建的工厂,每月产能为35,000片晶圆,因为这是将在2020年建成的逻辑晶圆厂的平均产能。晶圆厂与国家/地区对应关系为,GLOBALFOUNDRIES-德国(除14nm在美国),英特尔-美国(除以色列的10nm芯片),台积电-台湾,三星-韩国。

该图不包括掩模组或设计成本摊销,因此,在降低每个晶体管的制造成本的同时,能够使用这些技术的设计数量仅限于大批量产品。该图不包括任何封装测试或良率影响。

从130纳米降低到i32 / f28(英特尔32纳米/代工厂28纳米)每节点成本下降0.6倍,然后从i22 / f20到f16 / f14节点,由于代工厂决定为了FinFET而不微缩太多,成本降低速度减慢了。这种放缓导致许多业内人士错误地预测了成本削减的终结。从f16 / f14节点到i5 / f2.5节点,我们预计成本将以每节点0.72倍的速度降低,然后减速至每节点0.87倍。g1.25和g0.9节点分别是具有3个和4个堆叠层的通用CFET制程。

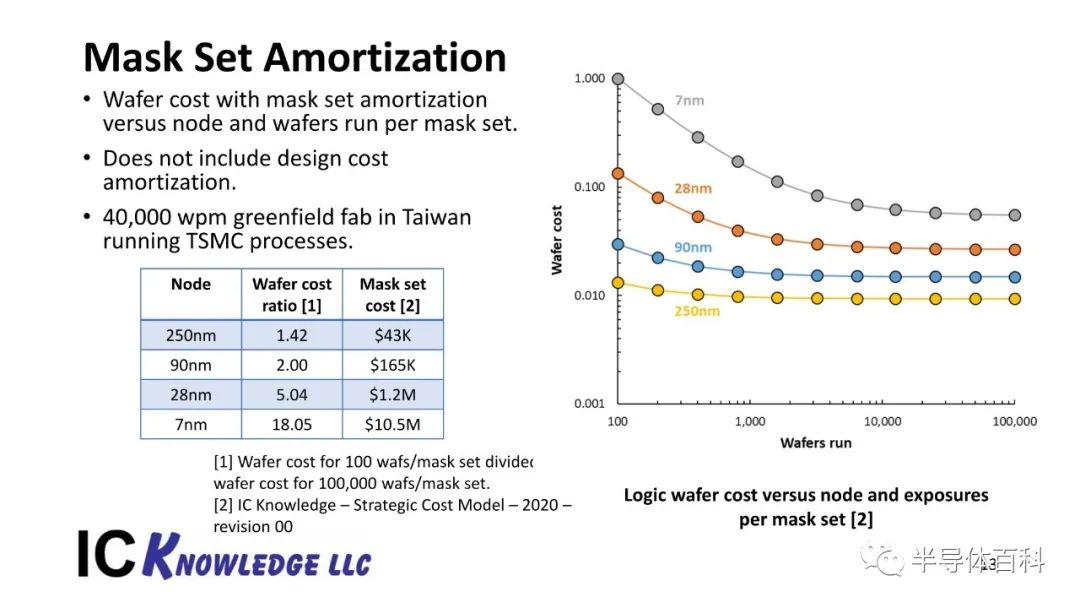

图11中的晶圆成本是基于台湾新建的晶圆厂,每月生产40,000片晶圆。摊销仅是掩模组,不包括设计成本。

该表列出了2020年250nm,90nm,28nm和7nm掩模组的掩模成本。请注意,这些掩模组在介绍时比较昂贵。掩模组成本是在一定数量的晶圆上摊销的,其标准化成本如图所示。在该表中,晶片成本比率是在掩模组上运行的100个晶片的摊销成本,除以在掩模组上运行的100,000个晶片的摊销成本。

从该图和表中,我们可以看到,掩模组摊销在250nm(比例为1.42x)时影响较小,而在7nm(比例为18.05x)时影响较大。设计成本摊销甚至更糟。最重要的是,设计和掩模组成本在先进节点是如此之高,以至于只有大批量产品才能吸收由此产生的摊销费用。

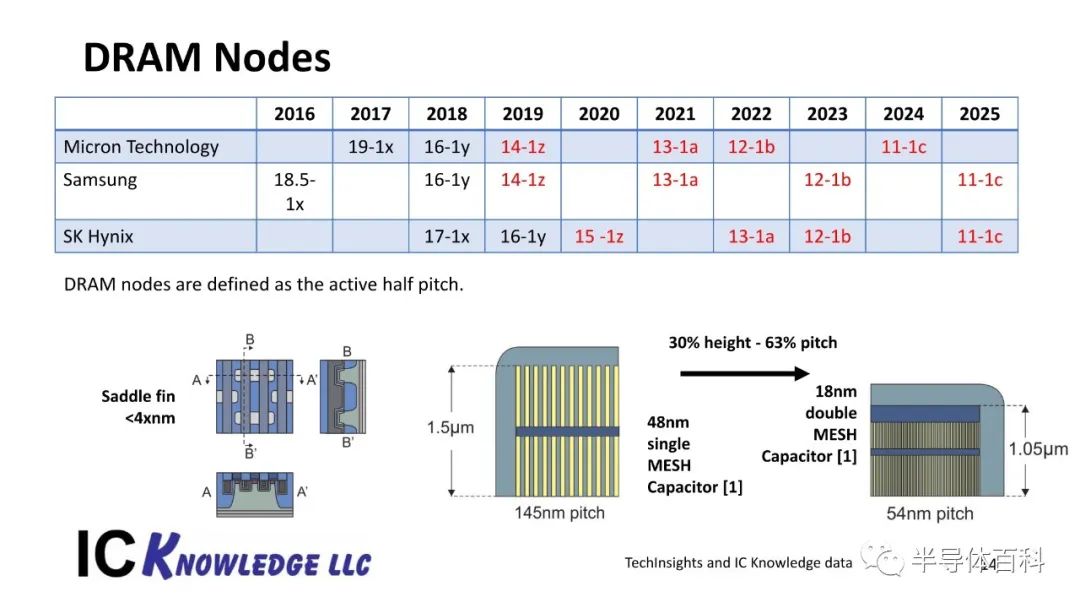

前沿DRAM的电容器结构是高深宽比的“ 3D”器件,与当前的逻辑器件类似,DRAM没有通过堆叠有源元件进行微缩。图12在顶部表中按公司列出了DRAM节点,在图底部是一些关键结构图。

随着DRAM节点前进到低于4x nm的水平,具有埋入式字线的埋入式鞍形鳍访问晶体管开始使用(见图左下角)。右下角展示了电容器结构向具有两个氮化硅“ MESH”支撑层的高深宽比结构的发展过程。DRAM电容器结构正达到该技术的机械稳定性极限,并且介电常数k值也停滞不前,DRAM微缩比例正演变为每个节点仅微缩一个纳米。

从图13可以看出,从2x到2y代,掩模数量有了很大的增长。性能和功耗要求推动了这种增加,因为外围逻辑电路需要更多晶体管类型和阈值电压。

在1x节点上,三星是第一家将EUV引入DRAM生产的公司,EUV层的数量在1a,1b和1c节点上有所增加。SK海力士也有望实施EUV,我们目前不希望美光实施EUV。

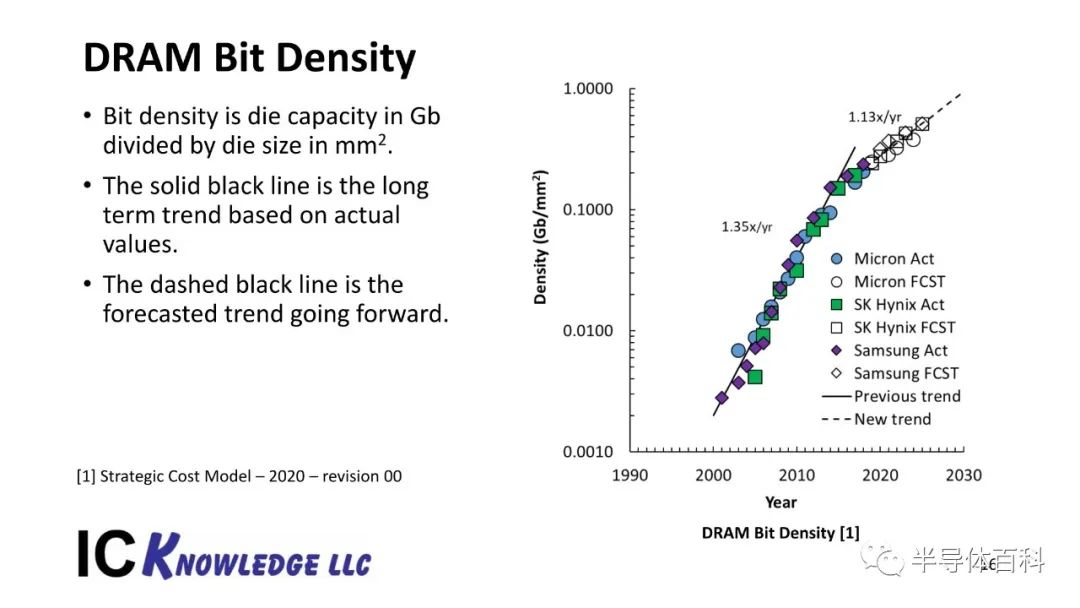

在图14中,比特密度是产品容量除以以平方毫米为单位的芯片尺寸。图14可以看出,从2105年左右开始,比特密度的增长开始放缓。目前,DRAM的比特密度受到电容器自身的限制,目前尚不清楚解决方案是什么。长期来看,可能需要一种新型的内存来代替DRAM。DRAM要求具有较高耐久性和相对较快的访问速度,目前,MRAM和FeRAM似乎是唯一有可能满足速度和耐久性要求的选择。由于MRAM需要相对较高的电流来切换,因此需要较大的选择器晶体管,从而限制了将MRAM缩小至具有竞争力的密度和成本的能力。FeRAM也是一种潜在的替代品,在IMEC等地方引起了很多关注。

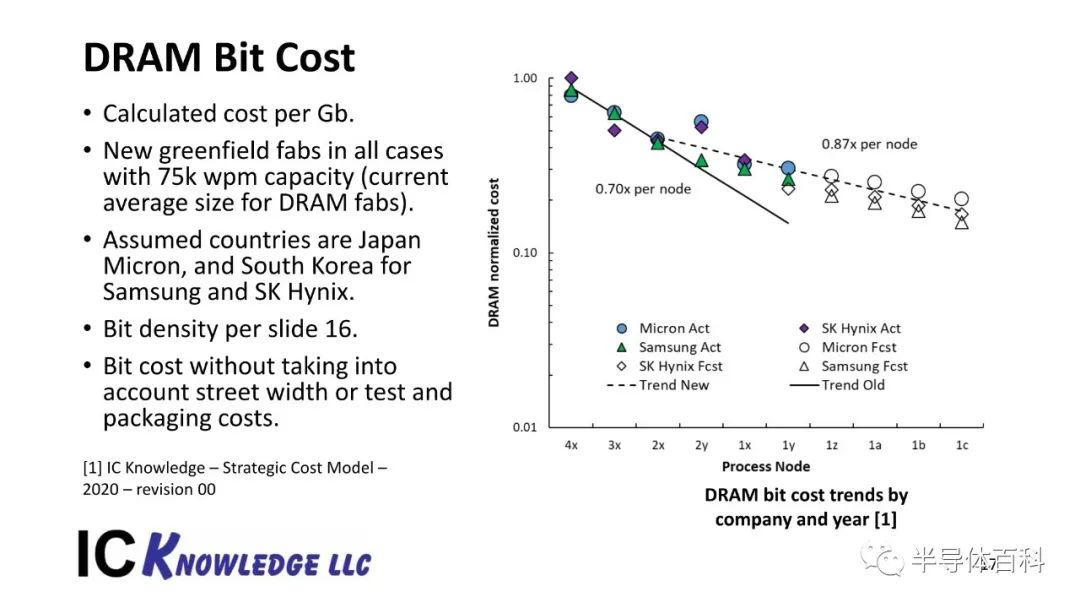

图15是基于战略成本和价格模型中的晶圆成本估算值与图14中的单位比特密度相结合得出的。所有晶圆厂都是新建工厂,每月产能为75,000片晶圆,因为这是2020年DRAM晶圆厂的平均产能。这里假设的公司与国家对应关系是,美光-日本,三星/SK海力士-韩国。

这些计算不包括封装测试成本,也没有考虑划片槽宽度或芯片良率。

在此图中,较高的掩模数和较慢的比特密度增长的组合导致从每节点成本降低0.70倍减缓至每节点成本降低0.87倍。

NAND已经成功地从2D过渡到3D,并且可以一路微缩至2025年左右。在2025年之后,可能会有非常高的层数,但是除非在工艺或设备效率方面取得突破,否则单位比特成本的降低可能会结束。

今天的前沿逻辑利用3D FinFET结构,但直到2025年左右引入CFET之后,它才是真正的堆叠器件的3D技术。通过从FinFET到HNS到CFET的过渡,逻辑有可能继续微缩至2020年代末,之后成本降低可能会放缓。

DRAM是3个市场领域中最受限制的领域,其微缩和成本降低已经显着放缓,并且目前尚无解决方案。较慢的比特密度和成本下降可能会持续到2025年左右,那时可能需要一种新的存储器类型。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2240期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

“芯”系疫情

|ISSCC 2020|日韩芯片

|华为

|

存储

|

氮化镓|高通|康佳

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie