HLS将在这个市场走向主流?

2020-04-01

14:00:10

来源: 半导体行业观察

来源:内容由半导体行业观察(icbank)

编译自「

eejournal

」,作者:Kevin Morris,

谢谢。

我(本文作者Kevin Morris)从1994年开始从事高级综合(high-level synthesis,简称 HLS)工作,假设我的数学正确,那是26年前。在早期,我们将该技术称为“行为综合”(behavioral synthesis),因为它依靠分析电路的期望行为来创建结构描述,而不是简单地从较高级别的结构描述转换为较低级别的结构描述。

HLS承诺用几十行的行为描述代替数千行详细的RTL代码,作为主要的设计输入方法。它具有快速为数据路径(datapath)尝试各种体系结构选项并选择最能实现特定应用关键设计约束的能力。HLS将硬件体系结构的细节与所需的设计行为脱钩。它扩展了重用的概念。它提高了抽象水平。这将大大提高设计师的生产率。

我们的团队以及像我们这样的团队都对HLS革新数字电路设计的潜力感到兴奋。尽管HLS面临着巨大的技术挑战,但它带来的希望是如此令人信服,以至于我们确信HLS将在三到五年内完全取代传统电子设计。

事实证明,HLS比我们最初估计的要困难得多。当然,我们的工具可以给出一个生动的演示,并且我们可以利用其中的最好的东西来制作一个FFT示例设计,但是事实证明,以一种实用且引人注目的方式处理现实世界的设计是一项巨大而又艰巨的技术挑战。经过几个月的开发和测试,HLS被戏称为“未来的技术,且将是永远的未来技术”。尽管许多芯片设计小组成功地进行了试点项目和Beta测试,但对于大多数人来说,将HLS集成到以RTL为中心的现有设计和验证流程中是极为困难的。HLS降级为“科学公平实验”的角色。

在随后的二十年中,HLS稳步成熟。摩尔定律将设计复杂性推到了必须改变方法的地步。尽管HLS提供了一种令人信服的方式来提高设计抽象水平,但更多的负担是由可重用IP块的规模和复杂性增加所承担。芯片设计团队将主要使用可重复使用的IP来组装片上系统,然后使用HLS或常规RTL设计来创建剩下的设计中相对较小和独特的部分。随着时间的流逝,HLS的优势在越来越广泛的工程界中变得显而易见,并且HLS捕获了更多这些“特殊调味料”设计模块的设计。

但是,完全采用行为抽象设计的大型片上系统的梦想从未实现。

随着Xilinx收购了AutoESL公司,HLS达到了一个重要的里程碑。在HLS根据行为描述快速生成优化的数据路径(datapath)架构的能力与FPGA快速创建这些数据路径(datapath)的硬件实现的能力之间存在强大的技术协同作用。HLS和FPGA的结合有望形成一种新的“编译器”和“处理器”对,它们可以采用C / C ++代码并创建一个可以在性能和功耗效率上击败传统处理器的引擎。通过HLS-to-FPGA流程提出的一种典型的简单但计算量很大的算法,可以轻易地将相同算法的常规CPU-软件击败,这个差距是几个数量级的。

赛灵思通过将HLS工具快速移动到其核心Vivado设计工具框架中,以HLS技术为世界铺平了道路,从根本上使HLS以非常低的成本提供给庞大的设计师社区。大型EDA供应商提供的其他HLS产品都是奇特的技术,它们的价格也相匹配。EDA已在高端ASIC设计中为HLS找到了一个利基市场,并一直保持较高的技术价格以利用这一优势。另一方面,Xilinx的产品将HLS推向了大众。在随后的几年中,Xilinx迄今已建立了使用HLS的最大的客户社区。

即使HLS通常以C或C ++开头,但绝对不是将常规软件编译为硬件的技术。许多在CPU上运行的软件中运行良好的代码构造无法直接合成为硬件,而编写可导致有效HLS实现的代码本身就是一门艺术。此外,HLS工具本身需要大多数软件工程师所不具备的硬件结构的实用知识,因此HLS通常更是经验丰富的硬件设计人员的“强大工具”,而不是使软件开发人员能够设计硬件的工具。实际上,用于HLS的C或C ++应该更多地被视为具有不同语法和语义的硬件描述语言,而不是“软件”。

但是,现在,HLS为主流接受找到了新途径,而这可能是迄今为止最引人注目的。随着AI的快速增长,整个行业都在寻求加速AI推理的方法。许多初创公司以及知名的芯片公司都急于想出最好的处理器架构,在卷积神经网络(CNN)以及其他AI架构所需的大规模卷积中,它们的性能可以超越传统的CPU。由于FPGA具有创建针对每个特定神经网络进行优化的自定义硬件的能力,因此FPGA在其中尤为突出——硬连线(hard-wired )的AI加速器无法实现这一目标。FPGA甚至有可能大大超越最佳专用通用AI加速器芯片。

但是,FPGA困扰着其他每个市场的问题同样困扰着AI领域。用FPGA创建设计非常困难。使用诸如TensorFlow之类的框架从AI专家/数据科学家的领域发展到针对该神经网络的优化FPGA(或ASIC)实现的可综合RTL级别,是一个跨越多个工程领域的艰巨挑战。HLS能够弥合这种鸿沟,从而创建了从AI框架到RTL的确定性路径。

现在,我们看到许多公司(FPGA和EDA)都在努力创建平滑,经过测试的设计流程,以封装AI-HLS-RTL方法论。赛灵思(Xilinx),英特尔(Intel),Mentor和Cadence都已发布公告,并推出了实现此流程各种风格的产品。Xilinx在其最新发布的Vitis AI框架中使用了HLS工具。英特尔相对较新的HLS技术是其雄心勃勃的oneAPI框架的关键组成部分。Cadence宣称其Stratus HLS工具用于AI加速器设计,Mentor的Catapult HLS AI工具包也是如此,而Silexica等公司则通过优化和驱动HLS流程以创建加速器体系结构的工具来扩展这些设计流程。

HLS将在许多从AI到硬件的实现流程中悄悄地进行幕后工作,但这显然是一项关键的启用技术。随着AI推理逐渐从数据中心进入边缘和端点IoT设备,对于需要以很小的功耗预算产生高性能的高度优化的推理解决方案的需求应将众多设计团队吸引到这种设计方法中。这会很有趣。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2266期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

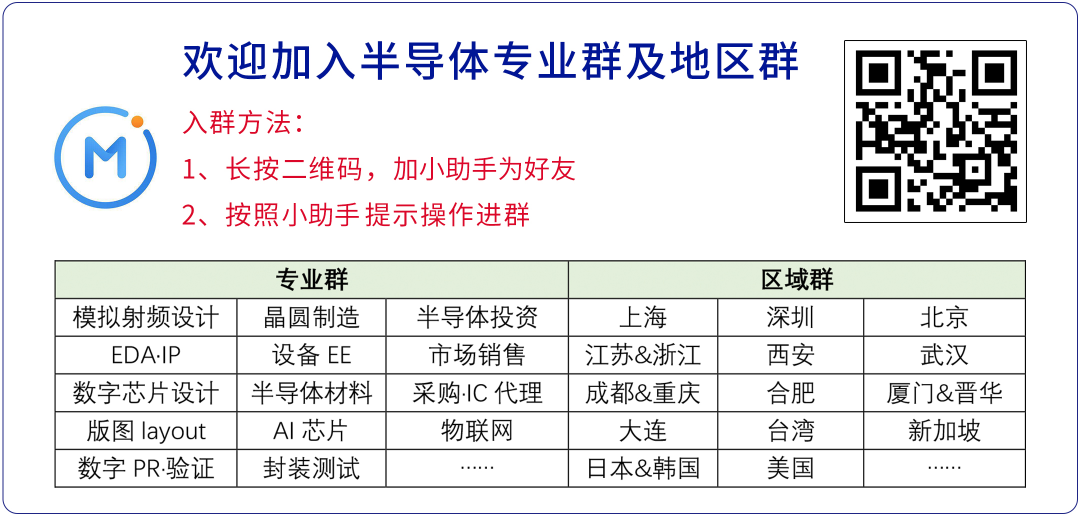

识别二维码

,回复下方关键词,阅读更多

存储|传感器

|IGBT

|

ARM

|FPGA

|中兴|苹果|半导体股价|IP

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie