[原创] NAND Flash跨入128层时代

2020-04-06

14:00:06

来源: 半导体行业观察

日前,美光发布第二季度财报,其在电话会议中美光透露,即将开始批量生产其基于公司新的RG(replacement gate)架构的第四代3D NAND存储设备。至此,美光,东芝,SK海力士和三星都已正式挺进128层,甚至更高层级,存储大厂们已经为3D NAND的堆叠层数而疯狂。

市场需求无疑是最大的驱动力,随着5G及物联网技术的发展,数据正呈现出爆炸式的增长,由此对于存储的需求也越来越大。

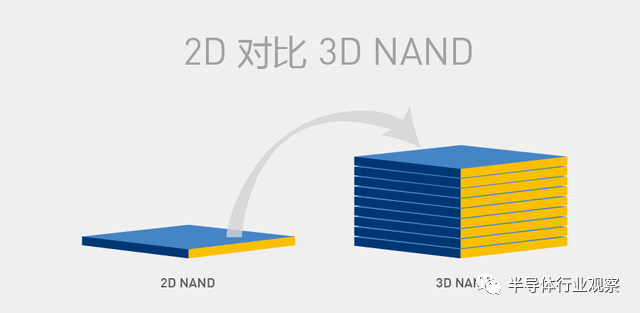

此前的闪存多属于平面闪存 (Planar NAND),我们一般称之为“2D NAND”。巨大需求推动下的2D NAND 工艺不断发展,向1znm(12-15nm)逼近, 平面微缩工艺的难度越来越大,接近物理极限,但尽管如此,存储密度也很难突破128GB容量。并且带来的成本优势开始减弱,有资料指出,16nm制程后,继续采用2D 微缩工艺的难度和成本已超过3D技术,因此各存储大厂都在积极推出3D NAND。

3D NAND,简单来说,就是通过die堆叠技术,加大单位面积内晶体管数量的增长。有资料称,3D NAND比2D NAND具有更高的存储容量,若采用48层TLC 堆叠技术,存储密度可提升至256GB,轻松突破了平面2D NAND 128GB 的存储密度极限值。

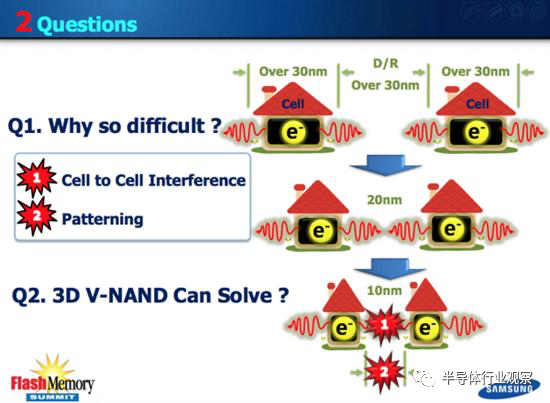

同时还具有更高的可靠性,NAND闪存一直有着电荷之间电场干扰问题,导致需要flash control芯片透过复杂的算法来防止和纠正这么干扰带来的错误,最后拖累了资料的传输速度。透过3D堆叠技术,单位储存空间变大,电荷间的电场干扰降低,大幅提升了产品的可靠性,也因资料错误降低,不仅提升了资料的传输速率,更因简化了纠错算法,进而降低了功耗,一举数得。进一步凸显了成本效益。

在主要的NAND厂商中,三星于2013年8月就已经宣布进入3D NAND量产阶段,2014 年第 1 季正式于西安工厂投产。其他几家公司在3D NAND闪存量产上要落后三星至少2年时间。

东芝、美光、SK海力士2015年正式推出3D NAND闪存。Intel 2016年4月初才发布了首款3D NAND闪存的SSD,不过主要是面向企业级市场的。在这些存储大厂的推动下,NAND Flash正在快速由2D NAND向3D NAND普及。

2019年Q3度全球NAND闪存市场明显复苏,三星、铠侠(原东芝存储)、美光等主要存储厂商的出货量均有较大幅度增长。据DRAMeXchange数据显示,2019年Q4季度全球NAND闪存市场营收125.46亿美元,环比增长8.5%,位元出货量增长10%左右,合约价也由跌转涨。

技术升级一向是存储芯片公司间竞争的主要策略。随着存储市场由弱转强,处于新旧转换的节点,各大厂商纷纷加大新技术工艺的推进力度,加快从64层3D NAND向96层3D NAND过渡,同时推进下一代128层3D NAND技术发展进程,以期在新一轮市场竞争中占据有利位置。

如前文所言,3D NAND主要依靠die堆叠,采用这种方式可以使得每颗芯片的储存容量可以显著增加,而不必增加芯片面积或者缩小单元,使用3D NAND可以实现更大的结构和单元间隙,这有利于增加产品的耐用性。因此想要增加存储空间就需要不断的增加堆叠层数,这也就是为什么先进存储厂商一直想要追求更多堆叠层数的原因。

在发展3D NAND的过程中,这些厂商通常采用两种不同的存储技术:电荷撷取技术(CTF, Charge Trap Flash)和浮栅(FG, Floating Gate)技术。

CSDN博主“古猫先生”指出,这两种技术没有好坏之分,应该是各有千秋。

CTF电荷撷取技术实现原理和过程更加简单,有利于加快产品进程。此外,电荷存储在绝缘层比存储在导体浮栅中更加的可靠。

FG浮栅技术从2D NAND开始已经很成熟。另外,采用FG浮栅技术的3D NAND的存储单元相互独立,而采用CTF电荷撷取技术的3D NAND的存储单元是连接在一起的。这样的话,FG浮栅技术的存储过程更具操作性。

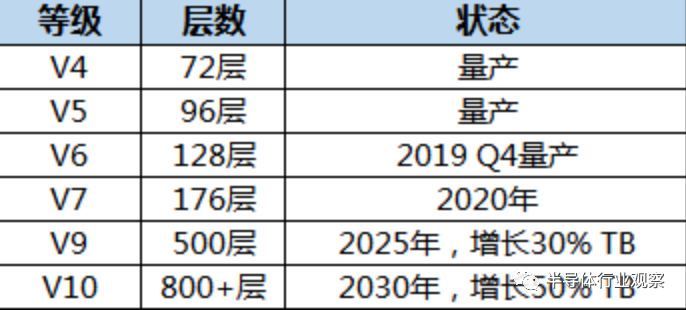

三星就是主推CTF电荷撷取技术的厂商 ,其3D NAND的发展轨迹是48层-64层-96层-128层+。从2013年开始量产第一代3D V-NAND,到2018年,开始批量生产第五代V-NAND 3D堆叠闪存,9x层的堆叠设计;一直引领着存储行业在闪存容量和性能方面的持续性创新。

三星在2019 年 6 月就推出了第六代 V-NAND(128 层 256Gb 3D TLC NAND),8 月份宣布基于该技术已批量生产 250GB SATA SSD,而在 11 月实现了第六代 128 层 512Gb TLC 3D NAND的量产。

据三星官方消息显示,新款 V-NAND 运用三星电子有的“通道孔蚀刻”技术,向前代 9x 层单堆叠架构增加了约 40% 单元。这是通过构建由 136 层组成的导电模具堆栈,然后垂直自上而下穿过圆柱孔,形成统一的 3D 电荷撷取闪存 (CTF) 单元实现的。

SK海力士也采用CTF电荷撷取技术,在由2D转进3D NAND世代的竞争中,SK海力士似乎一直处在掉队状态,落后过去 2D 平面式 NAND Flash 时代。因此,SK 海力士在全球 NAND Flash 排名中,已经被甩到五名之外。这对于在 2D 时代实力很强的 SK 海力士,属实有点让人意外。

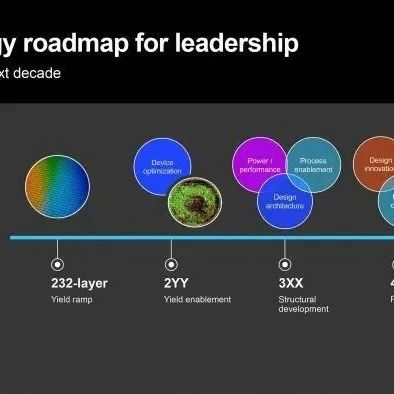

2019年,在美国闪存峰会上,SK海力士公布3D NAND技术路线图,此技术路线图展示,在2030年3D NAND将达到800多层的堆叠高度。SK海力士将该技术称为第6版4D NAND,但其他制造商都将其称为3D NAND。其中176层对应1.38 TB,500层对应3.9 TB,800层对应6.25 TB。

SK海力士在 2019 年 6 月份宣布推出首款 128 层 TLC 4D NAND,11 月份向主要客户交付基于 128 层 1Tb 4D NAND 的工程样品并较预期提前量产。这种先发优势,将会有助于抢占市场,更快达到规模经济。

SK海力士128层TLC 4D NAND将在2020年进入投产阶段。同时正在开发下一代176层4D NAND,将通过技术优势,持续增强其在NAND Flash市场上的竞争力。

东芝方面,也是CTF电荷撷取技术,东芝是目前日本最大的半导体制造商,也是闪存技术的缔造者,于1989年最早研制出了NAND闪存。虽然东芝公司最早提出3D NAND架构,并于2012年成功研发16层3D NAND实验品,但却迟迟未推出相关产品上市,导致其市场步伐落于三星之后。

据悉,迫于三星的市场压力,东芝计划采用P-BiCS(Pipe-shaped Bit Cost Scalable)技术量产3D NAND产品,样品于2014年Q1送样,计划于2016年第二季度量产;且在2016年度至2018年度,东芝大举投资半导体存储器,投资额将达8千亿日元。

2018 年6 月东芝将铠侠独立出去,并卖给由美国贝恩资本主导的「日美韩联盟」。东芝目前仍持有铠侠40.2%股权。

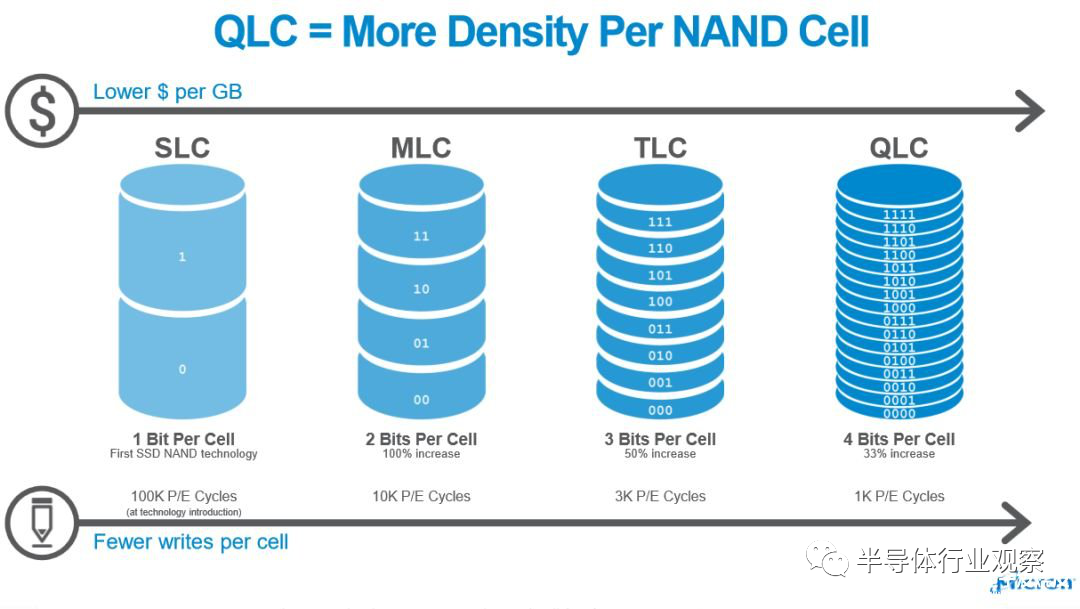

1月31日,铠侠宣布已研发出3D NAND Flash「BiCS FLASH」的第5代产品,采用堆叠112层制程技术,且已完成试作、确认基本动作。该款堆叠112 层的3D NAND 试作品为512Gb(64GB),采用3bit/cell(TLC:Triple Level Cel)技术的产品,预计将在2020 年第一季进行样品出货,除将用来抢攻需求持续扩大的资料中心用SSD、商用SSD、PC 用SSD 及智能手机等市场外,也将用来抢攻5G、人工智能(AI)、自动驾驶等新市场需求。

铠侠指出,该款112 层3D NAND 产品为该公司和合作伙伴美国Western Digital(WD)所携手研发完成,今后将利用双方共同营运的四日市工厂以及北上工厂进行生产,且今后也计划推出采用堆叠112 层制程技术的1Tb(128GB)TLC 产品以及1.33Tb 的4bit/cell (QLC:Quadruple-Level Cell)产品。关于上述112 层3D NAND 的量产时间,WD 宣布,预定将在2020 年下半年。

美光过去在 2D 平面式 NAND FLash 技术世代,一直与英特尔联合开发技术、分摊产能建置成本等。

不过,从 2D 转进 3D NAND 世代中,美光已经直逼拥头部厂商水准。IC 设计业者分析,美光在 3D NAND 技术层面,已经直逼三星水准,其读写 read/write performance 只有三星可以抗衡,且在相同layer 下,其die size 也是业界最小,技术实力在 3D NAND 时代大幅追上来

。

2019年10月初,美光宣布第一批第四代3D NAND存储芯片流片出样。第四代3D NAND基于美光的RG架构,采用128层工艺。在“Mircon Insight2019”技术大会上,美光科技执行副总裁兼首席商务官Sumit Sadana表示,128层3D NAND如果被广泛使用,将大大降低产品每比特成本。

如前文所言,他们即将开始批量生产其基于公司新的RG架构的第四代3D NAND存储设备,美光第四代的28层3D NAND即将流片表示,表示该公司新设计不仅仅是一个概念。

同时,美光还没有计划将其所有产品线都转换为最初的RG处理技术,因此明年公司范围的每位成本将不会大幅下降。尽管如此,该公司承诺在其后续RG节点广泛部署之后,到2021财年(从2020年9月下旬开始)将实现有意义的成本降低。

相比国际先进水平,国内厂商长江存储也在3D NAND上有所突破,并推出了其独特的Xtacking技术。

据相关报道显示,传统3D NAND架构中,外围电路约占芯片面积的20—30%,降低了芯片的存储密度。随着3D NAND技术堆叠到128层甚至更高,外围电路可能会占到芯片Xtacking技术将外围电路连接到存储单元之上,从而实现比传统3D NAND更高的存储密度。

据悉,长江存储的64层3D NAND闪存产品将在2020年进入大规模量产,此外,长江存储还将在今年跳过96层,直接投入128层闪存的研发和量产工作。

从进度来看,128层3D NAND基本将在今年大量进入企业存储市场,逐渐成为主流。但是从此亦可看出,存储厂商间的新一轮技术升级之争亦将变得更加激烈。

半导体专家莫大康指出,存储芯片具有高度标准化的特性,且品种单一,较难实现产品的差异化。这导致各厂商需要在工艺技术和生产规模上比拼竞争力。

因此,每当市场格局出现新旧转换时,厂商往往打出技术牌,以期通过新旧世代产品的改变,提高产品密度,降低制造成本,取得竞争优势。

值得注意的是,今年由于疫情原因,可能影响智能手机及笔记本等消费电子产品的出货,闪存出货量预计会衰退或者持平。因此也有业内人士指出,存储厂可能会更趋向于加大96层3D NAND的生产。

对于中国存储业来说,技术上从2D到3D的改变,是一个难得的发展机遇,但是如何抓住这个机遇仍具挑战。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2271期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

存储|射频|CMOS|

设备

|FPGA

|晶圆|苹果|海思|半导体股价

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie