索尼三星统领CMOS图像传感器市场的底气

2020-04-09

15:42:22

来源: Sophie

来源:内容来

自「

CTIMES

」,

谢谢

。

智能手机的相机功能可以有多强?三星电子(Samsung)近期发表的最新旗舰型5G手机,树立了一个新典范。该款新手机的拍摄画素来到了1亿800万的等级,可拍摄8K的影片,而且最大的变焦数来到了史无前例的100倍,更惊人的是,几乎克服了夜间低光源的拍摄困难,实现了随时、随地、随身的高品质摄影的可能。

达成这个目标背后的功臣,就是先进的CMOS影像感测器技术,而三星所使用的,是一个名为「ISOCELL」的影像感测器系统。该产品是三星自行研发的CMOS影像感测技术,目前最新的一代为「ISOCELL Bright HM1」。

在2018年初,三星宣布了新一代的ISOCELL(Fast 2L3版本)技术更新,而这次的更新是一个重大的升级,因为三星正式将3层堆叠架构运用在CMOS影像感测器上。

在此之前,一般的CMOS感测器是采两层的结构,也就是把产生光感讯号的画素阵列(pixel array)感测器,以及进行电子与数位讯号转换的逻辑运算器进行堆叠,借此加快运算的速度,并减少DRAM的使用。

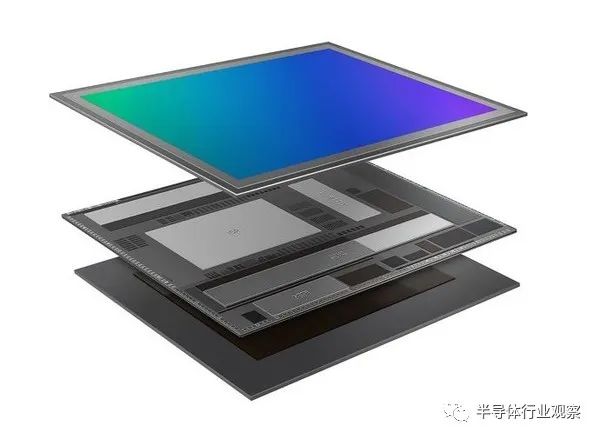

图一: 三星把DRAM整合至影像感测器之中,完成了一种三层的架构。(source:三星)

这种双层的结构对于实际的影像拍摄来了诸多的好处,最明显的就是实现了超高的画素(image readouts)读取性能,并让电子快门的即时取景,与顺畅的超级慢动作成为可能。

站在这个基础上,三星进一步把DRAM整合至感测器的结构之中。他们把2GB的LPDDR4 DRAM置于逻辑层之下,完成了一种三层的架构,并带来了超高速的的影像拍摄性能。

由于整合了2GB的DRAM,感测器可以在把数据传送到处理器之前,暂时储存大量的影像资讯,所产生的结果就是超高速的电子影像快门,以及清晰无比的录影功能,对于拍摄者而言,就是更强大的照相能力,以及超高解析的影片拍摄。最明显的改进,就是消除了过去CMOS感测器的照片变形与所谓的果冻现象(Rolling shutter)。

另一方面,高速快门与瞬时储存多重画帧(multiple frames)的性能,就能支援3D降噪(Noise Reduction)以及更高阶的高动态范围成像(HDR)。而这对经常需要在室内拍摄的手机来说,是非常重要的提升。

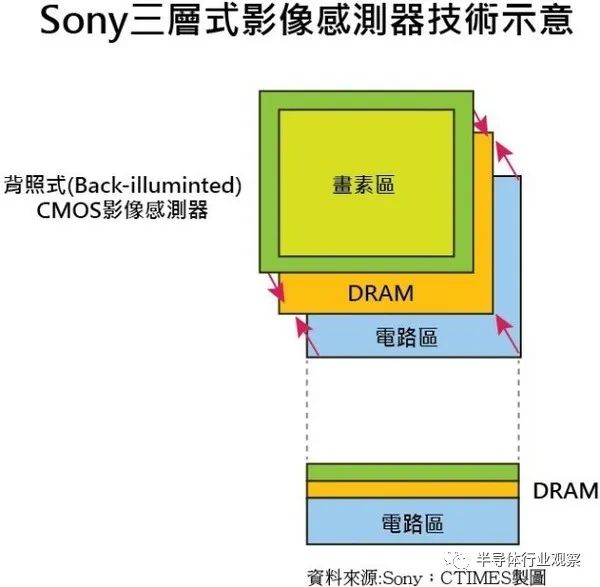

事实上,三星并不是第一个使用三层式堆叠技术的业者,早在2017年,Sony就发表了三层式的堆叠CMOS影像感测器技术。但是不同于三星,Sony的DRAM层是为在中间,画素感测在前,逻辑电路则是在后。此设计同样达成了高画素与更快的影像帧数,让智能手机的拍摄有了全新的思考。

近期,Sony则是进一步把堆叠式CMOS影像感测器技术拓展至工业领域上。他们与Prophesee合作开发的新一代事件导向(Event-based)CMOS视觉感测器,就是把光学画素阵列感测器堆叠在逻辑处理器之上,并以铜垫(copper pads)连接的方式取代过去采TSV的作法。透过这个堆叠的架构,Sony实现了业界最小的画素尺寸(1 4.86μm),和最高的HDR的性能(1 124dB)。

图二: Sony的DRAM层是为在中间,画素感测在前,逻辑电路则是在后。

一直以来,Prophesee的事件导向影像感测技术,就是以高光学资料读取量与快速的画素反应著称,再与Sony高敏感与低杂讯的CMOS影像感测器结合,两者合一,则是产生了兼具速度与质量的影像感测产品。而采用堆叠的结构,则又更进一步缩减了晶片的面积,这对于物联时代寸土寸金的产品体积来说,十分有经济效益,尤其是机器视觉与安全监控等应用。

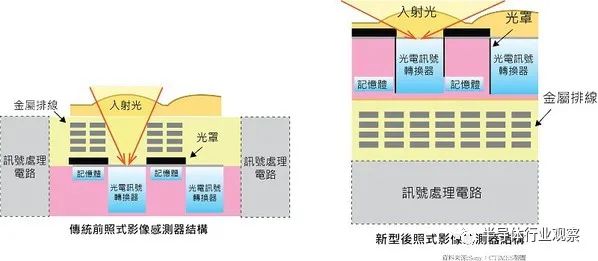

图三: 采用堆叠的结构,则又更进一步缩减了晶片的面积。

而尽管堆叠的架构能为影像资料的运算与晶片体积带来突破,但影像本身的质量则是完全取决于感测技术对光感的画素反应,要有更细致与更大量的画素,就要在画素层的技术着手,让光感反应更敏感,同时画素资料更细致。

以Sony为例,就是采用背照式(Back-illuminated)的影像感测结构,再搭配自主研发的专属画素结构(proprietary pixel structure)技术,达成了优越的敏感度,同时也改善了过去画素微小化的缺陷。

图四: 背照式(Back-illuminated)的影像感测结构。

透过这个技术,Sony把画素微缩至2.74 μm,并维持了元件的敏感度以及色彩饱和度,也由于采用后照式的形式,感测器得以针对更广的区域进行侦测与量测,这意味着能够产生更多更精细的讯号,所以整体的解析度也较前照式架构增加了1.7倍。

至于三星则是运用独家的画素模拟技术「Teracell」,来突破实体感测画素无法增加的困境,他们透过特殊的演算法,让画素以四个为一组的形式安排在影像感测器的彩色滤光片。

当处于低光源的拍摄时,演算法就会把四个画素模拟成一个,让画素变大;反之,在明亮的环境时,则使用称之为「再马赛克(re-mosaic)」演算法,把原本的画素再分割成四格,借此产生更高解析度的照片。这个技术不仅改善了明暗成像的性能,同时也增加了HDR在高对比环境中的拍照能力,等于全面提升了手机的拍摄能力。

而三星最新一代的ISOCELL Bright HM1,则是更进一步采用了新的「Nonacell」技术,它其实是Teracell的升级版。不同于前代使用四画素(2 x 2)一组的结构,新的Nonacell则是使用9画素(3 x 3)一组的结构,把拍摄画素一举推升到了1亿800万的等级,同时新的感测器的画素尺寸则是缩小至0.8μm,意味着能够对光感测讯号有更细致的敏感度,在明暗两端的拍摄也更加突出。

就系统设计的观点,CMOS影像感测器本身的体积只能有减无增,并不允许其占用过多的装置空间。而在这个前提下,想要达成更佳的拍摄品质,就只能从制程与设计结构来改善。

但若从应用的角度切入,则拍照与摄影其实是软硬体协同产出的结果,所以想要突破目前的成像限制,更多的光学工程设计与软体优化的技术也是不可或缺的,例如AI与人工智能的导入等,都是可用之策。

所以对于系统开发商来说,寻求先进的影像感测器方案固然是一个明显的对策,但思考进一步结合第三方的光学设计与优质的软体协助,从整体性的影像拍摄体验进行改良,才会是最佳对策,而这也是前述这两家业者能够持续领先的原因所在。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2274期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

存储|射频

|CMOS

|

设备

|FPGA

|晶圆|苹果|海思|半导体股价

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie