来源:文章转载自期刊《微纳电子与智能制造》,作者:冯鹏,刘力源,吴南健,谢谢。

使用硅通孔技术将图像传感、处理和存储芯片以垂直堆叠的方式进行连接,可实现更加先进的光电融合三维集成人工智能视觉芯片。介绍了与三维集成视觉芯片相关的研究进展,包括超高速成像、三维成像和宽光谱太赫兹成像等超越人类视觉水平的图像传感技术,基于仿生机理的高能效视觉处理芯片以及三维集成视觉芯片相关技术。

视觉是人类最重要的信息获取途径 ,视觉信息占人脑获取信息总量的80%以上,而随着各种图像传感技术的发展,据统计,2012年图像和视频数据占数据总量的比例已达到了80%。视觉图像的采集 、传输、处理和存储已成为人工智能和大数据技术应用的基础。然而,在传统的图像系统中,图像的采集和处理在硬件上是分离的,这一方面将导致图像数据传输速度瓶颈,使得系统很难满足高速实时图像处理的应用需求;另一方面将导致系统的体积和功耗过大,限制其应用场景。为了突破传统图像系统面临的上述瓶颈 ,早在上世纪九十年代,美国加州理工学院的Mead和日本东京大学的石川正俊等就提出了视觉芯片的概念。视觉芯片是一种模仿人类视觉功能 ,集高速图像采集、并行图像传输和并行图像处理能力于一体的数模混合系统级半导体芯片。视觉芯片的典型应用场景如图 1所示 ,其在机器人 、自动驾驶 、智能监控、目标跟踪等领域都有非常重要的应用价值。经过二十多年的快速发展 ,视觉芯片架构目前已发展到了第三代。

第一代视觉芯片采用全像素并行架构,处理器以单指令多数据(SIMD)方式工作,因此有并行度高、处理速度快的优点,但主要缺点是像素填充因子小,分辨率难以大幅提升,难以实现广域图像处理的功能。

第二代视觉芯片采用像素阵列和处理单元电路分离的架构,分辨率得以大幅提升,而其中处理电路包括二维像素级处理阵列(PE阵列)和一维行并行处理器阵列(RP 阵列)。其中 PE 阵列与第一代视觉芯片中的并行PE阵列功能类似 ,而RP阵列由计算能力较强的处理器构成 ,可以完成广域图像处理的功能。这种视觉芯片的缺点是不能快速完成图像分类等算法,在处理图像识别任务时实时性较差。

第三代视觉芯片在第二代视觉芯片的基础上引入了人工神经网络或卷积神经网络来加速分类的算法。这种视觉芯片可以快速完成地平线检测、手势识别、指尖追踪和人脸识别等多种复杂的图像识别任务。

然而,上述视觉芯片存在的问题是视觉传感器和图像处理电路均采用相同的工艺以二维集成的方式实现。由于芯片通常需要采用图像传感器工艺实现,受到工艺的限制,其图像处理能力难以大幅提升。此外,随着视觉芯片应用领域的逐渐拓展,采用二维集成的视觉芯片还面临芯片面积大、功耗高、处理速度提升有限的瓶颈。因此,三维集成的视觉芯片已成为发展的必然趋势。三维集成视觉芯片利用硅通孔技术(through silicon via, TSV)将图像传感、处理和存储芯片以垂直堆叠的方式实现连接,有望实现超越人类视觉,具有高速、小体积和低功耗特点的光电融合人工智能视觉芯片。本文将首先介绍超高速成像、三维成像和宽光谱太赫兹成像等超越人类视觉水平的图像传感技术;然后介绍基于仿生机理的高能效视觉处理芯片;最后介绍三维集成视觉芯片相关研究进展。

在视觉芯片中,视觉传感器负责图像信息的采集,是视觉芯片功能实现的基础。为了实现超越人类视觉水平的视觉芯片,首先需要实现具有超越人类视觉功能的图像传感器。目前 ,超高速视觉图像传感器、三维成像视觉传感器以及宽光谱视觉传感器是3种比较典型的具有超越人类视觉特点的传感器,也是当前的研究热点。

在科学及工程的先进研究领域,对燃烧、材料断裂及静电击穿等高速现象进行观测已成为迫切的需求。为了能够有效观测到这些现象 ,需使用帧率超过100万帧/s(1Mfps)的超高速CMOS视觉传感器 。这种传感器能以极高的速度采集图像信息并缓存至片上模拟信号存储器中( 突发工作模式,burstmode),然后以相对较低的速度将片上模拟信号存储器中的图像信息输出至芯片外( 连续工作模式 ,continuous mode)。片上缓存的图像帧数将受到片上模拟存储器数量的限制。

在超高速CMOS视觉传感器中,主要有5个因素限制了像素信号的读出速度:

(1)像素驱动信号的稳定时间;(2)大尺寸光电二极管中光生电荷的转移时间;(3)信号从像素至列线的读出时间;(4)信号在列并行电路中的处理时间;(5)信号从列并行电路至芯片接口的读出时间。近年来,超高速CMOS视觉传感器技术发展迅速。一方面,通过光电二极管掺杂浓度以及掺杂形状的设计来产生电场加速电荷转移;另一方面,通过在片上集成模拟信号存储器对像素信号进行超高速缓存,之后再通过列并行处理电路及接口电路实现像素信号的模数转换及高速输出。

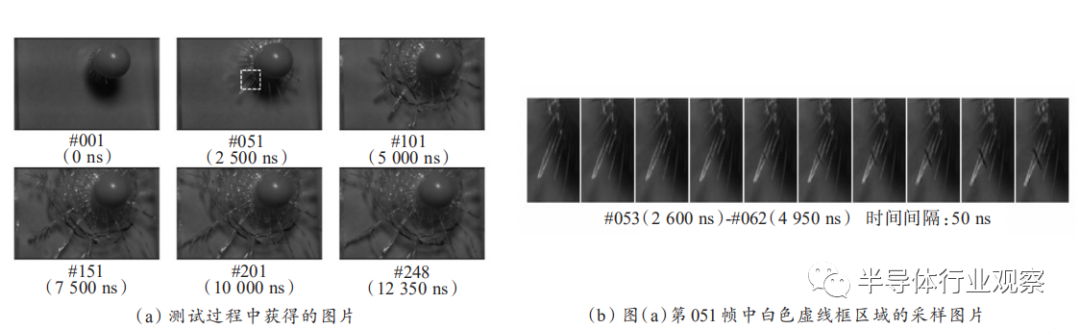

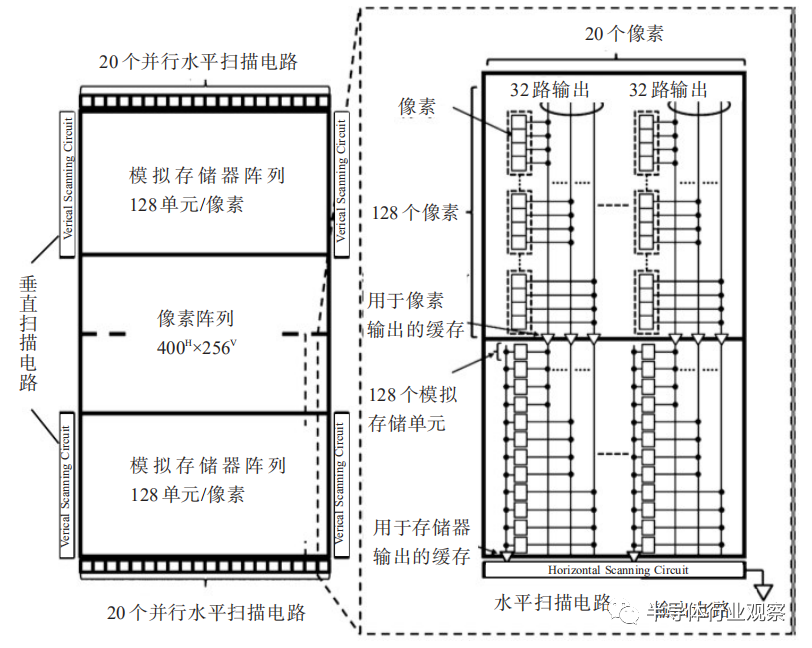

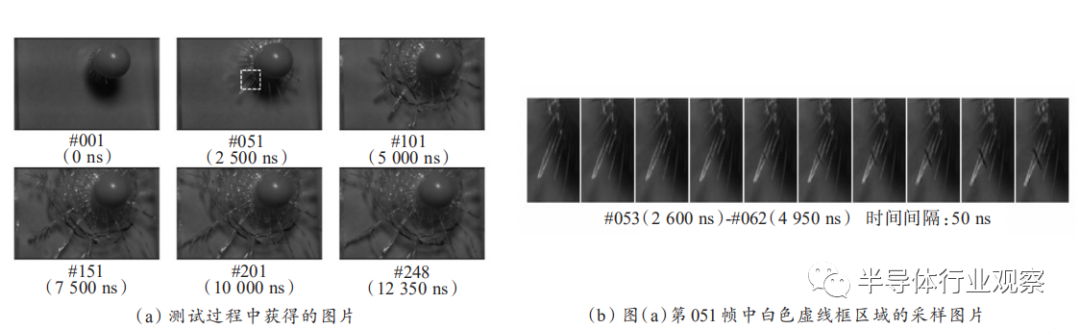

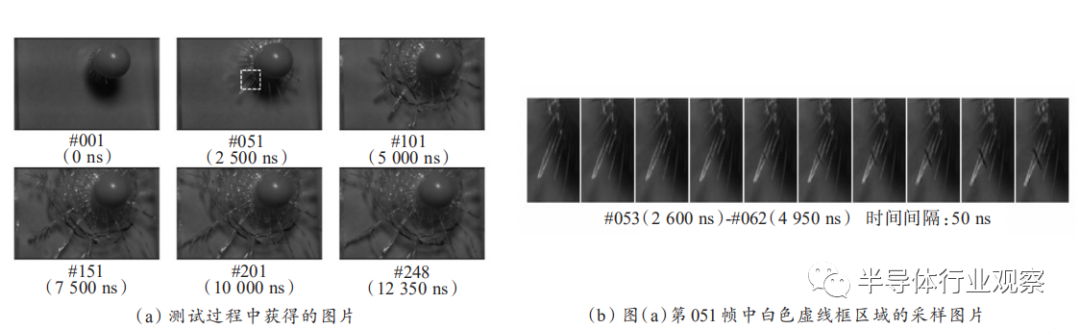

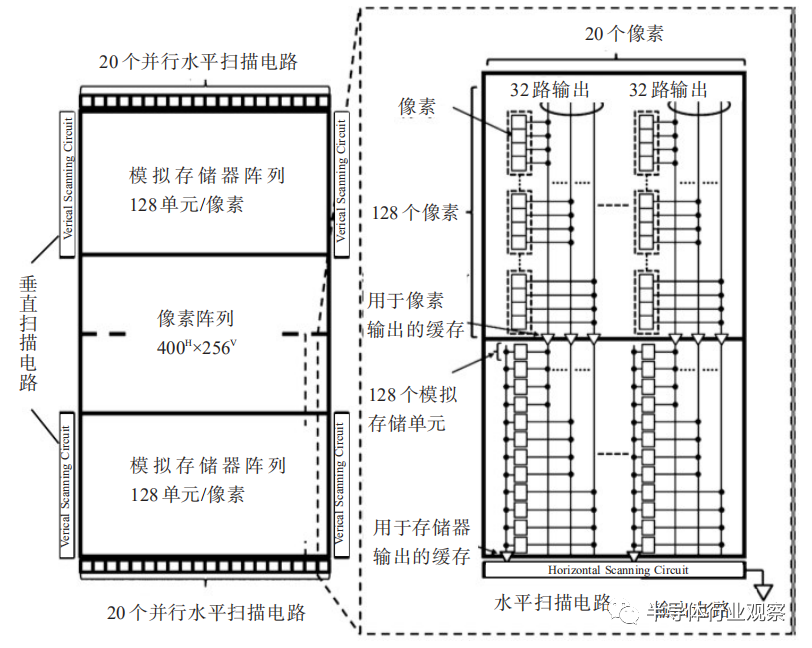

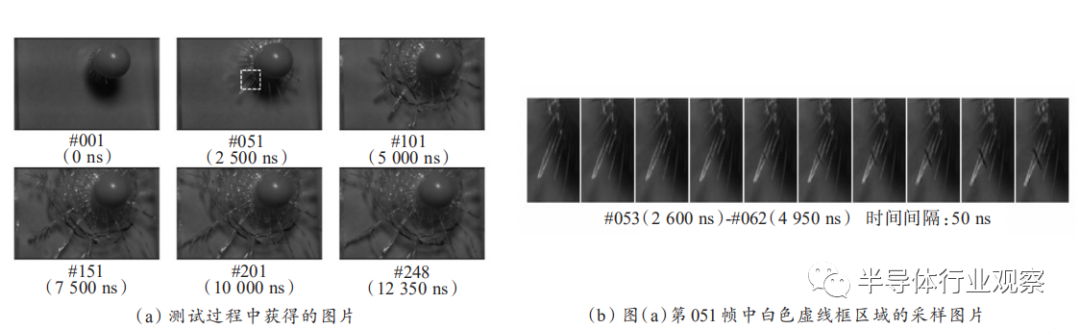

2012年,日本东北大学基于0.18μm CMOS图像传感器工艺设计实现了突发帧率工作模式下图像采集速度超过10Mfps的全局曝光视觉传感器,其分辨率为 400

H

×256

V

,可支持128帧图像的连续存储。该传感器采用了像素阵列和片上模拟存储器相分离的结构,其结构框图如图2所示,该传感器在半分辨率模式下,以20Mfps速度采集到塑料子弹击碎玻璃时的图像如图3所示。2019年,该研究团队又基于0.18μm CMOS图像传感器工艺,采用像素和片上模拟存储单元相邻的结构,实现了最高帧率超过100Mfps的超高速CMOS视觉传感器,其分辨率为25

H

×100

V

,可支持80帧图像的连续存储。

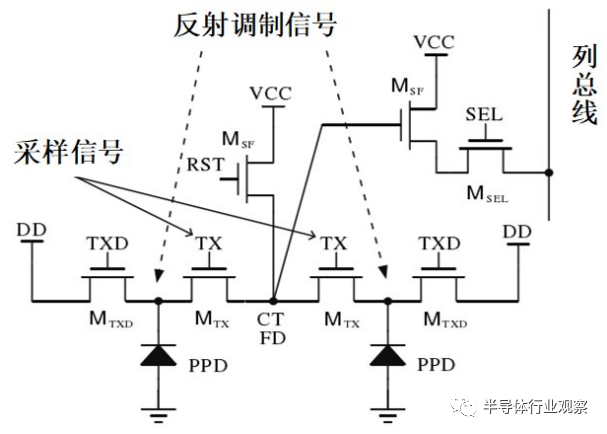

大多数图像传感器在获取图像信息时 ,往往丢失了真实世界中观测物远近的距离信息。三维成像视觉传感器能够获得图像的三维信息,在科学研究、工业检测、安全监控和消费娱乐等领域具有广泛的应用前景。目前 ,商用的三维成像技术主要有立体视 觉 技 术(stereo vision),结构光术(structuredlight)以及飞行时间技术(time of flight, ToF)等。其中ToF技术具有低功耗和微型化的重要优势,能够满足便携式电子设备的需求,已成为目前三维成像视觉传感器的研究热点。根据成像原理,ToF视觉传感器可分为直接ToF(D-ToF)三维视觉传感器和间接ToF(I-ToF)三维视觉传感器。D-ToF三维视觉传感器的工作原理类似于激光雷达的测距原理 ,即由光源向场景发射激光脉冲 ,并以二维阵列探测器捕捉发射信号,探测器基于单光子雪崩二极管(SPAD)和时间数字转换器(TDC)阵列实现飞行时间测量及图像深度信息的探测,可以实现100m左右距离和较高测量精度的三维成像,但这种传感器电路结构较复杂,难以实现较大的像素阵列,此外通常还需要配置机械扫描装置和相应的光学系统,难以实现较低的成本和体积。I-ToF三维视觉传感器采用CMOS图像传感器的感光像素对光源发射的连续脉冲信号的反射信号进行高速采样,然后通过解调计算出连续脉冲信号的相位延迟信息,进而推算出信号飞行时间和距离,这种结构像素面积较小,能够实现较大的像素阵列,具有低成本和高成像速率的优点,但测量距离通常较近。

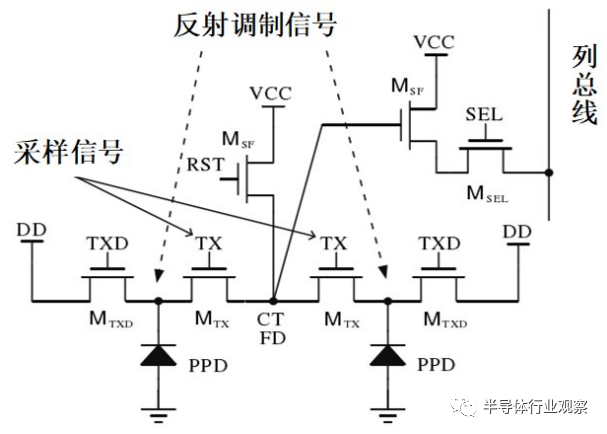

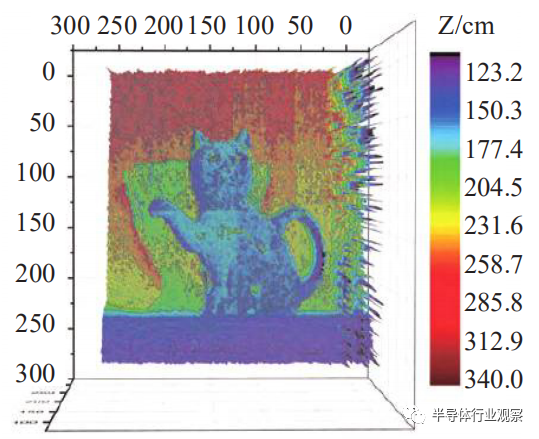

2016年,中科院半导体所基于0.18μm CMOS图像传感器工艺,采用I-ToF技术实现了一款分辨率为256

H

×256

V

的ToF三维视觉传感器。其中像素尺寸为10μm×10μm最大深度测量距离为7.5m,测量误差为4cm@2.5m,最高帧率达到90fps。像素的结构以及三维成像的测试结果如图4和图5所示。

2018年,微软公司基于65nm背照式(BSI)CMOS图像传感器工艺,采用I-ToF技术实现了一款分辨率为1024

H

×1024

V

的全局曝光ToF视觉传感器。其中像素尺寸仅为3.5μm×3.5μm,最大深度测量距离达到4.2m,测量误差小于0.2%,帧率为30帧/s。

2019年,荷兰代尔夫特理工大学基于0.18μmCMOS工艺,采用D-ToF技术实现了一款分辨率为252

H

×144

V

的ToF视觉传感器。最大深度测量距离达到50m,测量精度达到8.8cm,帧率为30帧/s。

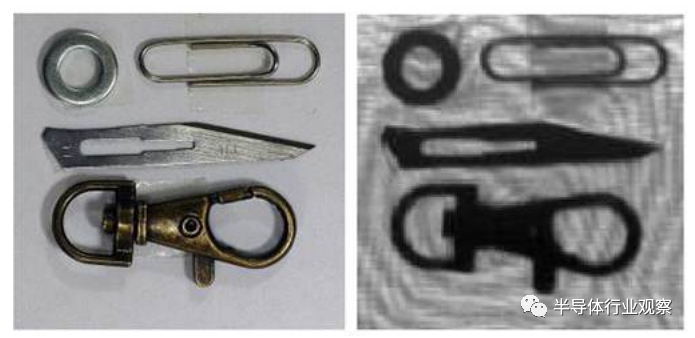

太赫兹(Terahertz,THz)波是指频率在0.3~3THz(1THz=1012GHz)范围内的电磁波,其介于毫米波与远红外波之间。太赫兹波具有透射性、非电离性、指纹特征、分辨率高、带宽高等多种特性。与可见光成像相比,利用太赫兹波成像可以穿透塑料、木材、纸张等障碍物实现透射成像,并且由于没有电离辐射,安全性好,太赫兹波成像技术在安全检查、生物医学检测、雷达和无线通信等领域具有非常好的应用前景。

由于CMOS工艺具有体积小 、易大规模集成和廉价等特点,基于CMOS工艺实现的太赫兹波探测器近年来得到了广泛研究。2012年,德国伍珀塔尔大学发表了一款基于65nm CMOS工艺集成32×32阵列像素以及信号放大的太赫兹波探测芯片,单个像素的尺寸为80μm×80μm,芯片采用场效应晶体管实现了0.7~1.1THz太赫兹信号的探测,图像采集帧率达到25fps。中科院半导体所在2017年和2018年分别实现了采用场效应晶体管作为探测器件,集成片上信号处理电路的太赫兹CMOS视觉传感器。太赫兹波图像传感器像素结构示意图如图6所示,像素采用基于两个晶体管(2T)的结构,其包含了太赫兹波探测晶体管 M1、选择开关管 MSEL、天线、匹配网络TL1和微带线TL2。860GHz频段下树叶以及隐藏在信封内部金属的成像效果如图7所示。

(b)860GHz频段下隐藏在信封内部金属的成像效果

生物神经系统可以在资源十分有限的情况下,实现远超过现有视觉芯片的智能处理能力,因此我们希望能够从生物神经系统的工作原理找到高能效仿生视觉处理芯片的设计思路。为了实现这样的芯片,可从两个方面进行突破,一是提出新的仿生计算架构,如可大规模并行协同工作的神经元和突触结构;二是提出新的信息描述方法,如采用脉冲信号来对信息进行编码 ,信息的处理完全基于事件驱动模式,从而实现高能效计算。由于数字芯片工艺具有设计周期短、可靠性高的优点,为了能够尽可能利用先进的深压微米数字工艺来推动仿生处理芯片的发展,近年来多个研究团队开启了数字神经网络芯片的研究。

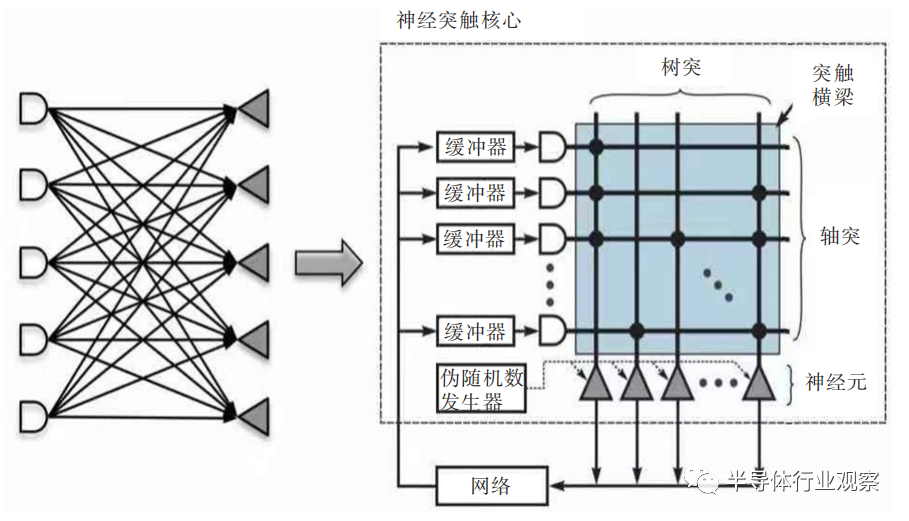

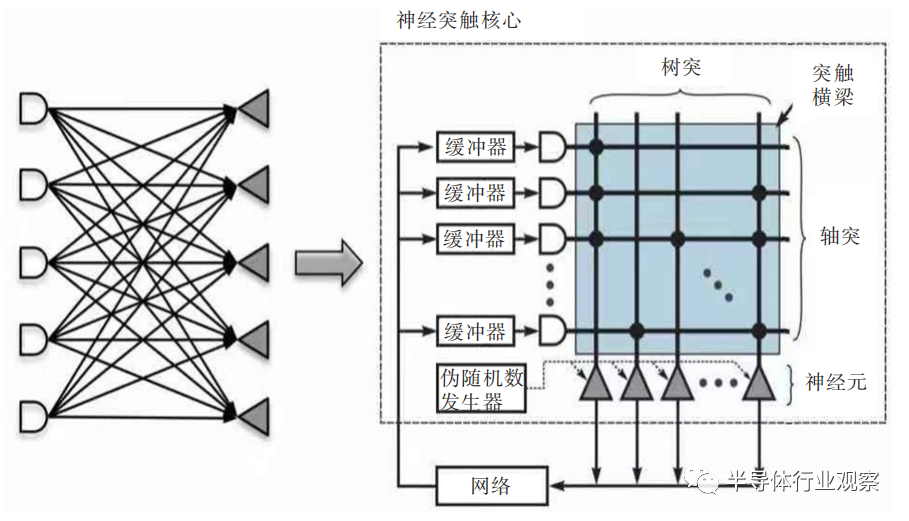

目前,比较有代表性的研究成果有两类。一类是通过在芯片上大规模集成神经元,实现功能强大、类脑程度较高的处理芯片,如IBM公司提出TrueNorth芯片和Intel公司提出的Loihi芯片。其中TrueNorth芯片基于28nm CMOS工艺实现,集成了10

6

个神经元结构以及2.56亿个突触结构,功耗仅为65mW。而Loihi芯片则基于14 nm CMOS工艺实现,神经元以及突触的密度分别达到了2 184万/mm

2

和210万/mm

2

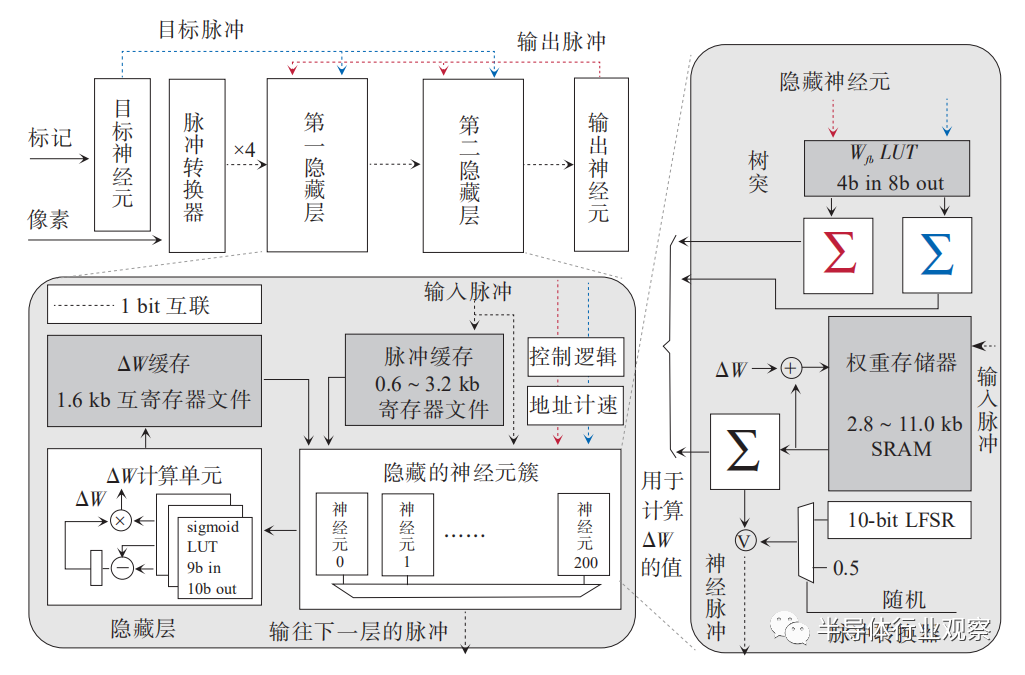

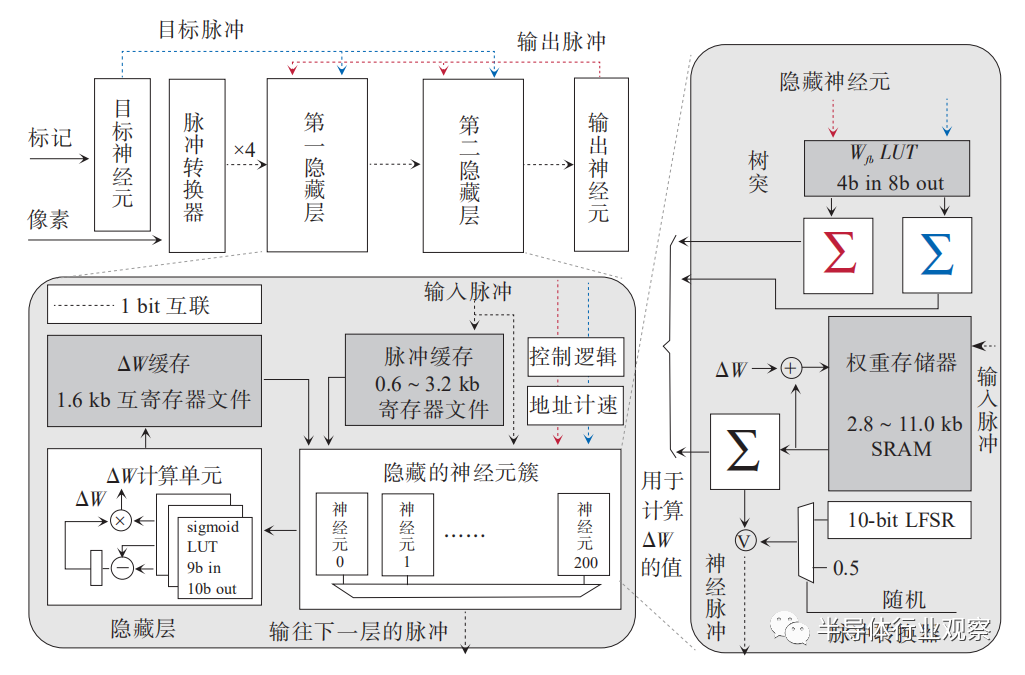

。TrueNorth芯片的神经网络硬件实现与处理单元之间的连接结构如图8和图9所示。另一类是兼具脉冲神经网络和深度神经网络特点的处理芯片,如首尔大学于2019年提出的神经网络处理器,该处理器基于65 nm CMOS工艺实现,处理图像和在线训练时功耗分别仅为23.6mW和23.1 mW,图像分类精确度达到97.83%,总能效达到3.42TOPS/W。该神经网络处理器的结构如图10所示。

图8. TrueNorth芯片中神经网络的硬件电路实现

图9. TrueNorth芯片中多个处理单元的连接结构

图10. 兼具脉冲神经网络和深度神经网络特点的处理芯片

在二维集成视觉芯片中,视觉传感器、存储器和视觉信息处理器集成在同一颗芯片上,采用同一种工艺实现,因此难以同时将几种电路优化到性能最佳的状态。为了实现能够超越人类视觉极限的高速高性能人工智能视觉芯片,以满足更多的应用需求,一方面需要开发特殊工艺实现超越人类视觉感知能力的传感电路和高性能存储电路,另一方面需要使用最先进的数字芯片工艺开发具有更加智能和高效的视觉信息处理电路。因此,TSV等三维集成技术将不同工艺特点的芯片在垂直方向上实现互联和集成,从而实现高性能、高能效、高带宽和小尺寸的三维集成视觉芯片已成为未来发展的趋势和研究热点。下面分别介绍三维集成技术在视觉传感器、存储器以及视觉芯片中的应用研究。

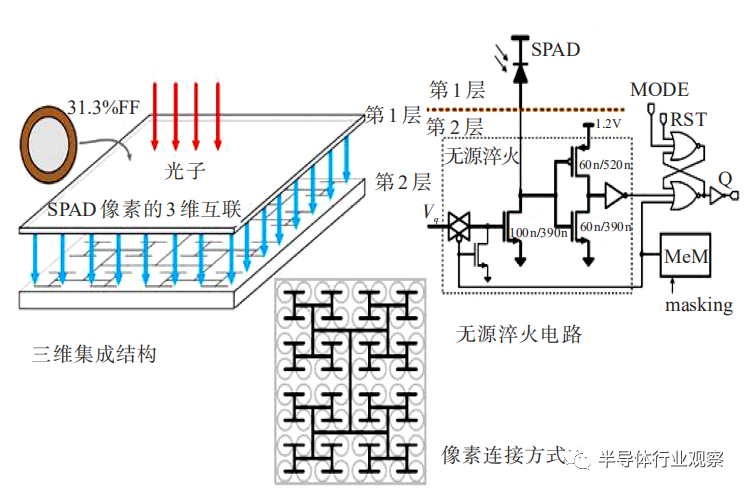

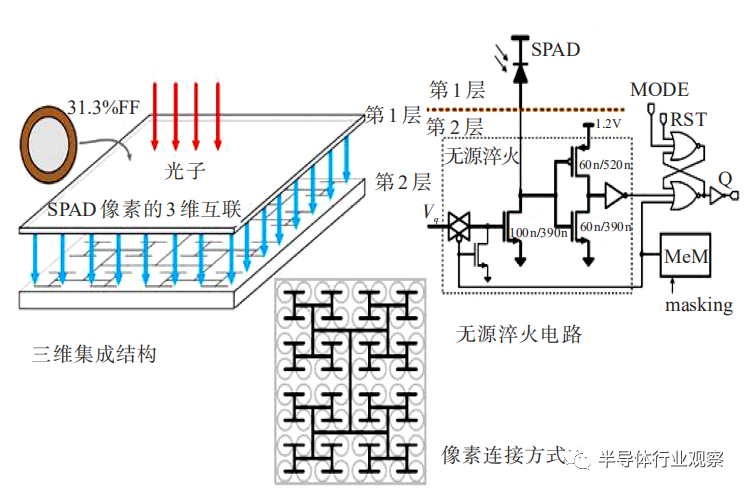

2018年,荷兰代尔夫特理工大学采用三维集成的方式,实现了一款分辨率为 256

H

×256

V

的D-TOF视觉传感器。其中的传感器部分基于45nm背照式CMOS 图像传感器工艺,采用单光子雪崩二极管(single-photon avalanche diode,SPAD)阵列实现。而其中的数字信号处理和通信电路部分(digitalprocessing and communication unit ,DPCU) 则基于65nm低功耗 CMOS 工艺实现。其中2×8×8个SPAD共享一个TDC电路。TDC电路达到了14bit分辨率。传感器的三维集成结构以及像素连接方式以及无源淬火电路结构如图11所示。其测量距离达到150~430m,测量误差为0.3%~0.4%。

图11. D-TOF视觉传感器的三维集成结构、像素连接方式以及无源淬火电路结构

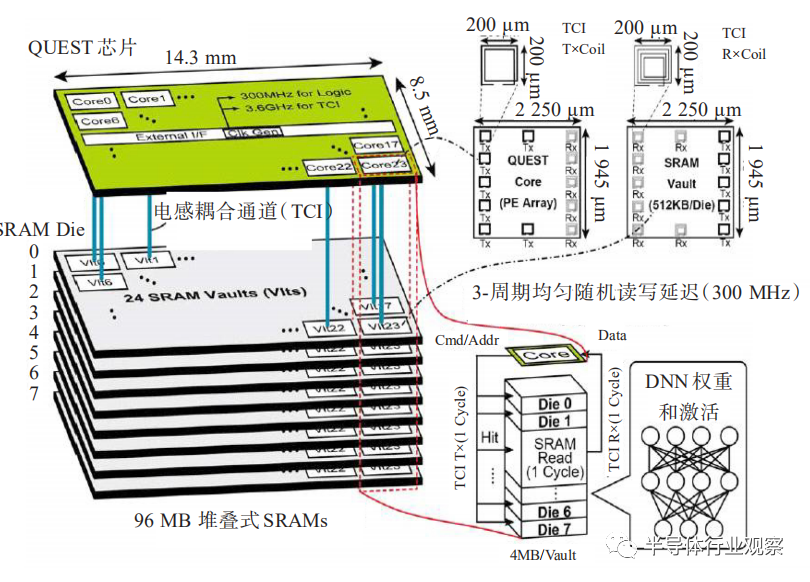

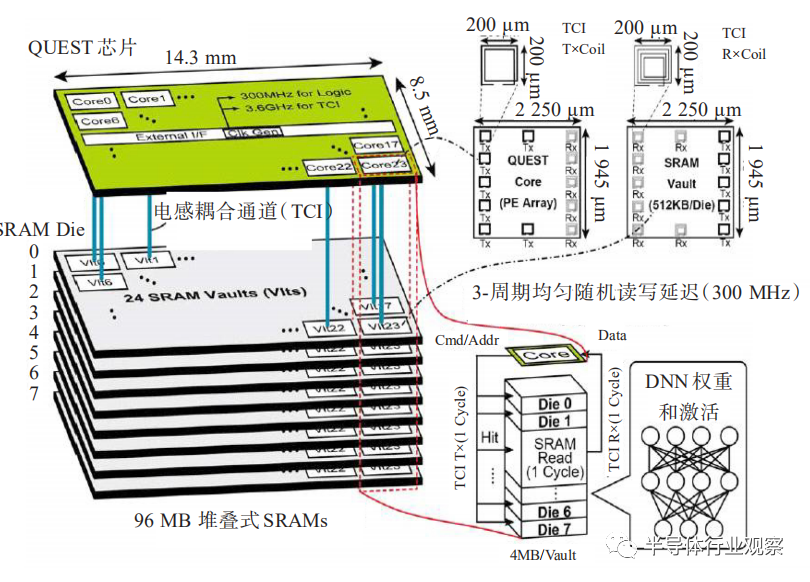

为了能够更好地加速深度神经网络(deep neuralnetwork,DNN),通常需要采用大容量以及高带宽的片外存储器。2018年 ,日本北海道大学采用三维集成技术实现了DNN电路与大容量SRAM电路的集成,所实现芯片的基本结构如图12所示。芯片均采用40nm低功耗CMOS工艺实现,其中SRAM电路包括8个SRAM芯片,总存储容量为96MB,DNN电路包括1个深度神经网络芯片(其中包含24个工作频率在300MHz的处理核)。芯片与芯片之间的数据传输采用24通道电感耦合无线通信技术实现(inductive-coupling technology,ICT)以减少TSV的数目以提高数据传输的可靠性,总数据传输带宽达到28.8GB/s,而芯片的电源和地则采用TSV技术实现互联。最终实现的芯片面积仅为14.3 mm×8.5mm,其峰值运算速度达到7.49TOPS@1bit。

图12. 采用三维集成技术实现DNN电路与大容量SRAM电路集成

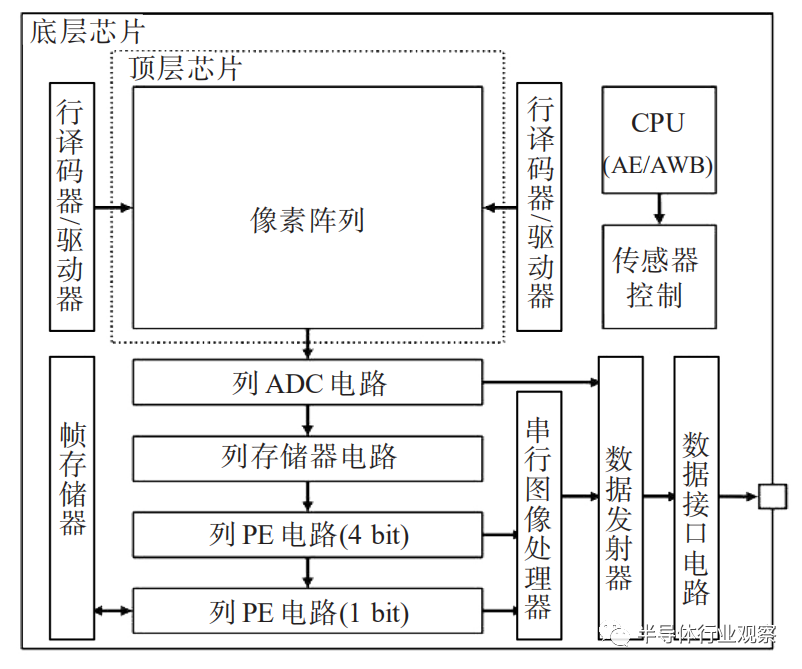

高速视觉芯片结合了高速图像采集和高速并行图像处理的功能,可用于对设备的实时响应和精确控制,然而传统的二维高速视觉芯片中集成了大规模的处理电路,难以达到较高的成像质量和优化的图像处理能力。

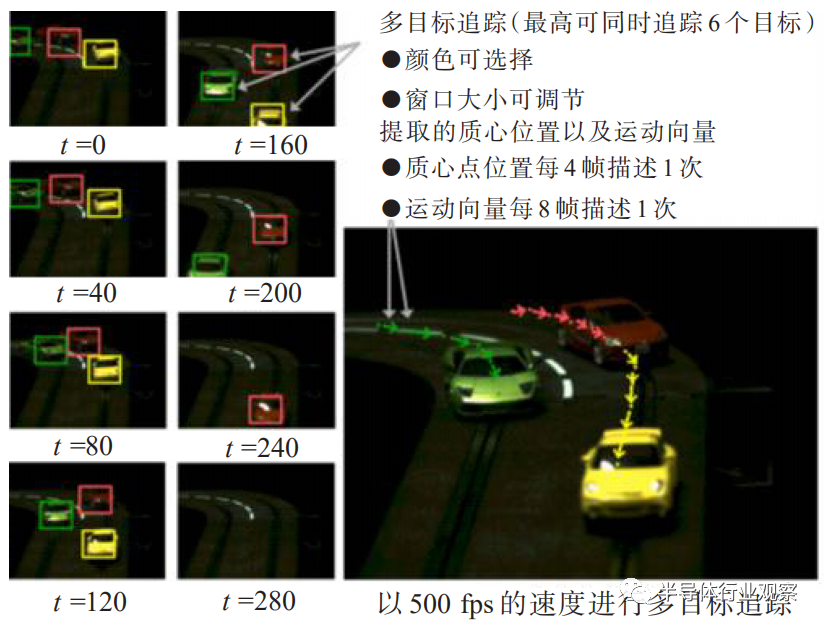

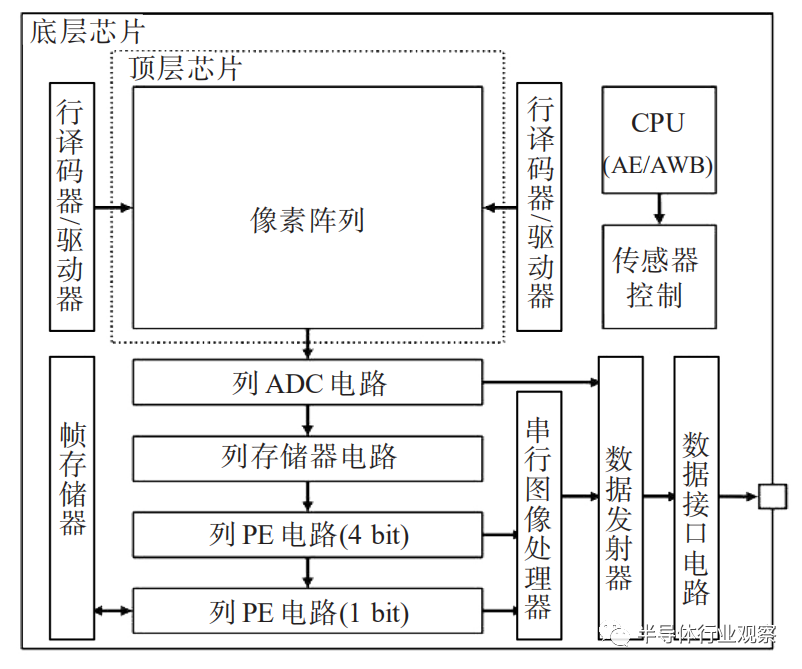

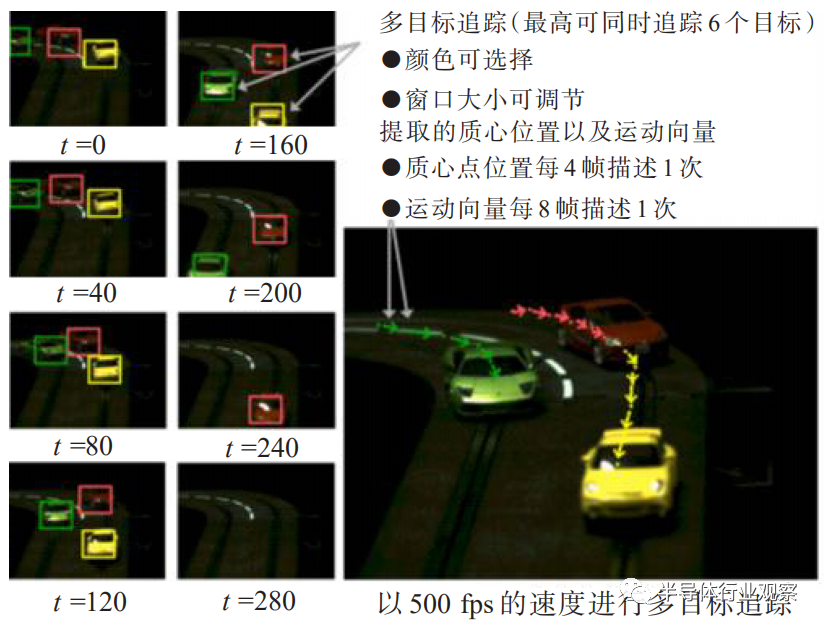

2017年,Sony公司提出了一种采用列并行式单指令多数据(programmable single instruction multipledata,SIMD)PE单元的三维集成高速视觉芯片,芯片可支持目标识别、追踪以及特征提取等功能。其中视觉传感器采用了90nm 1P4M背照式CMOS图像传感器工艺 ;而信号处理电路则采用了40nm1P7M CMOS工艺。芯片可在1296

H

×976

V

全分辨率模式下以500帧/s@4bit的速度进行图像采集,灵敏度超过50000e-/lx-s,同时可实现140GOPS@4bit 的图像处理能力,能效达到0.23mW/GOPS,整个芯片尺寸仅为5.67mm×4.5mm。芯片架构以及采用该芯片实现多目标追踪的效果图如图13和图14所示。

重点介绍了光电融合的三维集成人工智能视觉芯片,包括超高速成像、三维成像和宽光谱太赫兹成像等超越人类视觉水平的图像传感技术;基于仿生机理的高能效视觉处理芯片以及三维集成视觉芯片的相关研究进展。光电融合的三维集成人工智能视觉芯片正朝着超越人类视觉感知能力和智能化、高速、小型化和低功耗方向发展,有望突破当前人工视觉芯片面临的瓶颈问题,具有重要的应用和研究价值。

冯鹏, 刘力源, 吴南健. 光电融合的三维集成人工智能视觉芯片[J]. 微纳电子与智能制造, 2019,1(3): 75-84.

FENG Peng, LIU Liyuan, WU Nanjian. Photoelectric and 3D integrated artificial intelligent vision chip[J]. Micro/nano Electronics and Intelligent Manufacturing, 2019,1(3): 75-84.

《微纳电子与智能制造》刊号:CN10-1594/TN

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2300期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

中国半导体|苹果|封测|

蓝牙

|设备

|晶圆|英伟达|射频|台积电

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!