两大应用驱动,扇出型封装前景看好

2020-05-06

14:00:17

来源: 半导体行业观察

来源:内容来自「

CTIMES

」,谢谢。

5G时代来临代表的是一个高频通讯的概念,而人工智慧则是代表高度的概念,所以高频和高度这2个名词,将会是代表未来芯片的封装技术在新一代的研发过程当中,所需要面对的挑战。

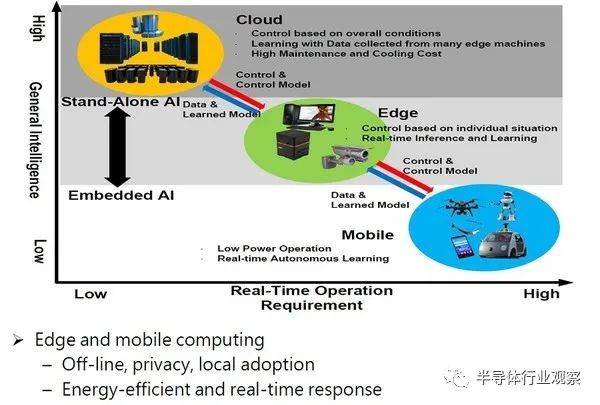

过去AI芯片几乎是运用在云端,因此大多是掌握在Facebook、Amazon或是Google上,因此在AI芯片制程的技术与市场规模上面,并没有太大的推动力。不过,从2018年开始,出现了一个很大推波助澜的效应,也就是说,Edge运算的出现,造就Edge端跟云端有很大的差异。

基于这样的趋势带动之下,全球封测与晶圆厂都争相开发高速运算芯片的封装技术,例如透过逻辑及记忆体芯片整合在矽中介层上,来高芯片整合效能,并且利用芯片切割后再整合,来达到降低制程成本(图1)。

图1 : 先进封装产值趋势。(source:工研院,智动化整理)

Edge端应用所带来的挑战和变化是,首先,在Edge端的市场里通常AI芯片的单价不能太高,因为来自消费者市场阶层的要求,不可能拿云端的AI芯片在手机里面,因为云端的AI芯片价格最少一颗要1000美元,而目前高阶手机的均价也都是在1000美元左右,所以不可以为了一支具有AI能力的手机,来加购一颗1000美元的AI芯片,所以芯片成本永远是一个很重要的因素。

其次是,在Edge端会有耗电的问题,不像云端的取电是经由市电或电源供应器,可以己乎永无止尽的获得电力支援。因此对于Edge端所需的AI芯片耗电量就需要考量的。因此成本、耗电量跟体积这些事情,造就了面对新一代AI芯片的封装呢,就不能用云端的概念去思考(图2)。

图2 : AI运算从Cloud端到Edge端。(source:HJ Yoo(KAIST), ISSCC 2017)

因此在面临高速通讯与AI的需求来说,Edge端的市场结构必须和云端的思考做一个切割,把跟Edge端独立变成一个商业市场来看,但是要面对这样的一个新到来的Edge端市场,就免不了又要出现数量、价格的竞争需求,以及被期待的庞大市场商机。所以可以发现吸引了台湾业者先后涌入开发相关的产品。

但是就目前来说,AI芯片有4大问题,首先AI芯片不是一个通用型,而仅是半通用的架构,需要面对各种不同的运用跟情境设定,因此AI芯片需要客制化。其次,内建的memory要更低的耗电能力,可携式产品的运用情况之下,就会有电池供电的问题存在,因此你的记忆体就不能耗太多力量。第三就是如何将这些AI芯片记忆体、CPU甚至未来所需的感测器整合在一起,因为这是把不同的Node整合在一起,因此这对于封装来说是一个很大的挑战。

最后就是一个AI系统的软件开发,因为AI的应用几乎都是客制化,因此不可能为了每一个客制系统,去反覆修改、测试和调整,因此最佳的期望是在软件的开发过程当中,就可以把各种条件和要求做出来,再确认这样设计是可行的,才开始进行芯片的设计开发,进而缩短整个设计过程。

面对上述的种种问题,未来AI的硬体加速器会有几个趋势和要求,包括Low Power、Low Latency、Data Reuse和Data Locality。尤其是Low Power和Low Latency这2项就需要让封装业者花很多时间去解决(图3)。

图3 : AI硬体加速器需求(source:工研院)

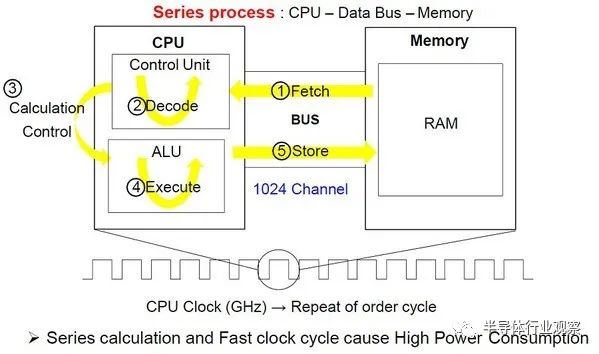

就Von-Neumann影像辨识架构AI芯片来看,在HPC里面的系统需要置入CPU与Memory。当从CIS获得影像之后,先存放到Memory,然后再去把原来放在里面的资料取出,再送到GPU里面进行prediction后再回传,如果比对有误,就需要重新再找一笔资料,所以基本上来它的整个cycle是1到5的一个循环(图4)。

图4 : 利用逢纽曼架构产生高耗工运算(source:KAIST)

基本上,需要1024个Channe个I/O来进行传送。因此整个运算过程当中,需要这么多的步骤被执行,假设能够将功率消耗降低的话,才有办法能够让资料量变快。对于以PCB与IC所设计出来的云端AI系统来说,根本不会担心电力问题,但是对于应用在可携式产品上的EDGE来说,就没办法了。

因此必须透过更先进的3D封装技术来达到期望,因为3D的话,芯片之间传送的路径最短,也就代表耗电量最低。但是,以目前的技术层次来说,3D基本上还有很多问题。因此,目前众多业者仍旧把大部分的精力放在改善2.5D封装技术上,透过各种方法来改善耗电量,然后能够真正在可携式产品端使用。对于这方面,目前TSMC和INTEL都有一些概念提出来,希望能够解决这样的问题跟成本。例如,TSMC提出了一个SoIC概念,而INTEL则是提出EMIB(图5)。

图5 : 多芯片异质整合SiP方式。(source:工研院)

因此相信在短时间的1、2年之内,会有很多2.5D、2.1D甚至2.XD被提出。所以基本上整体来看,其实都是因为运算所带来的需求,前述的AI两个大问题,一个是功耗,另一个是速度的问题。那速度的问题除了将配线做的更细之外,因为同时间要有更多的记忆体,所以Die的厚度会变的更薄,这就是一个大问题。

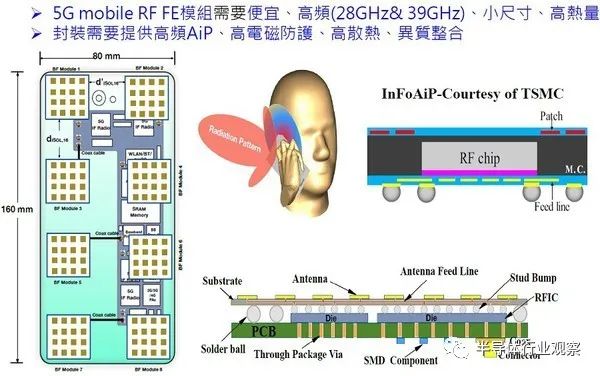

在芯片中Data的部分,因为5G的频段比较高,因此呢它容易受到一些所相关的阻隔,因此在手机芯片设计上,芯片在封装时都会加上AiP(Antennas in package),为什么Antennas in package变成非常重视?这个因为基本上利用传统的PCB没有办法实现天线的结构,所以才会利用封装的Wafer Level Processes将天线置入,并且将天线缩小,因为现有的4G通讯环境之下只需要一个天线就够了,一个大片的天线就可以进行讯号的传送接受了,但是相对的呢整个功率跟能量的损耗会比较大。

不过,面对更高速的应用,就无法以目前的技术来因应,因此在最近这几年全球的芯片业者都相当积极的开发AiP的封装技术,就是因为在系统端面对28 GHz、38 GHz的频段时,是无法利用single pattern的方式达到,所以一定要用阵列方式,但又无法放入封装里,因此这是一个很大的挑战。

图6是一个RF chip上面有天线,而另外一种较简单用Fan Out的模式,把模封材料(Molding Compound)整个应用在AiP,但是高频的情况之下会有电磁干扰,因此模封材料原先不是用来做电磁干扰,只是用来做保护。

图6 : 因5G带动的RF FE模组新需求。(资料来源:工研院)

封装从DIP等技术开始,模封材料本来的责任就是指要保护芯片不要受到外面的伤害,但是到现在,不仅仅保护的功能还能在上面做线路的置划。在这种情况之下,模封材料现在责任越来越大,以前只是配角,但是现在已经快变成主角,因为有很多的应用都会利用模封材料来当作一个载板,以及高频的隔离和散热,所以呢对于整个来说,因为新的需求,所以模封材料会有一个很大的挑战。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2301期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

中国半导体|苹果|封测|

蓝牙

|设备

|晶圆|英伟达|射频|台积电

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie