来源:内容由半导体行业观察(ID:icbank)编译自「

mynavi

」,谢谢。

在半导体行业中,“微缩(Scaling)”是一个经常出现的词语,比方说,我们经常在半导体行业的新闻中听到有关晶体管微缩(即把纳米级(Nano-scale)的尺寸缩小至原子级别)的信息。或者,我们又曾听说过,我们日常使用的智能手机等电子设备由于采用了容量较大(Scaling)的存储半导体,因此能够存储清晰度较高的视频。无论什么样的新闻,基本都意味着微缩(Scaling)的进步。

以上这些进步都是由元件接触面积(Footprint)的缩小、三维结构的扩大、新材料和革新结构的采用所带来的效果。如今的数字时代因以上这些技术的发展和进步而得以成立。如今,使我们的日常生活发生翻天覆地变化的电子设备是由于微缩(Scaling)而得以诞生的,而且,今天的我们只需动动手指就可以获得海量的数字信息。

就半导体的微缩(Scaling)而言,摩尔定律是众所周知的。即当价格不变时,集成电路上可容纳的元器件的数目每隔18个-24个月便会增加一倍,性能也将提升一倍。

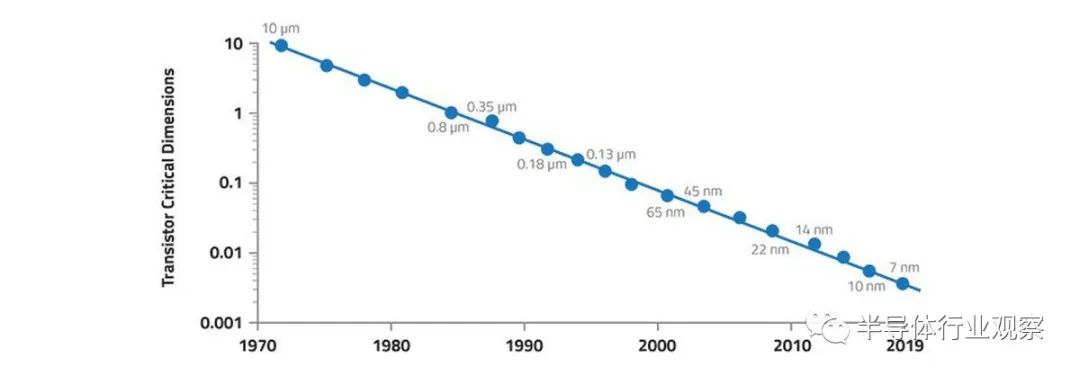

最近几十年来,随着光刻(Lithography,在晶圆表面影印成线路图案的加工技术)和等离子蚀刻(Plasma Etching)技术的进步,半导体行业正在逐步缩小晶体管这一重要的(或者说是不可或缺的)构成要素,且获得了较大的发展。

此外,就半导体的技术节点(Technology Node)而言,一般指的是晶体管的闸极(Gate)的长度。比方说,所谓0.5um的技术节点指的就是闸极(Gate)长度为0.5um的晶体管。但是,随着时代的发展,技术节点的定义也在变化,如今不再是晶体管相关的主要部分的尺寸指标,而仅是指代元件的代际的名称。但是,随着节点的微缩发展,人们对于提高元件的性能和功率、削减生产成本的目标从来没有改变过。

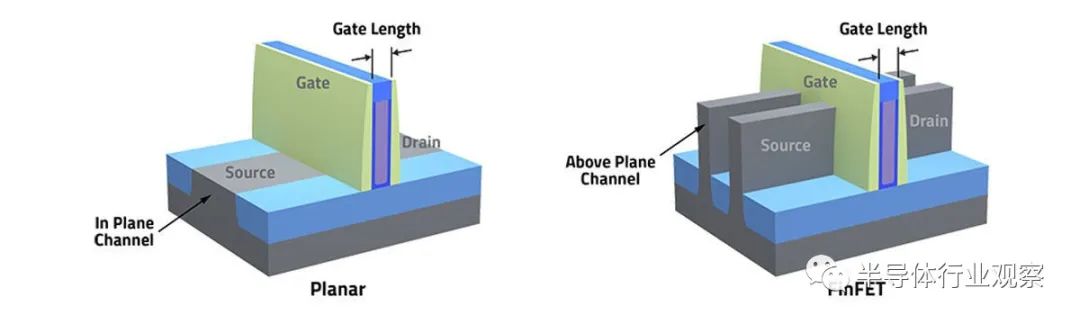

高性能晶体管在20nm节点前后达到了微缩的极限。半导体行业的工程师们不得不探索其他设计晶体管的方法,因为如果缩小平面型(Planar)晶体管的水平尺寸,将会产生其他问题。

就三维FinFET(鳍式场效应晶体管)的结构而言,晶体管的主要构成要素相对于硅晶圆而言较立体,因此不会减少晶体管的沟道(Channel)的容量,而是缩小元件的接触面积(Footprint)。就FinFET的微缩而言,作为提高元件性能的方法,一般是在提高Fin的高度的同时,为提高每个单元(Unit)面积的元件密度而缩小水平尺寸。

为了维持晶体管的微缩,以及获得高性能、低功耗、低成本的元件,近年来实施的方法是往硅里添加锗(Germanium),但要用FinFET技术超越5nm的节点,还是需要新材料!此外,压层纳米板(Nano Sheet)、纳米线(Nano Wire)等新的材料很有可能成为新的解决方案。要对这些新材料进行加工,毫无疑问,微缩是必须的,且灵活运用原子层级别的成膜以及蚀刻工艺都是必须的。

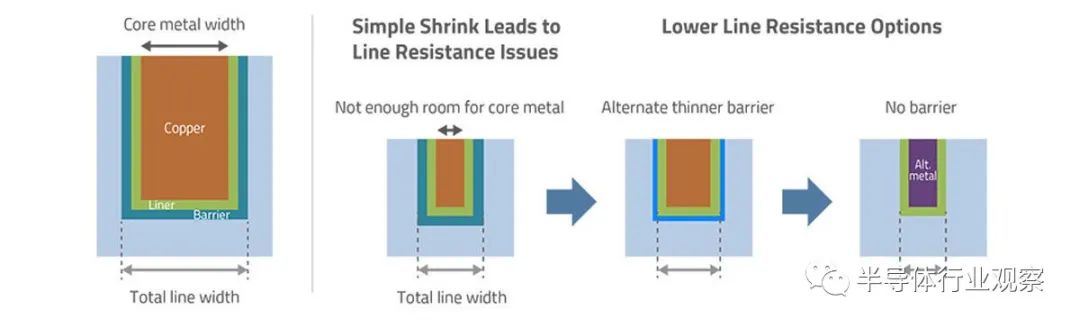

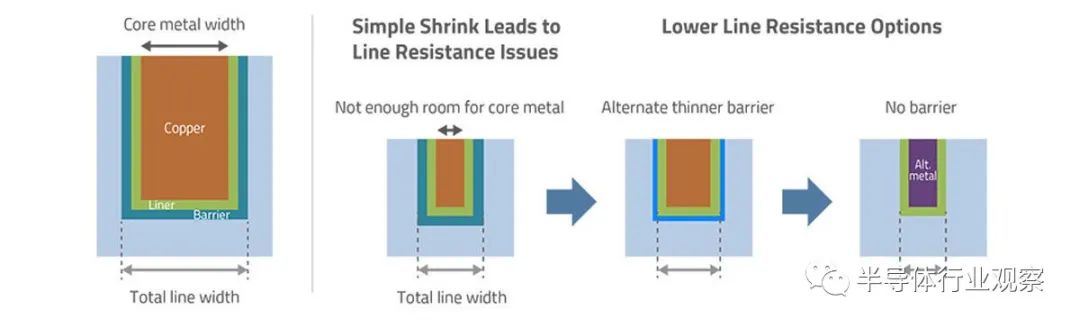

如果缩小晶体管的尺寸,为了连接晶体管、排线层,就需要整体缩小接触(Contact)层的尺寸。随着代际的进步以及局部内部联系(Inter-connect)的密度越来越高,如果进一步推进微缩的发展,如今主流的铜配线将会面临严重的课题。比方说,如果要进一步降低配线的宽幅、高度,则铜配线的电阻将会大幅度增高。半导体生产厂家在灵活运用既能防止铜污染又具有较高电阻值的新阻挡(Barrier)材料、新衬垫(Liner)材料的同时,力求减小阻挡(Barrier)层、衬垫(Liner)层的空间。另一种可能性是使用一种不需要阻挡(Barrier)层的其他金属来取代铜,或者使用其他金属与铜的合金。

(图片出自:mynavi)

(图片出自:mynavi)

存储半导体容量的微缩(Scaling)--即容量的扩大

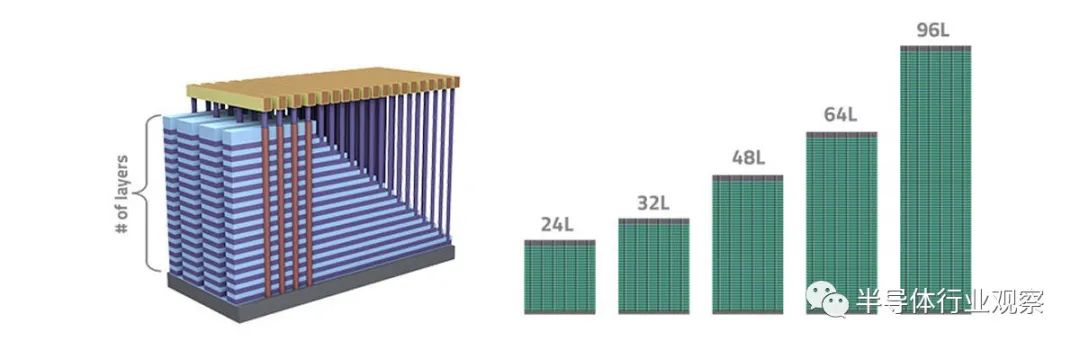

3D NAND的存储半导体容量的微缩(Scaling)是通过垂直方向的堆叠来实现的。就存储半导体的结构而言,单元(Cell)密度与堆叠层的层数成比例地增加。初期的3D NAND一般采用的是24层构造的芯片,如今96层、128层构造的芯片已经量产,因此预计堆叠层数将会进一步增加。而且,每一层都需要均匀、光滑,且与下层紧密结合,因此堆叠层数带来的课题也增加了。

堆叠层数的持续增加带来了存储半导体容量的扩大,而存储半导体容量的扩大又使具有较高纵深比(Aspect)的存储孔(Memory Hole)的蚀刻、阶梯(Staircase)图形的定义、字线(Word-line)的钨填充等后续工艺更加复杂。此外,如果沟道(Channel)长度变长,电子迁移率会受到限制,影响设备的性能。眼下,人们正在推进运用重要的成膜工艺以及蚀刻工艺来切实推进新代际的发展。

如今最尖端的芯片毫无疑问是迄今为止设计、生产的产品中最先进的元件,也是历经几十年人们推进微缩的直接成果。今天的缩小水平方向尺寸的、谋求纵向堆叠的元件所要求的性能(Performance)和成本(Cost)优势会因为半导体生产设备的进步、生产设备厂家和芯片厂家的强化合作而得以实现。

通过半导体的微缩(Scaling)发展,我们的工作、通勤、娱乐、通信方式获得了翻天覆地的变化。作为改革(Innovation)的方向性,我们期待“More Moore(延续摩尔定律)”可以持续下去。作为支撑半导体行业得以发展的另一个方向性—--将各种各样的技术融合到各种各样的构造、系统中的“More than Moore(新摩尔定律、超越摩尔定律)”战略也颇受瞩目。

未来,我们需要同时推进以上这两个方向的进步,但是,要推进实现更智能(Smart)、更互联(Connected)的社会而必须的速度和性能需要被应用到更多的行业和领中。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2309期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

政策|海思|集成电路|

AI

|CMOS

|晶圆|ARM|射频|台积电

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

(图片出自:mynavi)

(图片出自:mynavi)