来源:内容由半导体行业观察(ID:icbank)编译自「

semiwiki

」,谢谢。

随着该行业进入2020年代,先进封装不仅将成为补偿工艺规模缩小带来的好处的必要工具,而且它们有潜力为具有这种能力的公司提供独特而的优势。许多公司都处在这一转型的最前沿。

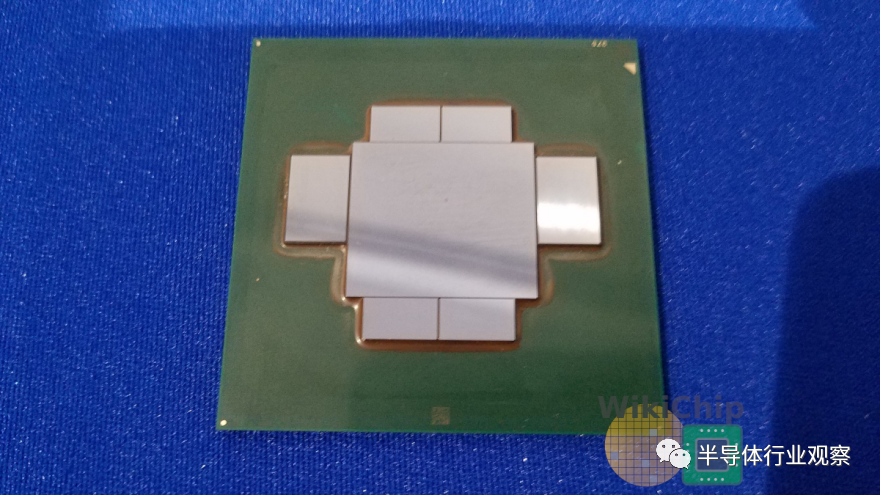

之前,我们报道了台积电的工作成果,其中包括针对高端性能要求应用的CoWoS,广泛的InFO封装流程系列以及他们的3D IC堆叠的SoIC演示。同样,英特尔的高级封装产品组合包括其2.5D EMIB和面对面的3D堆叠Foveros技术。最近,该公司添加了Co-EMIB,将两者结合成一个更复杂的芯片。

与传统的硅中介层相比,嵌入式多互连桥(EMIB)具有许多明显的优势。在大型中介层上需要的地方嵌入一小片硅具有明显的成本优势。第一代EMIB产品已经在许多产品中出货了一段时间,包括该公司的高端Stratix X FPGA和Kaby Lake G移动芯片。

到去年年初,英特尔已经售出了超过一百万种基于EMIB的产品。因为这些都是超高级产品,因此不大可能要分摊其技术成本以摊销该技术的成本,但随着该技术开始在更多产品中出货,足以对其进行改进。像EMIB一样,Foveros可以提供更大的bump密度增加,但是它是通过直接面对面堆叠两个裸片来实现的,因此成本更高。

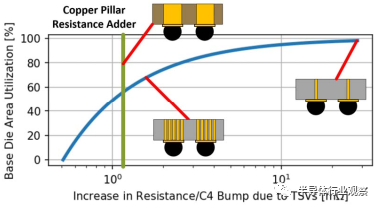

以Foveros为例,它在顶部和底部die之间提供了很高的带宽。为了给顶部die供电,必须通过底部die放置过孔。TSV会增加电阻,尽管可以通过添加更多的过孔来减轻电阻,但会增加面积成本。

最重要的是,将zones拒之门外,以及现有路由拥塞的固有增加加剧了这种情况。据英特尔称,保守的估计是芯片面积增加20%。在某些情况下可能高达70%。然后是散热问题。对于高性能应用,散热是主要关注的问题,因为上面的die会阻碍散热片的路径,从而增加热阻。

传统的硅中介层可通过将裸片分布在大块硅片上来避免此问题,从而实现更好的冷却效果。同样,它也消除了逻辑芯片中对TSV的需求,因此不会影响面积利用率。较大的中介层会增加成本。此外,2.5D解决方案失去了3D封装的优势。这就是英特尔ODI技术的用武之地。

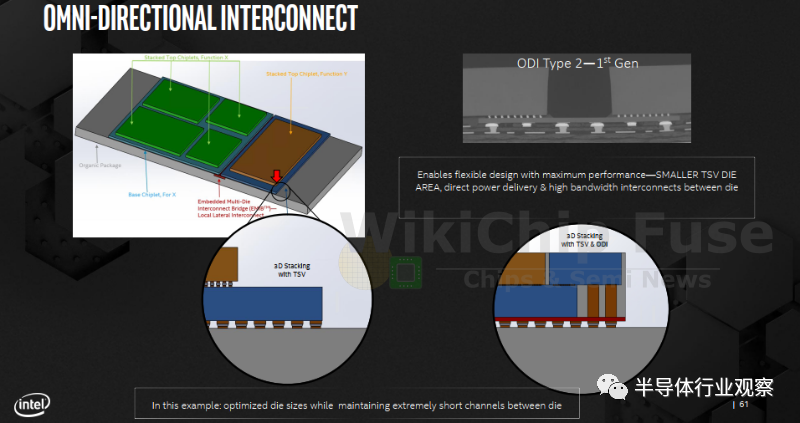

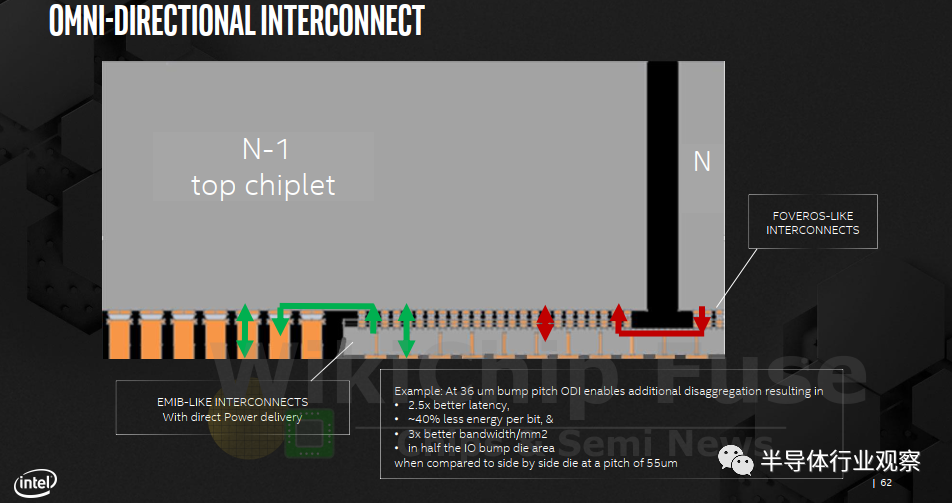

全向互连(ODI)是一整套新的封装互连技术。这是不断增长的封装选择库中的另一种工具,可以在适当的地方加以利用。ODI通过许多3D封装流程弥合了EMIB和Foveros之间的鸿沟,与硅中介层等替代技术相比,这些3D封装流程增强了功率传输和冷却能力。

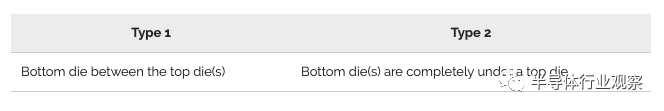

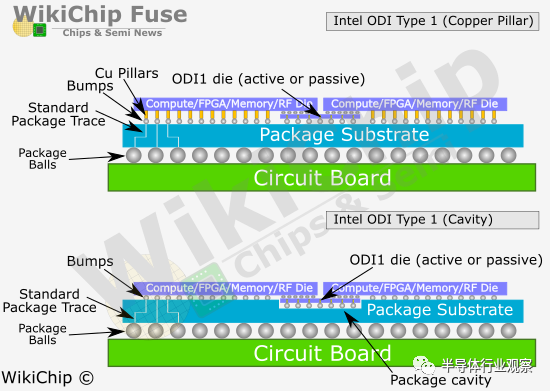

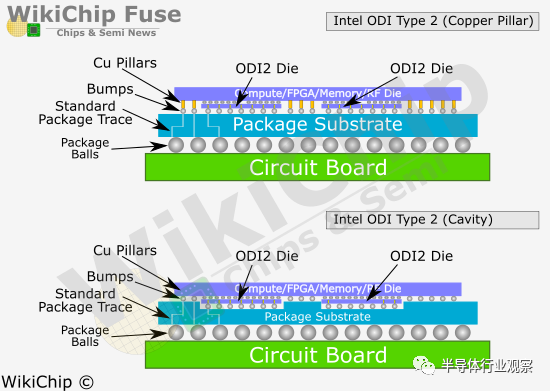

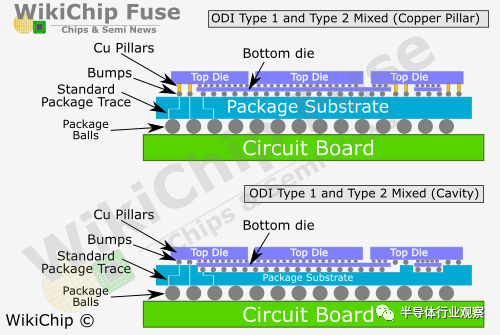

ODI当前有四个变体。当中有两个主要选项,分别为“类型1”和“类型2”。每种类型有两种不同的选择——铜柱(copper pillar)vs腔(cavity)。可以根据需要将所有四个变体组合在一起。同样,底部ODI芯片可以是有源芯片,无源芯片或两者的组合。

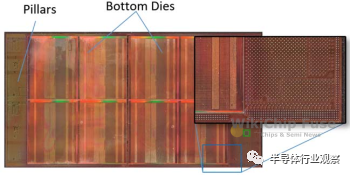

在ODI类型1中,die放置在两个顶部die的下方,或者放置在一个不完全覆盖底部die的单个die的下方。在ODI1中,底部芯片仅覆盖需要bonding的顶部芯片部分,在继承了Foveros样互连优势的同时,消除了TSV的缺点。ODI1可以是被动的,例如在各个裸片之间进行简单的简单路由时,也可以是主动的,例如在多个裸片之间主动路由数据或直接在多个裸片下提供高度本地化的高速缓存时。也可以将这种类型的芯片用于单个芯片,例如带有HBM或其他逻辑的处理器。

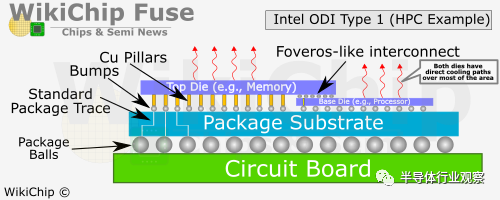

对于更关注热量的高性能应用,ODI1提供了标准2.5D interposers所具有的附加优势,即可以直接进入冷却溶液而没有任何障碍。英特尔提供的一个示例是涉及直接连接到堆栈存储器的微处理器的示例。ODI避免了两个die的完全堆叠,从而为两个die提供直接的冷却液通道。同时,此版本保留了裸片之间的高带宽类Foveros互连,同时消除了对穿过硅中介层的长通道的需求。

从表面上看,Type 1 Cavity版本似乎与标准EMIB非常相似,但是却大不相同。此版本中的ODI裸片实际上并未嵌入硅片中,并且四周都具有路由功能。使用热压键合将基础ODI芯片以受控的高度放置在型腔内。然后,使用TCB固定顶die。通过独立控制底die的高度,他们能够最大化C4工艺。

在ODI类型2中,die完全位于顶部die下方。在这种情况下,就可以将底部裸片精确地定位在所需的位置上,该布线路径最接近顶部裸片中的所需逻辑,这与使用侧边电容器(LSC)的方式大体相同。ODI2可用于增强顶部裸片的优势,例如通过附加其他I / O功能或本地缓存。或者,它可以用于添加另一层主要功能,例如通过将加速器直接连接到处理器下方。

ODI有趣的功能之一是,所有各种选项都可以根据需要在有意义的地方进行混合和匹配。例如,有可能使基础裸片更大,以在Type 2配置中包含多个顶部裸片,而使边缘裸片在Type 1配置中,从而使它们的功率传递可通过铜柱逸出。

英特尔已经推出了令人印象深刻的新封装技术,涉及一系列功能和功能。自从首次公开EMIB以来,已经花费了很多年,直到Kaby Lake G等芯片的生产开始批量生产。鉴于英特尔于2019年末首次公开ODI,我们可能再过几年才会看到这种技术。可能在2022/23的时间范围内,但是随着EMIB和Foveros技术的成熟,我们很可能会看到新技术的进一步集成除了ODI以外的其他功能,也可以更快地投入生产。

★

点击文末【阅读原文】,可查看

本文原链接

。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2313期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

美国|台积电|

RISC-V

|汽车芯片

|

AI

|CMOS

|中芯国际|苹果|射频|

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!