来源:内容由半导体行业观察(ID:icbank)编译自「eetimes.jp」,谢谢。

“IMW 2020”论文集的表纸。(图片出自:International Memory Workshop论文集的第一页)

2020年5月17日-20日举行了在线IMW(International Memory Workshop),笔者自2018年起已经连续三年参加IMW会议,而在线会议还是首次参加。今年的会议中,有关3D NAND的论文数量最多,因此,笔者就各家NAND型闪存(以下简称为:“NAND”)厂家的现状、未来的技术蓝图(Roadmap)展开论述。

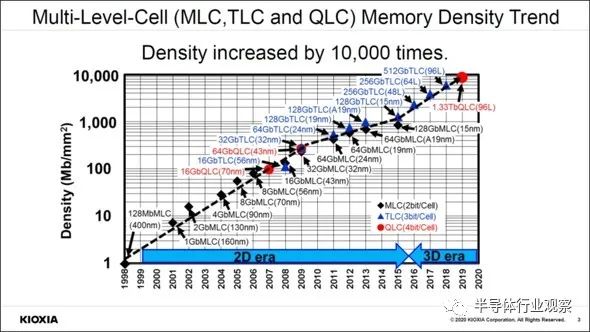

5月17日的会议(Tutorial)“PART I - 3D NAND”中,首位出场的是铠侠(原东芝存储半导体)的Noboru Shibata先生,他在主题为《History and Future of Multi-Level-Cell Technology in 2D and 3D Flash Memory》的演讲中,说明了NAND的历史,如下图1。

图1:NAND存储密度增加的趋势。(图片出自:Noboru Shibata, KIOXIA Corp., “History and Future of Multi-Level-Cell Technology in 2D and 3D Flash Memory”, IMW2020, Tutorials PART 1.)

Noboru Shibata先生以NAND的字位(Bit)为焦点,如上图1展示了2字位(MLC)、3字位(TLC)、4字位(QLC)分别对应了何种细微性、何种存储容量的芯片。

在2009年(32纳米)以后,存储半导体密度的增长趋势呈现了一时的放缓现象,自2016年开始转向3D趋势,且趋势越来越明显。因此,人们普遍期待未来3D化的NAND将会继续扩大存储的密度。

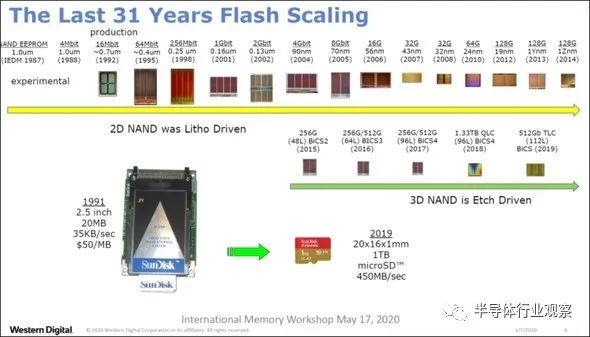

Shibata先生的演讲之后,WD的Yan Li先生做了题目为《3D NAND Architecture and its Application》的演讲,其中提到31年来NAND的细微化全过程。如下图2所示。

图2:NAND存储密度增加的趋势。(图片出自:Yan Li, Western Digital Corporation, “3D NAND Architecture and its Application”, IMW2020, Tutorials PART 1.)

1987年在IEDM上公布的NAND的细微化为1um。此次的发言者应该是NAND的发明人—舛冈富士雄先生(笔者推测),在次年的1988年,以1um生产出了4M bit的NAND,1992年以0.7um发布了16M bit。自此,东芝的NAND业务开始正式启动。

后来,随着细微化、高度集成化的发展,2014年以1Znm(应该是15纳米)发布了128Gbit的NAND。但是,后来由于发生了近邻存储单元(Memory Cell)之间的串扰(Cross Talk)问题,放弃了2D的细微化,自2015年开始转入(Paradigm Shift)3D时代。而且,除了细微化,还开始了在纵向堆积更多层数的“多层化”发展。

这种多层化以48层、64层、96层(约1.5倍)的形式发展,可以推测,下一步应该是1.2倍的112层。

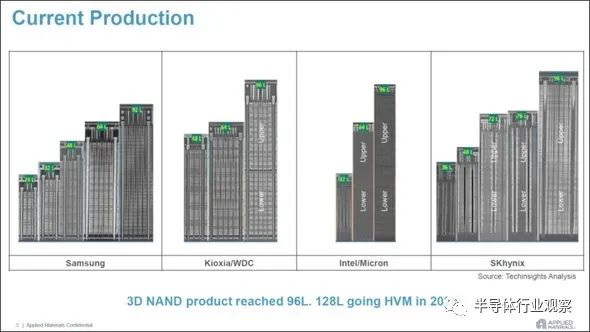

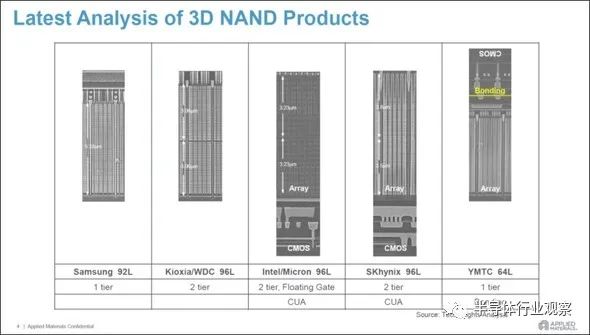

会议(Tutorial)“PART I - 3D NAND”的第三位演讲者是Applied Materials(AMAT)的Tomohiko Kitajima先生,演讲题目为《Materials and process technology driven 3D NAND Scaling beyond 200 pairs》。在这篇演讲中Tomohiko Kitajima先生简明地分析、比较了各家NAND厂商的现状,且说明了未来的技术蓝图。这篇演讲,为理解3D NAND,很有帮助,且演讲者在过程中反复展示了视频说明。下面笔者简单介绍其中一部分。

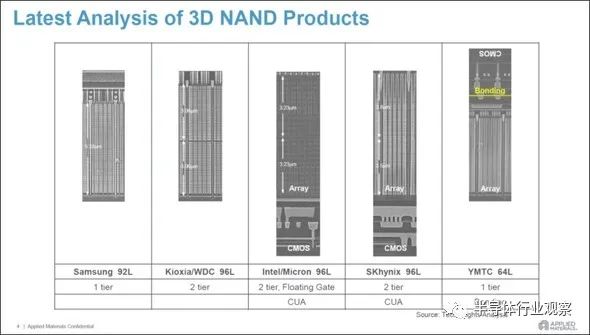

下图3是各家厂商生产的3D NAND的所有断面SEM图,此外,图4是各家厂商的最新的3DNAND的SEM照片与构造。看到这两幅图,笔者感觉很震惊、很有价值。

图3:各家存储半导体厂家的3D NAND的断面SEM照片。(图片出自:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.)

图4:各家存储半导体厂家的最新的3D NAND的比较。(图片出自:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.)

行业先驱--三星(Samsung Electronics)直面的问题

下面我们再看下一图3,仅从这一张图我们就可以看到各家集团公司的技术、战略、面临的问题等信息。

三星(Samsung Electronics)正在推进24层、32层、48层、64层、92层以及3D的的多层化发展,由于中国西安工厂大量生产并最先开始出货的是48层,因此可以判断24层、32层是样品交货。三星是最先开始出货48层产品的,且已经发售64层产品,因此可以断言三星控制了48层和64层的市场。

业界普遍认为三星竞争力的来源在于纵横比(Aspect Ratio、AR)较大的内存孔(Memory Hole)的干蚀刻技术(Dry Etching)。三星通过与Lam Research共同研发,开发了AR较大的HARC(High Aspect Ratio Contact)蚀刻设备与技术,远远领先于其他公司。

此外,在64层的下一代产品上,三星“摔了一个大跟头”,尽管其他公司已经开始生产96层,只有三星在生产这种处于中间位置的92层的产品。此外,从断面图的高度来看,三星的92层纵向高度明显比其他公司的96层低了很多。

主要原因如下:铠侠与WD等其他公司的96层是利用两个48层堆叠而成的,然而仅有三星采用了一次性加工的方式、进行内存孔(Memory Hole)的HARC蚀刻。

也就是说,AR越大,HARC蚀刻的难度也越大。具体而言,蚀刻速度会呈现指数级的降低,且会发生各种异常情况,如很难控制内存孔(Memory Hole)的方差。

为此,三星将纵向的层数做成92层(比其他公司少了4层),进一步将存储单元(Memory Cell)朝纵向收缩,尽量把HARC的AR做得更小。据推测,三星的92层的产品良率十分低。

尽管如此,三星在2019年11月19日公布说,新一代的128层也会采用一次性加工的方式进行生产。笔者认为,与其拘泥于一次性加工的生产方式,不如再研发其他新的生产方式,因此三星的未来堪忧。

与由于对HARC蚀刻技术怀有较大的信心而“摔了跟头”的三星不同,铠侠和WD通过96层产品统领了全球市场。根据笔者从供应链等处得到的信息来看,在2019年时间点的第四季度,日本四日市工厂的96层的稼动产能是三星的3倍-4倍。

在64层之前,铠侠和WD在HARC蚀刻技术方面,都远远落后于三星。因此,他们尽早地将堆叠两个48层应用到了96层上。

从图3 来看,就96层而言,三星以外的其他厂家都分为Lower和Upper。在这种双层堆叠方式形成96层的情况下,很难将12英寸晶圆完美地与将近约2兆个内存孔(Memory Hole)贴合。据推测,即使在四日市工厂,也曾因为这个问题而导致产品的良率低下。

此外,自2019年夏季开始,行业的趋势就变化了。笔者从就职于铠侠的朋友得知,“如果要我们堆叠500层,我们也可以做到”!就内存孔(Memory Hole)贴合的技术而言,笔者推测他们应该是取得了某种技术突破(Breakthrough)。此外,据笔者调查的各家NAND厂家的稼动产能而言,如上文所述,四日市工厂的96层,具有压倒性的规模。

下面我们再看一下图3,Intel&Micron在64层以后,采用了双层堆叠的方式。此外,海力士是自72层以后(不是64层),采用双层堆叠的方式。

此外,比较一下各家的双层堆叠方式,我们可以看出,铠侠和WD的Lower、Upper的分界线十分明显。因此笔者推测,铠侠和WD为解决内存孔的贴合问题,在Lower、Upper之间植入了某种特殊的构造。笔者认为,正是这种特殊的构造技术使铠侠和WD的双层堆叠的良率大幅度提高、产能远超三星,且顺利地生产96层。

三星由于对HARC蚀刻技术过度自信,导致“栽了跟头”,但是,铠侠和WD及时地放弃了一次性加工的生产方式,所以成功了生产了96层的双层堆叠方式。这让人想起了2020年1月23日逝去的哈佛商业学院的Clayton M. Christensen教授提出的“创新的困境(Innovation Dilemma)”。

下面我们看看下图5,即比较了各家厂商的最新3D NAND的图。此处最引人注目的是中国的紫光集团旗下的长江存储(YMTC,原XMC)的3D NAND。

图5:比较各家厂商的最新3D NAND。(图片出自:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.)

2016年3月,YMTC突然宣布要进军3DNAND。YMTC 以较高的薪资待遇汇集了大批的日本、台湾、韩国等地的半导体技术人员,首先致力于32层的研发。仅仅用了一年的时间就成功研发了32层的产品,且跳过48层直接开始研发64层。同时,2019年9月17日,YMTC成功量产了64层。

就YMTC的64层产品而言,控制数据读取、写入的CMOS线路由一种不同于存储单元(Memory Cell)的晶圆制造而成,分别通过Bonding工艺进行贴合。

为了扩大单个芯片的存储密度,一般采用的是将CMOS线路放在存储单元下部的CUA结构(CMOS Under Array),实际上,Intel&Micron和海力士正是采用的这种模式。但是,YMTC的Xtacking则采用不同的键合工艺!

在2019年第四季度时间点,YMTC的64层稼动产能不足2万个,但是,在2020年4月12日,YMTC发布说,成功研发了128层的、1.33Terabit、QLC的3D NAND。未来,3D NAND的“风向标”可能要发生变化了。

一场出人意料的新冠肺炎促使了远程办公、在线授课、在线诊疗等网上业务的发展。IMW2020也是在线召开的。结果,导致了数据中心(Data Center)的需求暴增,用于服务器的NAND的需求也呈现了爆发式增长。

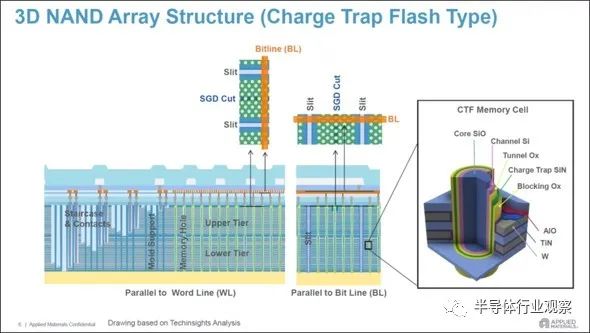

因此,人们对于3D NAND的高密度化的期待越来越高。其研发的R&D的蓝图如下图6所示。如今,各家厂家都在努力推进128层(铠侠和WD是112层)的量产工作。未来,层数应该还是更高,从蓝图上看,2021年-2022年研发200层,2022年-2023年研发250层以及以上。从技术蓝图来看,Charge Trap方式是具有代表意义的3D NAND结构(如图7)。

图6:3D NAND的R&D 技术蓝图。(图片出自:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.)

图7:Charge Trap方式--具有代表意义的3D NAND。(图片出自:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.)

为了实现以上这些多层化,如图6下部所示的研发是必不可缺的。首先, 就左侧的“Architecture Change”而言,会把CMOS线路配置在存储单元格(Memory Cell)的下面(CUA),或者像YMTC的做法一样采取Bonding的方式,增大单个芯片的面积上的存储密度。这种技术已经被多个NAND厂家采用。

所谓的“Vertical Scaling”技术,指的是在纵向可以堆叠多少层的存储单元。此图中清晰地写着未来的发展趋势。首先,有一个单纯地增加存储单元格(Cell)数量的“More Pairs”。其次,有一个“WL(Ward Line)Pitch Reduction”(三星已经采用此项技术)。这是一种纵向收缩存储单元格尺寸的技术方法。运用此技术,如果是同样的Pair数量,由于可以降低Stack Height,内存孔(Memory Hole)的HARC加工将会变得很容易。

此外,如果同时进行“WL Pitch Reduction”和“More Pairs”,迟早会出现“Multi Tiers”(多层堆叠)。三星以外的厂家已经运用到量产产品中。笔者认为,未来三星肯定也会转移到“Multi Tiers”(多层堆叠)。此外,笔者还认为,所有的NAND厂家未来都为朝着堆叠双层、三层、四层甚至更多的方向发展。

另外,作为扩大存储密度的方法,还有一种是“Lateral Scaling”。这是一种通过横向收缩的方式,来扩大单个芯片存储密度的技术手段。“Lateral Scaling”有两种方式,其一为“More Holes b/w Slits”,即将Slit和Slit之间的内存孔的数量由现在的九个增加至十四个。其二为“Hole BL(Bit Line) Pitch Reduction”,即缩小存储孔的直径,使存储孔的密度更高。

但是,这两种研发都需要HARC蚀刻,此外,“More Pairs”的实行还存在很多复杂的问题,各家NAND厂家都需要在元件构造、材料、工艺流程等方面下工夫,在与生产设备厂家以及材料厂家共同研发的同时,推进存储半导体的高密度化。

另外,就像三星掌控了48层和64层、铠侠和WD掌控了96层一样,真正在高密度方面获得突破性发展的NAND厂家才能掌握新时代的霸权。究竟会花落谁家呢?也许我们能在下次在德国德累斯顿(Dresden)召开的IMW2021上看到端倪。笔者明年(2021年)还会继续参加IMW。

生于1961年,出生于日本静冈县。毕业于京都大学研究生院(硕士课程为原子核工学专业),后就职于日立制作所。此后16年中,先后在中央研究所、半导体事业部、设备研发中心、尔必达(因工作调动)、半导体前沿技术公司研发协会(即Selete,因工作调动)从事精密加工技术研发工作。2000年,被京都大学授予工学博士学位。目前,担任半导体产业和电力机械产业顾问及撰稿人,细微加工研究所所长。著有《日本“半导体”的战败》《“电器、半导体”产业大崩溃的教训》、《日本型制造业的败北,零战·半导体·电视机》。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2334期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

两会|台积电|

RISC-V

|汽车芯片

|

AI

|EDA

|中美|晶圆|射频|

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!