来源:内容由半导体行业观察(ID:icbank)编译自「

cool3c

」,谢谢。

科技业「黑色链金术」的半导体,不只有芯片设计和晶圆制造,以封装测试为主的后段制程,更造就了巨大的下游产业。在摩尔定律预期的制程技术演进之外,封装也是充满大量高深学问的专业知识领域,一点都不简单,所以科科们也不要不切实际的期待看完这篇科普文就能彻底了解什么是芯片封装,只要能够记得这些厂商想干哪些好事就够了。

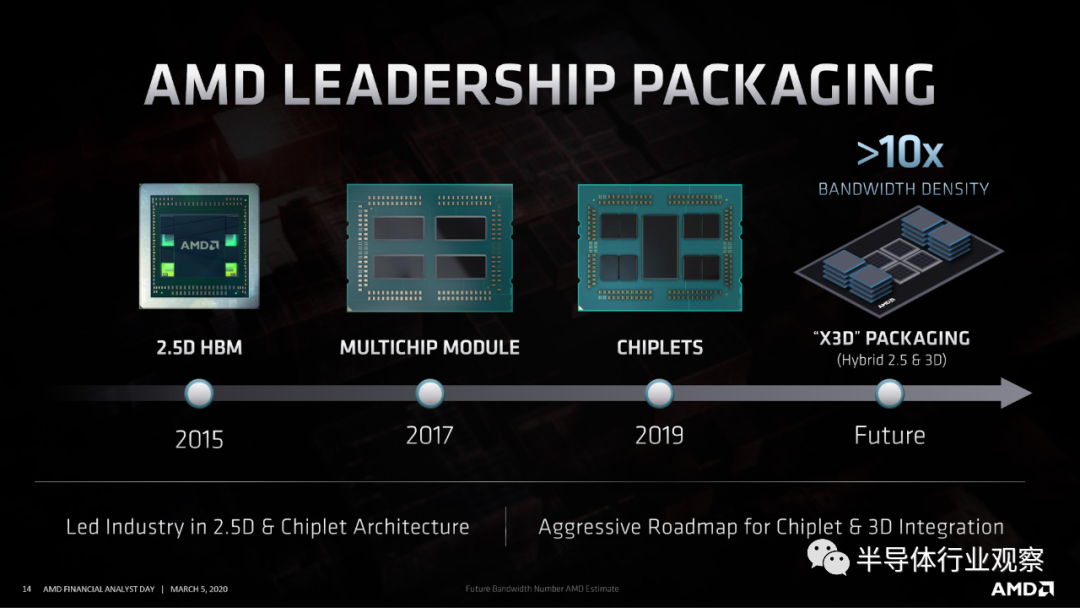

从绘图芯片到x86处理器,AMD近年来大玩多芯片封装(MCM,Multi-Chip Module),甚至在Zen 2世代,连「处理器核心(CCD)」和「北桥记忆体I/O控制器(IoD)」都分而治之,也预计未来将引进融合「2.5D」和「3D」封装堆叠的X3D。此类先进封装技术,也早已是半导体产业的兵家必争之地。

为何需要多芯片封装?把全部功能都做成同1颗芯片不是最省事吗?但天底下没有足以满足「所有功能」的半导体制程,像数字逻辑、I/O、各式各样的记忆体、模拟/射频等,特性都大相径庭,勉强将其「送作堆」,要嘛东西做不出来,要嘛牺牲产品良率,要嘛就是某些功能难以到达最佳化的程度。AMD会将Zen 2分离成几种不同功能的晶粒,不是没有原因的。

也因此,从1990年代开始,多芯片封装类型的产品在市场上屡见不鲜,包含各位科科并不陌生的高效能处理器,透过「分而治之」,让每个不同功能的IP,都位于最适合自己的制程工艺节点。

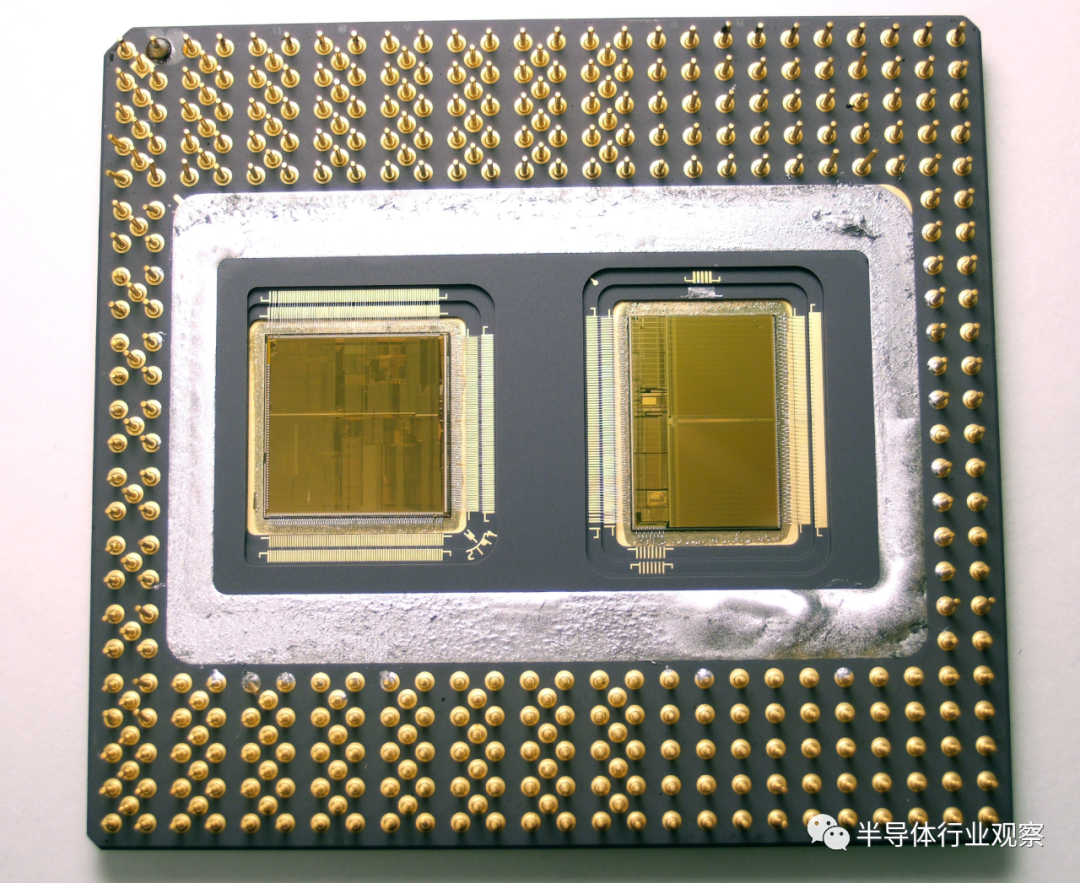

像1995年底的Intel Pentium Pro,将0.50µm BiCMOS制程的P6处理器核心,和256kB L2快取记忆体包在一起。

同时期的NexGen(随后被AMD并购)Nx586-PF,也将0.44µm制程的Nx586和相同制程的Nx587辅助浮点运算器,塞在同1颗封装。

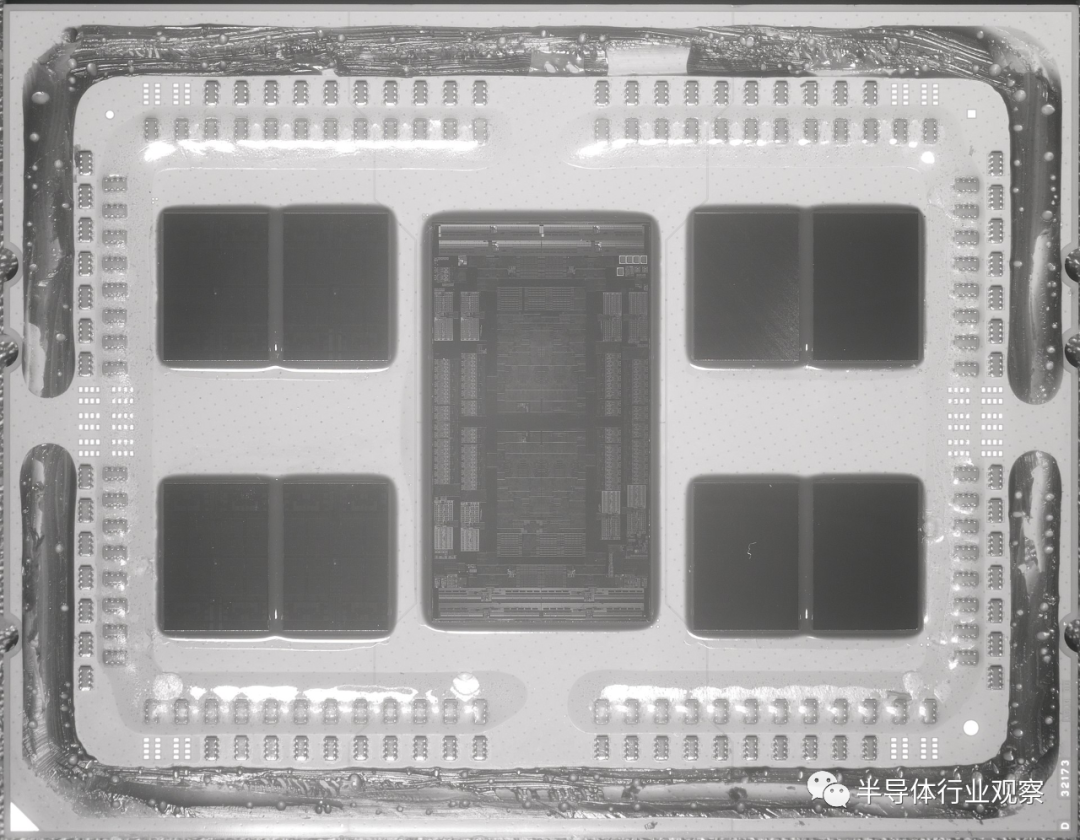

在2004年的高阶伺服器市场,杀遍天下无敌手的IBM Power5,更是将4颗双核心的Power5处理器和4块36MB L3快取记忆体,集中成整块八核心的巨大模组。

关于Intel和AMD,从2005年至今的一长串「双馅水饺」,就不必浪费篇幅讨论了,各位都懂。

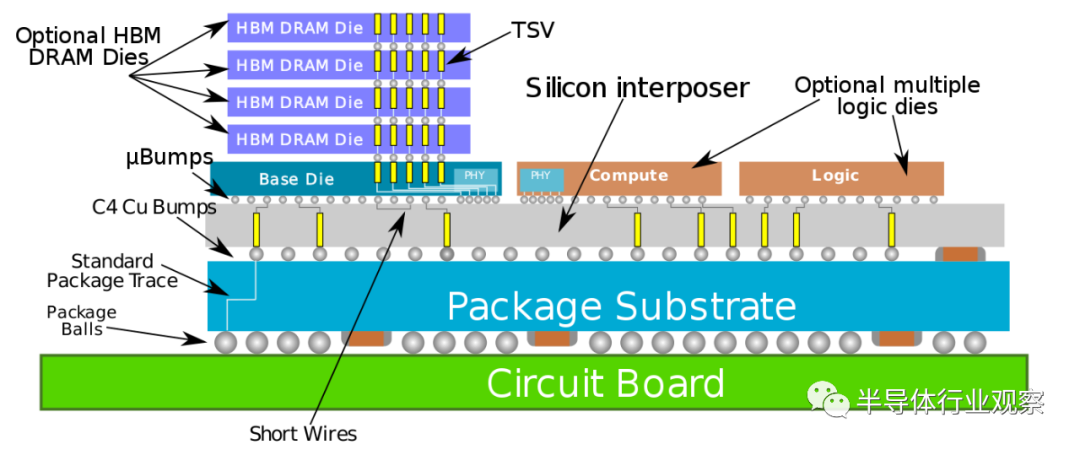

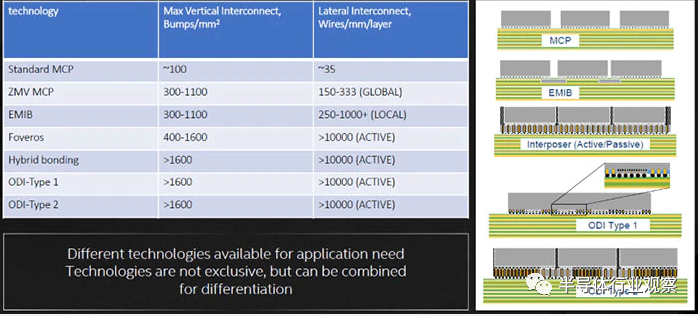

以台积电CoWos(Chip-on-Wafer-on-Substrate)的2.5D封装技术为例,相较于传统的「2D」SiP(System-in-Package),最主要的差别,在于2.5D封装在SiP基板和芯片之间,插入了硅中介层(Silicon Interposer),并以硅穿孔(TSV,Through-Silicon Via)连接上下的金属层,克服了的SiP基板(例如多层走线印刷电路板)难以高密度布线而限制芯片数量的难题。

一大票具备HBM记忆体的高阶产品,从AMD Vega20、nVidia A100/P100/V100、Google的第二/第三代TPU、Xilinx的高阶FPGA、Intel的NNP-T1000(Spring Crest,已被腰斩)人工智能训练处理器、成为Intel人工智慧新欢的Habana Gaudi、Intel的SDN(软件定义网络)交换芯片Barefoot Tofino 2、和日系高效能运算核心Fujitsu A64FX与NEC SX-Aurora,总计超过60个案例,都是台积电2.5D封装技术CoWos的座上嘉宾。

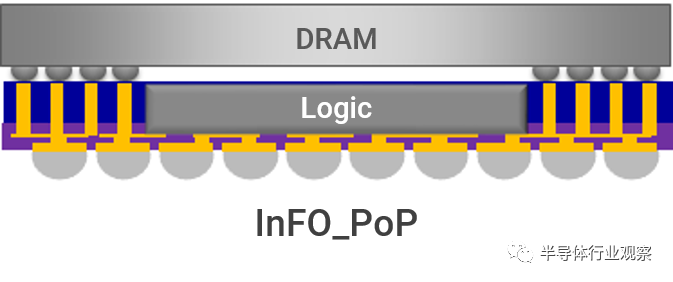

至于台积电的「3D」封装InFO(IntegratedFan-Out),因可减少30%的封装厚度,更是在击败Samsung独家抢下iPhone 7的A10处理器之后(笔者很不幸买到Samsung版A9处理器的iPhone6s),一直爽吃Apple订单的关键。

Intel

阵营:2.5D的EMIB与3D的Foveros

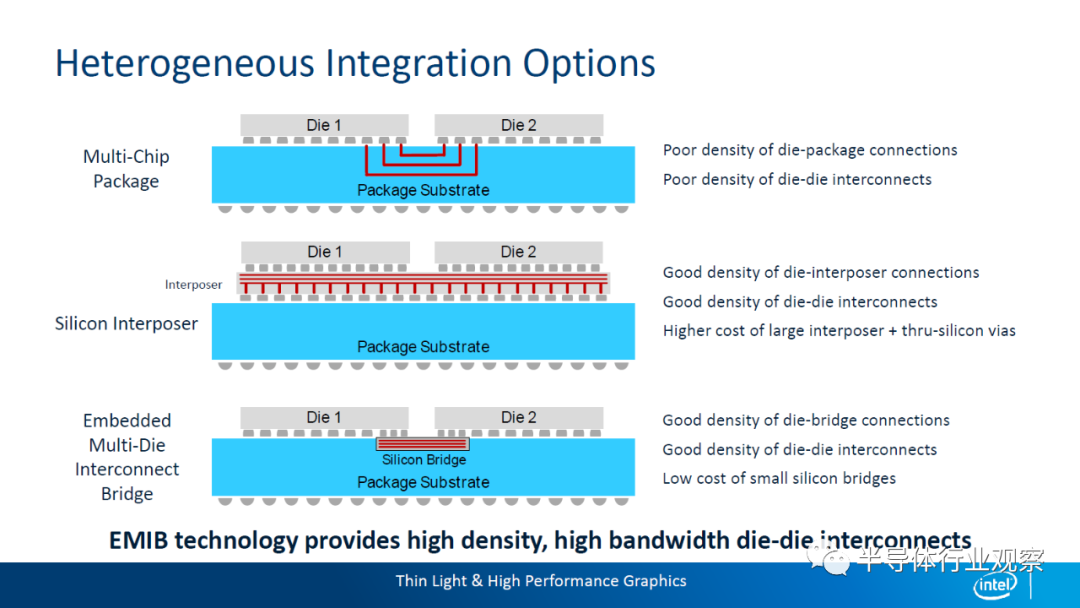

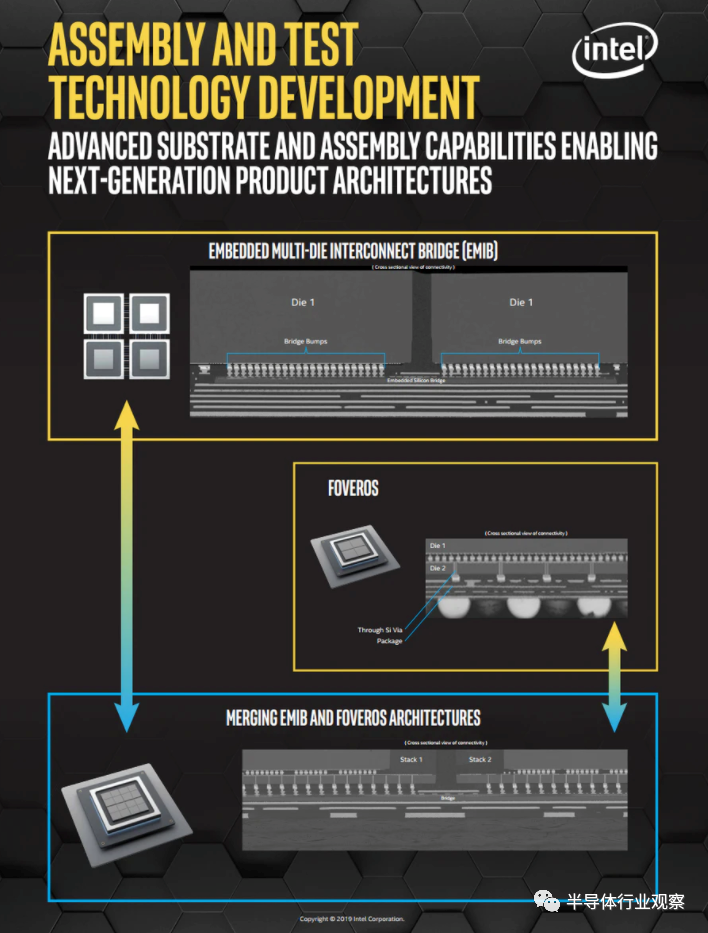

台积电有2.5D的CoWos和3D的InFO,那Intel当然也有:2.5D的EMIB(Embedded Multi-Die InterconnectBridge)和3D的Foveros。

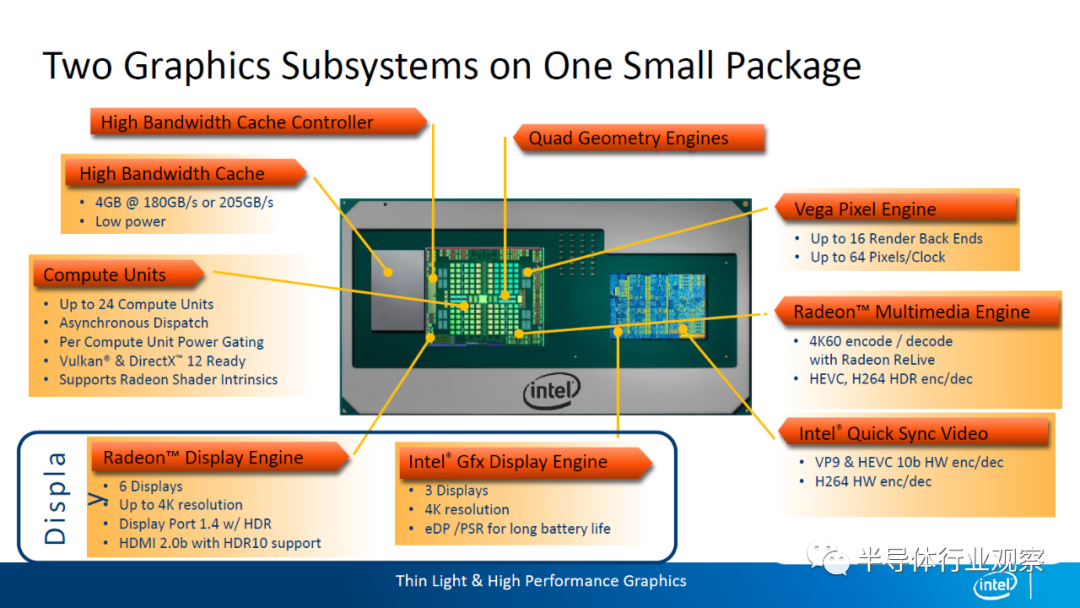

EMIB的技术关键在于埋藏在封装基板内、用来连接裸晶的「硅桥(Silicon Bridge)」,其代表性产品是「黏合」Intel Kaby Lake处理器核心、AMD Vega 20/24绘图核心和4GB HBM记忆体的Kaby Lake-G,与自家的Stratix X FPGA。

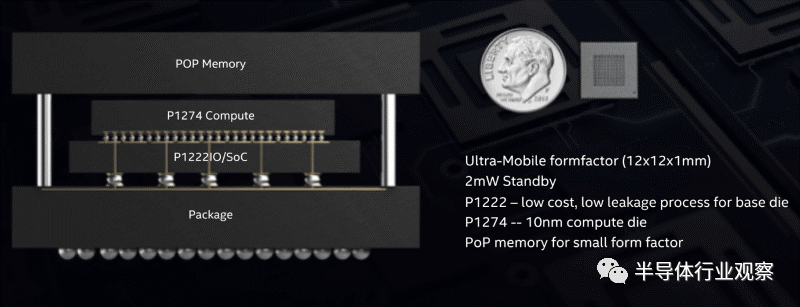

Foveros则是货真价实的3D「叠叠乐」,Intel的Lakefield就堆叠了「1大4小核心」的10nm制程(P1274)运算芯片、22nm制程(P1222)系统I/O芯片和PoP(Package-on -Package)封装的DRAM记忆体。

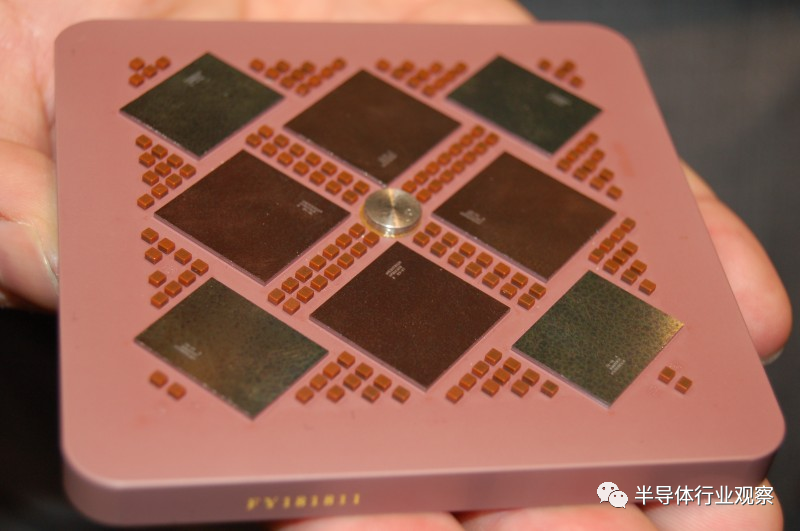

Intel在2019年7月公布的Co-EMIB,说穿了就是用EMIB连接多个Foveros封装,继续叠床架屋成「整合更多功能」的单一芯片。

EMIB和Foveros并非毫无缺点,尤其后者虽然可享受到惊人的芯片之间频宽(毕竟都「面对面」叠在一起了),但要如何替「顶楼」供电却是一大挑战,硅穿孔( TSV)会增加电阻,而提高硅穿孔数量以降低电阻,却又会增加芯片面积(Intel估计是介于20-70%)。

此外,「叠叠乐」也意味着难以散热,因为压在上面的芯片会阻碍热流传导的路径。这也是2.5D和3D之所以会并存的主因,像台积电的InFO,其实也付出了「牺牲部份性能」的代价,不见得适用于高效能产品。

反过来用EMIB把全体芯片「摊平」在同一片硅中介层,固然避免了硅穿孔和散热问题,但这就失去3D封装的所有优点,而且更大面积的硅中介层也意谓着更高的成本。

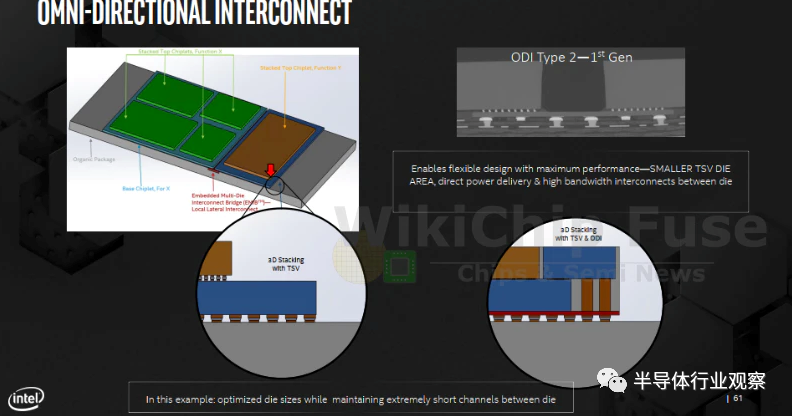

作为EMIB概念延伸的ODI(Omni-DirectionalInterconnect)即为此而生,可兼备2.5D和3D封装的应用,以较低的成本和更容易的散热,实现硅穿孔和EMIB无法达到的性能(每平方公厘1TB/s资料传输量,每资料传输位元0.1pJ热量)。有别于只能横向搭桥的EMIB,ODI四周都有「上下左右均可达」的路由功能,填补了EMIB和Foveros之间的鸿沟,为封装内众多小芯片(Chiplet)之间的连接,提供了更好的灵活性。

藉由ODI,「顶楼」芯片可以与其他小芯片水平互连,类似于EMIB,但亦可运用硅穿孔连接底层芯片,近似于Foveros。ODI的垂直通孔比传统硅穿孔大的多,可降低电阻,并以更少的硅穿孔数量,释放更多的面积,缩小芯片的尺寸,并得到更高的频宽、更低的延迟和更强的电力传输。

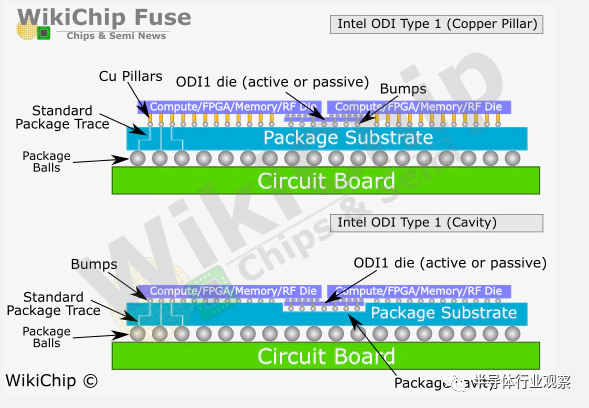

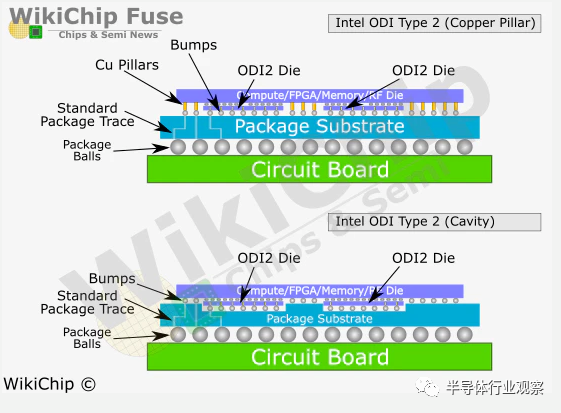

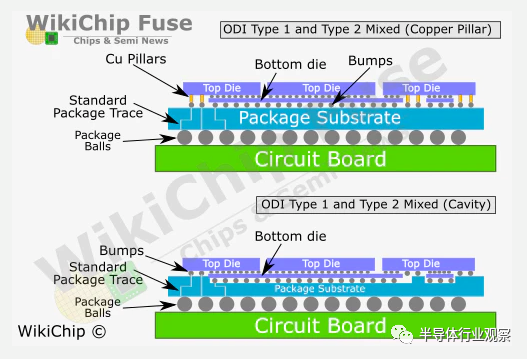

ODI主要有2种应用型式,每种类型还有2种选择(铜柱或封装基板凹洞)。

第一种是连结顶部的芯片(ODI Type 1),这避免了2片芯片的紧密堆叠,不仅利于散热,兼具了Foveros的高频宽优势,并如同EMIB消除了对硅中介层的需求。

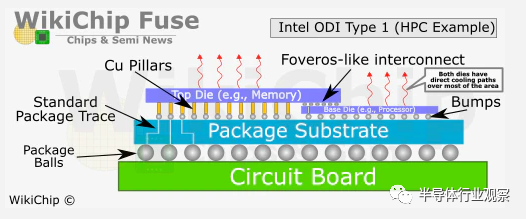

乍看之下好像跟EMIB没什么差异,但下面这个为了高效能运算,让处理器直连记忆体的范例,应该就可以让各位科科比较有感了,然后也可以猜猜看ODI藏到哪里去了。

第二种(Type 2)应用将ODI完全置于芯片下方,用来连接其他的功能单元,如I/O、记忆体或辅助处理器(请各位科科尽情发挥想像力补完这个失落的环节)。

长期关心Intel制程与封装的科科,看到MDIO(Multi-Die I/O)时,可能会当下摸不着头绪,只好像某位市长一样的抓抓头。

事实上,当初Intel在2017年,企图将EMIB用来连接裸晶的「硅桥(Silicon Bridge)」,正名为「先进界面汇流排(AIB,Advanced Interface Bus)」并公开免费授权以「建立产业生态系」。Intel也在2018年将AIB捐赠给美国国防先进研究计划署(DARPA),作为作为小芯片的免专利费互连标准。

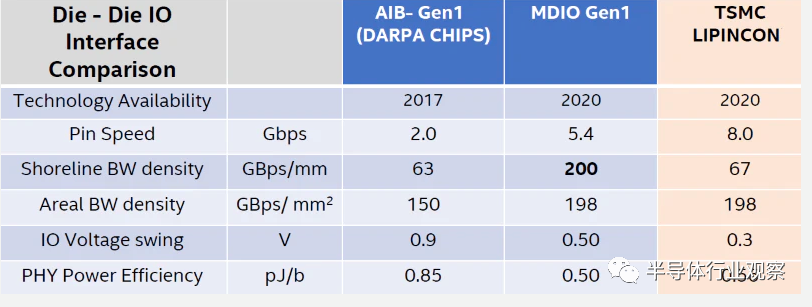

而MDIO则是AIB的下一代,为EMIB提供标准化的SiP实体层介面,可互连多个Chiplet。针脚的资料传输率从2Gbps提高到5.4Gbps,IO电压从0.9V降低至0.5V,并且号称「频宽密度」优于台积电的LIPINCON。但我们也知道,帐面上的技术规格再好是一回事,是否方便让客户导入在实际的产品设计,那又是另一回事,这些细节可暗藏了晶圆代工产业的奥秘。

理所当然的,Intel也在过去的公开活动,多次展示了这些先进封装技术的概念样品,也许我们很快就会看到Intel和AMD一起竞相较量各式各样的「花式包水饺大赛」。

但每次一想到目前在地球上仍不存在的18吋晶圆厂和相关生产设备,回忆起在Intel总部瞻仰过的18吋晶圆样品,看看Intel这两年迟迟未解的14nm制程产能危机和10nm制程良率问题,再回想十多年前这间公司是如何的义气风发的摆出「老子够大可以单独蛮干,领导全体半导体业界的技术趋势」的态度,不拿「干嘛不快点带头冲18吋晶圆抢救产能」这件事出来狠狠的酸一下Intel,真的很对不起过去那位坐在IDF主题演讲台下满脸黑直线的自己。各位科科务必要理解笔者的谆谆苦心啊。

接着,说到AMD的X3D,也差不多该谈谈谣传AMD偷偷进行中的EHP(Exascale HeterogeneousProcessor)计划, 据说某2份神秘的专利权透露出不少有趣的蛛丝马迹,这个容后再谈。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2342期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

半导体股价|台积电|

NAND Flash

|晶体管

|

AI

|EDA

|中美|封装|射频

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!