[原创] 1nm将如何实现?VLSI 2020与会专家有“妙招”

2020-07-13

14:00:03

来源: 半导体行业观察

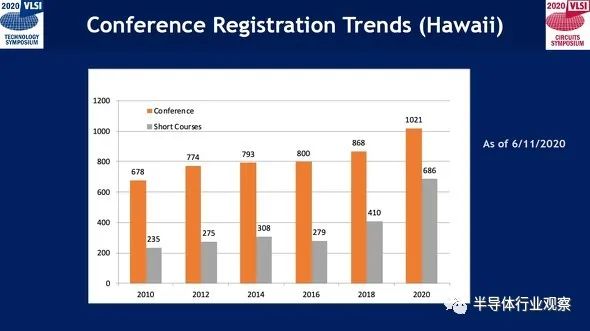

原本计划在夏威夷举行的第四十届“VLSI座谈会2020”于6月15日-18日,在线以点播(On-demand)和线上实时(Live)的形式得以召开。(如图1,2,3,4)。

由于此次座谈会参加者人数众多、内容丰富,笔者仅就细微化、EUV(极紫外光刻)、3D IC展开论述。

今年(2020年)TSMC开始量产采用了5纳米节点(Node,以下简称为“5纳米”)工艺的逻辑半导体,其中,不仅将EUV曝光设备应用于孔上,还应用在了配线上。此外,TSMC计划自10月份开始进行3纳米的风险生产(Risk Production)、明年(2021年)开始量产。另外,已经开始正式研发2纳米,目标是在2022年实现量产。

考虑到TSMC处于细微化加工的最尖端位置,因此当看到VLSI座谈会的发表内容中出现7纳米、5纳米、3纳米这些字眼,笔者并不感到吃惊。此外,笔者更关注的是“2纳米以后将会如何发展”。

其中,比利时imec的Myung Hee Na先生在其“Friday Forum”中,展示了截止到1纳米的技术蓝图(Road Map)(如下图5)。下面中的纵轴为以对数形式表示的每个晶体管的成本、横轴为其技术节点的量产开始年份,横轴上的时间几乎与TSMC的量产计划一致。

图5:1纳米之前的技术蓝图。(图片出自:Myung Hee Na, imec, “CMOS and Beyond CMOS Technologies for Edge Intelligence”, VLSI 2020, FF5)

从以上技术蓝图来看,28纳米使用了High-K/Metal Gate,16纳米---14纳米导入了FinFET,7纳米---5纳米采用了EUV曝光设备,此外,还将Co应用于Middle of Line(MOL)上。MOL是一种将晶体管(FOEL)与多层配线(BEOL)连接在一起的孔(Via),虽然imec使用了Co,还有其他选择项如Mo、Ru等。

此外,4纳米---3纳米中采用了具有Nanosheet结构的晶体管。此次的VLSI座谈会上,有关7纳米、5纳米、3纳米的文章发布得比较多,然而,笔者却发现将Gate All Around(GAA)的Nanosheet结构应用在这些节点上的情况是全球共通的认知。

同时从技术蓝图看,在2纳米中,使用搭载了Buried Power Rail(BPR,在晶体管下埋入电源线的构造)的Forksheet晶体管;在1纳米中,将会使用采用了BPR的Complementary FET(CFET)。

在2019年的VLSI座谈会上,imec表示将会把CFET应用到5纳米、3纳米、2纳米上,笔者就此向其中一位演讲者提出:“imec计划从哪个技术节点开始使用CFET”?得到了以下回答:“就此,目前imec还没有达成一致意见”。

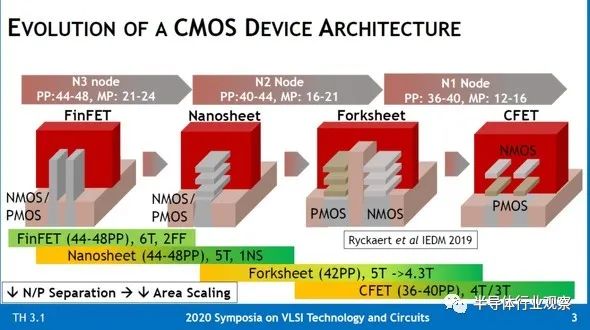

后来,imec在其内部达成了以下共识:3纳米之前采用Nanosheet、2纳米采用Forksheet、1纳米采用CFET。也就是说,在此次VLSI座谈会上,imec的其他发言人,如Sujith Subramanian先生,也是基于以上技术蓝图而做的发表。(如图6)

图6:CMOS结构的变化,FinFET→NanoSheet→ForkSheet→CFET。(图片出自:Sujith Subramanian, imec, “First Monolithic Integration of 3D Complementary FET (CFET) on 300mm Wafers”, VLSI 2020, TH3.1)

从上图可以清晰地看出FinFET、Nanosheet、Forksheet、CFET的结构变化。从FinFET到CFET,通过将Contact Poly Pitch(PP)做到最小、分离nMOS和pMOS,以达到缩小SRAM面积的效果。

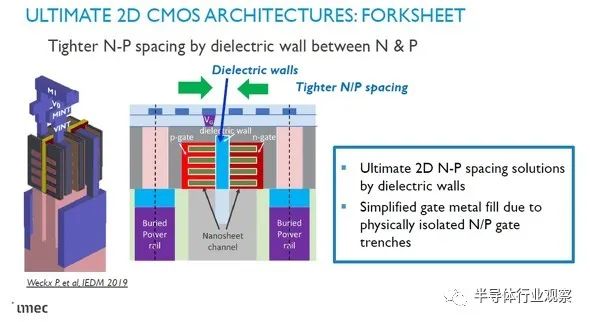

在历年的VLSI座谈会上从未出现过Forksheet这中晶体管结构,今年是第一次,首先做成Nanosheet、然后用绝缘壁膜将其内部分离,就能将nMOS和pMOS分离(如下图7),与其说将nMOS和pMOS的Nanosheet分离有意义,不如说工艺的削减更有意义。

图7:设想的2纳米节点的Forksheet。(图片出自:Myung Hee Na, imec, “CMOS and Beyond CMOS Technologies for Edge Intelligence”, VLSI 2020, FF5)

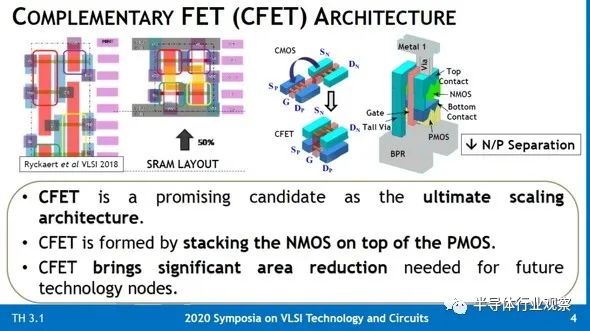

此外,在1纳米中,采用了将nMOS和pMOS纵向排列的CFET(如下图8),虽然CFET的工艺流程非常复杂,但毫无疑问,极大地缩小了CMOS、SRAM的面积,达到了集成化。问题是---是否做到了人们所期待的晶体管的特性,这是未来研发的关键。

图8:设想的1纳米节点的COMPLEMENTARY FET(CFET) 。(图片出自:Sujith Subramanian, imec, “First Monolithic Integration of 3D Complementary FET (CFET) on 300mm Wafers”, VLSI 2020, TH3.1)

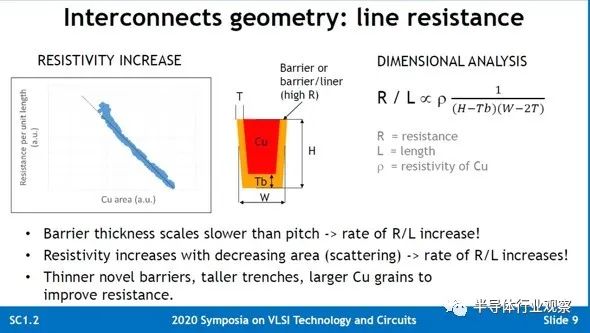

随着细微化的发展,人们也在考虑新的晶体管结构。然而,多层排线却面临着严重的问题,当下,多层排线的材料多采用Cu,由于Cu会扩散到绝缘膜中,因此需要采用Ta、TaN等位障金属(Barrier Metal),含有位障金属的Cu排线的阻值随着细微化的发展也迅速扩大。(如下图9)

图9:排线断面面积的缩小、排线电阻值的增加。(图片出自:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2)

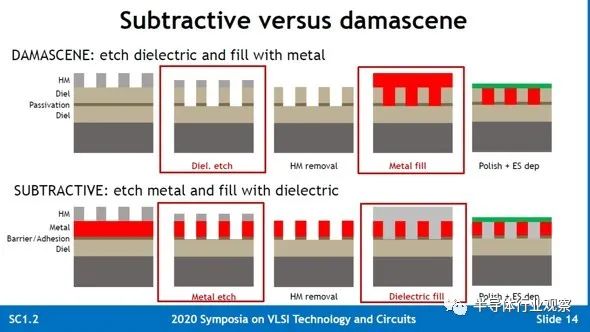

要解决此问题,英特尔的Mauro Kobrinsky先生提出了以下方案:就最细微的配线(M1)而言,不采用传统的Damascene工艺法,而是采用Subtractive工艺法,即直接在金属上进行干蚀(Dry Etching)。(如下图10)

图10:金属排线的形成方法,Damascene工艺法与直接加工法。(图片出自:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2)

实际上,金属直接加工法是在用Cu之前的AI排线法。虽然Cu比AI的阻值低,但是Cu很难被直接加工。于是,在绝缘膜上挖槽、开孔,通过位障金属(Barrier Metal),将Cu埋入,且将不需要的部分利用CMP清除掉,即所谓的Damascene工艺法。

然而,如上文所述,如果排线极细,位障金属(Barrier Metal)的阻值就会成为问题,因此人们不得不考虑不采用位障金属(Barrier Metal)的“金属直接加工法”。

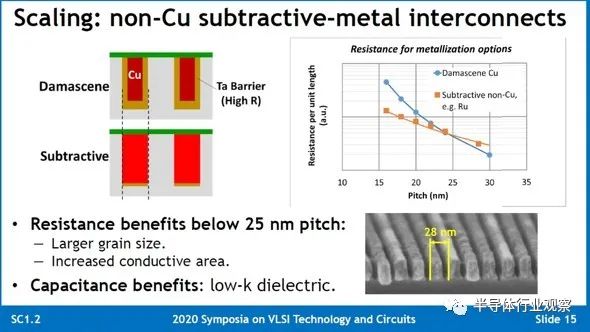

关键问题是到底选择哪种金属材料呢?英特尔的事例如下:直接加工Ru,并形成28nm间距(Pitch)的金属排线。此处排线的阻值比24纳米间距下(同样采用Damascene工艺法)的Cu排线要低。(如下图11)

图11:利用Damascene工艺法做成的Cu排线与利用直接加工法做成的非Cu(比方说Ru)排线。(图片出自:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2)

然而,从笔者过去的经验来看,不推荐使用Ru排线材料,1998年前后笔者曾就职于日立制作所的产品研发中心,从事有关1G Bit DRAM的研发工作。曾预想,在电容(Capacitor)绝缘膜上采用(Ba,Sr)TiO

2

、在电容(Capacitor)电极上采用Ru,当时笔者的工作是Ru柱(Pillar)的垂直蚀刻。笔者当时与LamResearch合作研发了Ru专用的蚀刻设备,采用O

2

与Cl

2

混合离子(Plasma),实现了Ru的垂直加工。

Ru的垂直加蚀刻本身并不是那么困难,但是控制Ru的活动是十分困难的。一旦周边有氧,就会产生RuO

2

。RuO

2

也具有导电性,在电气性能上没有问题,但由于吸取了两个氧,因此Ru就会产生膨胀。

由于当时我们认为直接加工RuO

2

就可以了,因此就马上实行了。然而,RuO

2

又会在还原条件下释放氧气,结果,RuO

2

就变成了满是“洞穴”的Ru。

总之,Ru这种材料会随着周围的环境变化而“呼吸”,这种金属材料无法用于DRAM,因为我们的团队放弃将Ru用于电容(Capacitor)电极上。因此,笔者不认为Ru是一款良好的材料。

如今,英特尔的10纳米工艺进行的似乎也不是那么顺利,笔者认为其最大的原因在于金属排线问题。英特尔首先利用Damascene工艺法在M1上制作Co排线,然而失败了,原因是Co的CMP不充分,导致无法彻底排除缺陷(外界推测)。后来,英特尔又讨论采用Ru排线,如果以上推测属实,那么英特尔的10纳米之路走得真艰辛。

Synopsys的Victor Moroz先生也就在1纳米时代的金属排线(直接加工Mo)进行了演讲(如下图12)。笔者个人认为,就M1的金属材料而言,Mo比Ru更好。

图12:1纳米节点的金属排线。(图片出自:Victor Moroz, Synopsys, “Can We Ever Get to a 100nm Tall Library? Power Rail Design for 1nm Technology Node”, VLSI 2020, JFS3.2)

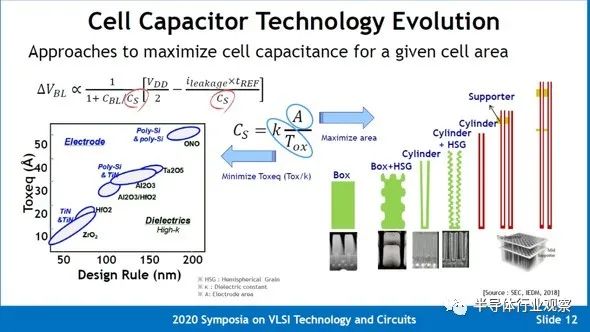

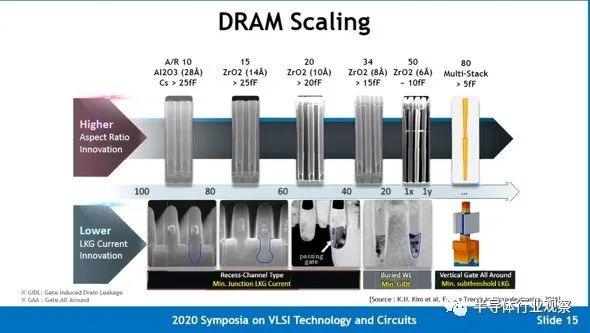

就DRAM的研发而言,最辛苦工作的应该是电容(Capacitor),未来应该也是。三星电子的Gwan-Hyeob Koh先生就电容(Capacitor)的历史在下图13中表示出来。随着DRAM的细微化发展,电容(Capacitor)中存储的电荷量需要保持在一定的值。因此,需要同时在提高电容(Capacitor)绝缘膜的介电率和确保电容(Capacitor)面积上同时下功夫。

图13:DRAM电容的发展。(图片出自:Gwan-Hyeob Koh, Samsung Electronics, “Challenges and Prospects of Memory Scaling”, VLSI 2020, SC1.3)

就电容的绝缘膜而言,有SiO

2

/SiN/SiO

2

(ONO)、Ta

2

O

5

、Al

2

O

3

、Al

2

O

3

/HfO

2

、HfO

2

,最近又出现了ZrO

2

,从图13左上部可以看出。

然而,要扩大电容面积,首先要经过以下流程:在柱状结构的Poly Si电极周围形成电容绝缘膜--Box,将Poly Si表面粗化后形成Ta2O5(Box+HSG,Hemi-spherical grained Poly-Si)-- 圆柱模式(Cylinder Mode),在圆柱(Cylinder)的内外及周边形成HSG。以上流程结束后,再挖深孔,形成具有超高介电率的薄膜。

此处应该关注的点如下:由于圆柱(Cylinder)的纵横比过大,因此容易与旁边的圆柱(Cylinder)连接,导致不良发生,为此,就增加了“桥架”(Support)。最近“桥架”(Support)已经做到两层了。

至此,读者应该大致已经理解了吧。因此,笔者很想知道未来将会怎么再发展下去。其技术蓝图如下图14所示,圆柱(Cylinder)的纵横比的变化为10、15、20、34、50,逐步变大,如今,最尖端的1X、1Y、1Z的纵横比为50。

图14:DRAM的细微化。(图片出自:Gwan-Hyeob Koh, Samsung Electronics, “Challenges and Prospects of Memory Scaling”, VLSI 2020, SC1.3)

此外,未来纵横比应该会增至80,且圆柱(Cylinder)将会通过Multi-Stack来制成。如今,就96层以上的3D NAND闪存(以下简称为:NAND)的存储孔(Memory Hole)而言,除了三星,都采用了Multi-Stack方式。因此,DRAM的圆柱(Cylinder)应该也会采用Multi-Stack方式。

笔者虽然对“DRAM的圆柱(Cylinder)采用Multi-Stack方式”表示吃惊,然而,三星却公布说要用Single-Stack来形成128层的3D NAND。其存储孔(Memory Hole)的纵横比应该是80左右。就同样纵横比(80)的孔的开口而言,DRAM采用Multi-Stack、3D NAND却要采用Single-Stack。三星内部是不是在进行技术方面的争论呢?

TSMC自7纳米的量产以来就开始将EUV应用于孔上,今年(2020年)将EUV应用在排线上,且开始量产5纳米。因此,对尖端细微加工而言,EUV已经不可或缺。

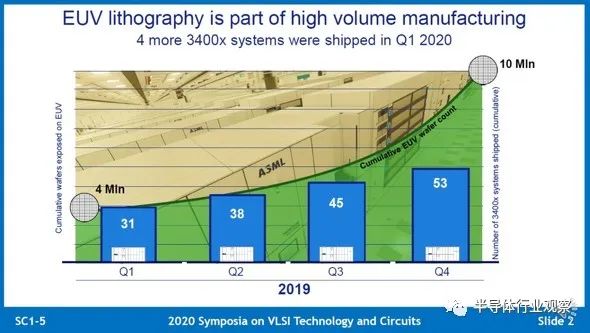

如今能够生产EUV设备的仅有荷兰的ASML一家公司,其出货情况如下图15所示,2019年第一季度,合计出货了31台EUV 扫描设备(Scanner,NXE:3400系列),2019年第四季度出货数量为53台。虽然上面写着2020年出货增加4台,然而这一年总的设备出货数量只有26台。

图15:ASML的EUV爆光设备合计出货数量。(图片出自:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5)

据说,ASML的EUV生产产能为26台/年,且目前ASML处于100%稼动状态,此外,虽然一年出货26台,其中20台被TSMC购买。据说,TSMC未来继续以20台/年的速度导入EUV。

声称要紧追TSMC的三星应该也会以同样的速度购买EUV设备。自研发以来已经经历了20多年的时间,EUV终于迎来了属于它的时代。

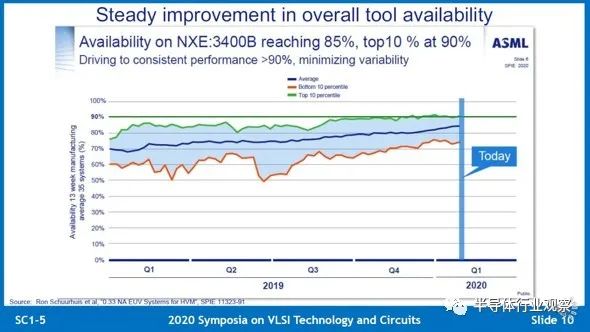

由于TSMC将EUV导入到量产工程中,也促进了EUV性能的提高,下图16为“NXE:3400B”的稼动率,2019年第一季度的平均稼动率为70%左右,2020年第一季度提高了10%左右,提高至85%。

图16:ASML的EUV 曝光设备(NXE:3400B)。(图片出自:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5)

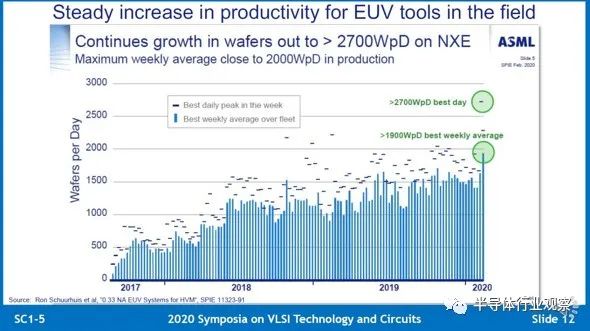

随着稼动率的提高,吐出量(Through-put)也在上升,如下图17,2019年下半年以来,一台设备一天大约可以处理1,500片产品。每小时的生产效率约为62片。此外,2020年第一季度的最高值为一台设备一天可以处理2,700多片产品。每小时的产量提高至112片。

图17:ASML的EUV曝光设备(NXE:3400B)。(图片出自:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5)

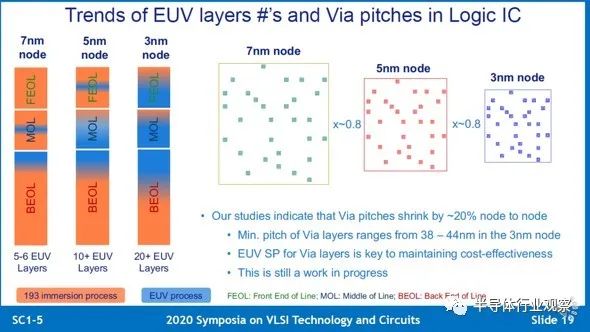

据ASML表示,就采用了EUV的工程而言,7纳米为5---6层,5纳米为10层以上,3纳米为20层以上,如下图18。如今,在TSMC,7纳米(将EUV应用到孔上)的月产晶元数为170k(k=千个),排线上也采用EUV工艺的5纳米月产能为130k,几乎处于100%稼动状态。

图18:7纳米、5纳米、3纳米逻辑半导体分别使用几层EUV?(图片出自:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5)

假设TSMC在用的EUV设备有20台,我们计算一下每台设备的吐出量:

-

假设7纳米的EUV工程为5层,EUV处理产品数量为170k*5=850k。

-

假设5纳米的EUV工程为10层,EUV处理产品数量为130k*10=1,300k。

-

每月的EUV处理产品数量为850K+1,300K=2,150K。

-

每小时的吐出量为:2,150K÷20台÷30日÷24小时×稼动率85%=127个。

上图16中提到,ASML的最大吐出量为2,700个/每日,112个产品/小时,假设TSMC的20台EUV的稼动率为85%,每小时的吐出量为127个,二者数值几乎差不多。几乎可以推测出来TSMC的EUV稼动情况。

曝光设备的解析度可以用以下Rayleigh公式来表示。

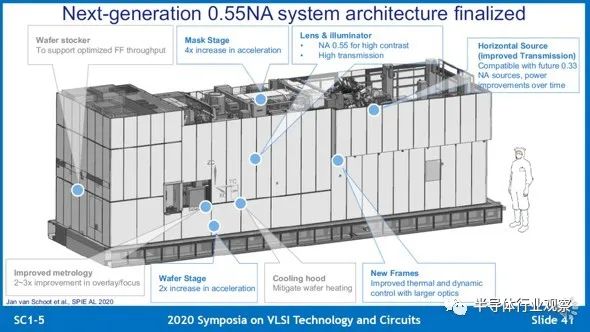

Λ为光的波长、NA是镜片的开口数。对当前使用中的EUV而言,λ=13.5纳米,NA=0.33。而就新一代的EUV曝光设备而言,λ依旧是13.5纳米,镜片的开口数扩大至0.55。那么,解析度R会提高。

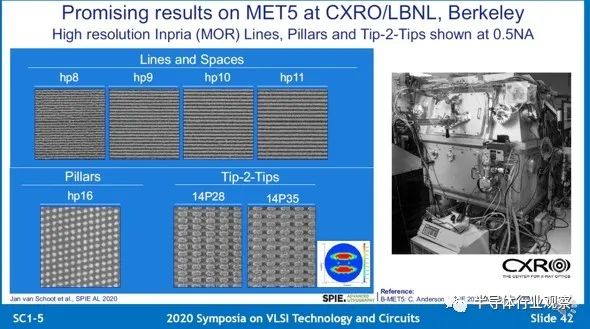

NA=0.55的EUV曝光设备如下图19所示,由于NA的扩大,可以形成更细微的图案。如图20所示,是利用位于Berkeley的The Center for X-ray Optics(CXRO)的NA=0.5的EUV曝光设备,且利用美国Inpria的无机光刻胶做的图案。就Line&Space而言,Half-ptch(hp)下8nm可以成像。此外,还能做成更细微的Pillar和Tip Pattern。如果使用NA值较大的EUV曝光设备,那么就能形成更细微的图案。NA=0.55的EUV曝光设备的发售预计在2021年以后。

图19:新一代EUV曝光设备(NA从0.33到0.55。)(图片出自:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5)

图20:利用NA=0.55的EUV曝光设备,且使用无机光刻胶时的解析度。(图片出自:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5)

虽然细微化的发展速度有所放缓,但还是在进步,此次VLSI的座谈会上还展示了2纳米---1纳米晶体管的结构。此外,由于细微化加工的进步,使EUV曝光设备得以应用于量产工艺,同时使ASML以100%稼动率生产设备。

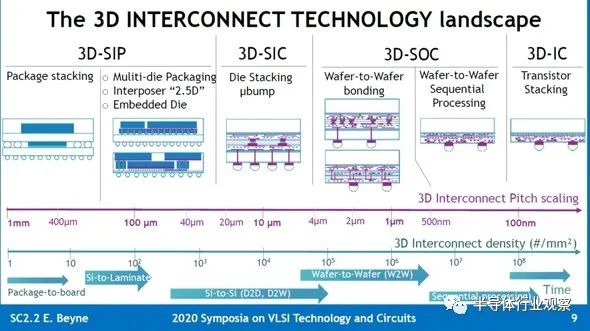

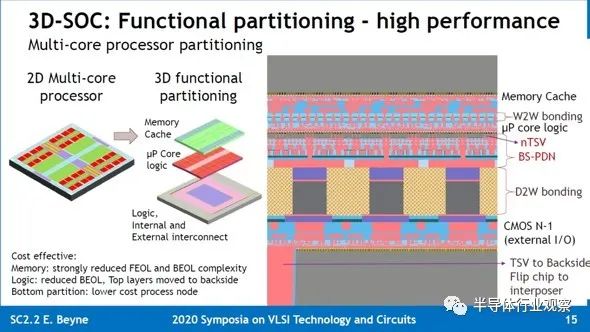

但是,由于尖端系统、电子设备的要求越来越严格,不仅要推进细微化加工(More Morre),还要求更高层次的晶体管的集成(More than Morre)。而且,为了实现More than Morre,堆叠了各种半导体芯片的3D IC技术正在突飞猛进。(图21)

图21:3D 芯片堆叠技术的发展。(图片出自:Eric Beyne, imec, “Heterogeneous System Partitioning and the 3D Interconnect Technology Landscape”, VLSI 2020, SC2.2)

继SiP(System in Package,堆叠Package,通过Interposer排列芯片)之后,通过Micro Bump堆叠芯片的3D SIC开始登场了,并获得了将埋入芯片的晶圆、直接焊接(Bonding)晶圆的3D SOC。此外,也正在研发堆叠(Stack)晶体管的3D IC。

比方说,如图22所示,作为3D SOC,由缓存内存(Cache Memory)和核心(Core)构成的逻辑半导体由Micro TSV(Through-Silicon Via)连接,而且,通过焊接(Bonding)将不同的逻辑半导体连接。

图22:3D IC的结构。(图片出自:Eric Beyne, imec, “Heterogeneous System Partitioning and the 3D Interconnect Technology Landscape”, VLSI 2020, SC2.2)

如果将以上汇集在一颗芯片上,需要准备一个包含了逻辑半导体和存储半导体的Mask Set,而且需要构筑一个极其长的工业流程(Process Flow)。另一方面,如果可以堆叠(Stack)特殊的半导体,就可以分别特化并生产逻辑半导体和存储半导体,并将良品结合在一起即可。设计3D SOC时,需要追求整体的优化(Design Technology Co-Optimization、DECO),毫无疑问,在工艺成本、TAT(Turn Around Time)方面,3D SOC更具优势。

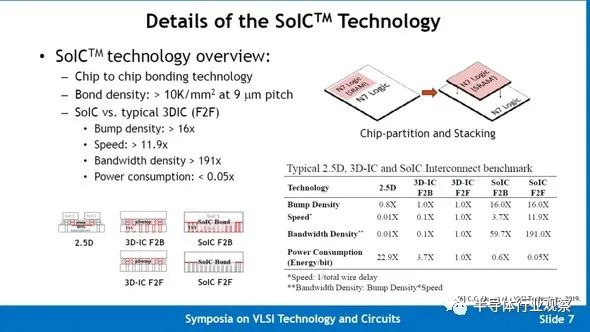

TSMC研发的3D IC技术,即Immersion in Memory Compute(ImMC,简称为:“SoICTM”)技术在成本、性能上都具有极高的优势。

与一般的存储半导体和逻辑半导体的3D IC(F2F:Face to Face)不同,就最好的3D IC的“SoIC(F2F)”而言,Bump密度是一般的16倍,速度为11.9倍,带宽密度(Band Width Density)为191倍,每比特消耗的电力为0.05倍。(如图23)

图23:TSMC的So ICTM的效果。(图片出自:C.T. Wang, TSMC, “Immersion in Memory Compute (ImMC) Technology”, VLSI 2020, TH1.5)

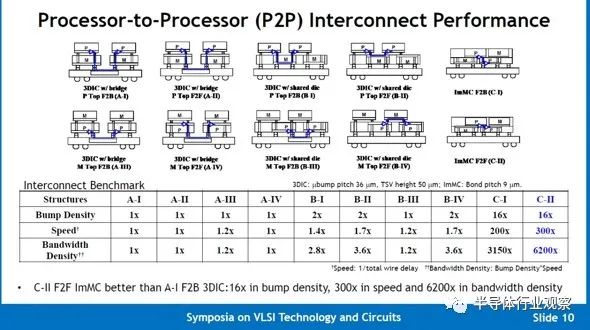

另外,以三维的形式将2个处理器结合在一起,且以三维的形式将2个存储半导体结合在一起的话,哪种压层方式最好呢(如图24)?如果要追求最优性能的话,应该将电子的移动距离设计到最小,这种考虑了系统最优化的设计被成称为System Technology Co-Optimization(STCO)。

图24:处理器和处理器连接后的性能表。(图片出自:C.T. Wang, TSMC, “Immersion in Memory Compute (ImMC) Technology”, VLSI 2

020, TH1.5)

以A-I结构为基准,采用电子移动距离最小的C-II构造的话,Bump密度变为16倍,速度增至300倍,带宽密度(Band Width Density)为6,200倍(与一般的存储半导体和逻辑半导体的3D IC相比)。

综上所述,在2纳米---1纳米之前,细微化还会持续下去,明年也许会出现Sub纳米。要做成2纳米---1纳米的晶体管,System Technology Co-Optimization(STCO)的理念是必须的。总之,“单纯只设计逻辑半导体的时代”已经过去,从所需要的系统中分离(Break Down)出来并设计逻辑半导体才是当下的趋势。

此外,5纳米以后,EUV曝光设备成为不可或缺的要素,其性能也在不断提高。目前正在以TSMC和三星电子为中心,推动EUV的发展和普及。

同时,与细微化的进步同时进行的还有三维形式堆叠芯片的3D IC技术的发展。通过3D IC技术,不仅可以降低成本、提高逻辑半导体的工作速度、削减功耗,而且性能也可以得到大幅度提高。

半导体的发展还在继续。明年的VLSI会在日本京都召开。同时笔者希望新冠肺炎尽快得到控制,明年的VLSI能在线下、线上同时举行。

生于1961年,出生于日本静冈县。毕业于京都大学研究生院(硕士课程为原子核工学专业),后就职于日立制作所。此后16年中,先后在中央研究所、半导体事业部、设备研发中心、尔必达(因工作调动)、半导体前沿技术公司研发协会(即Selete,因工作调动)从事精密加工技术研发工作。2000年,被京都大学授予工学博士学位。目前,担任半导体产业和电力机械产业顾问及撰稿人,细微加工研究所所长。著有《日本“半导体”的战败》《“电器、半导体”产业大崩溃的教训》、《日本型制造业的败北,零战·半导体·电视机》。

★

点击文末【阅读原文】,可查看

本文原链接

。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2369期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

英伟达|中芯国际|CPU|晶圆|

FPGA

|

5G|谷歌|射频

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie