[原创] 英特尔推出全新晶体管,吹响反攻号角!

2020-08-14

14:00:19

来源: 半导体行业观察

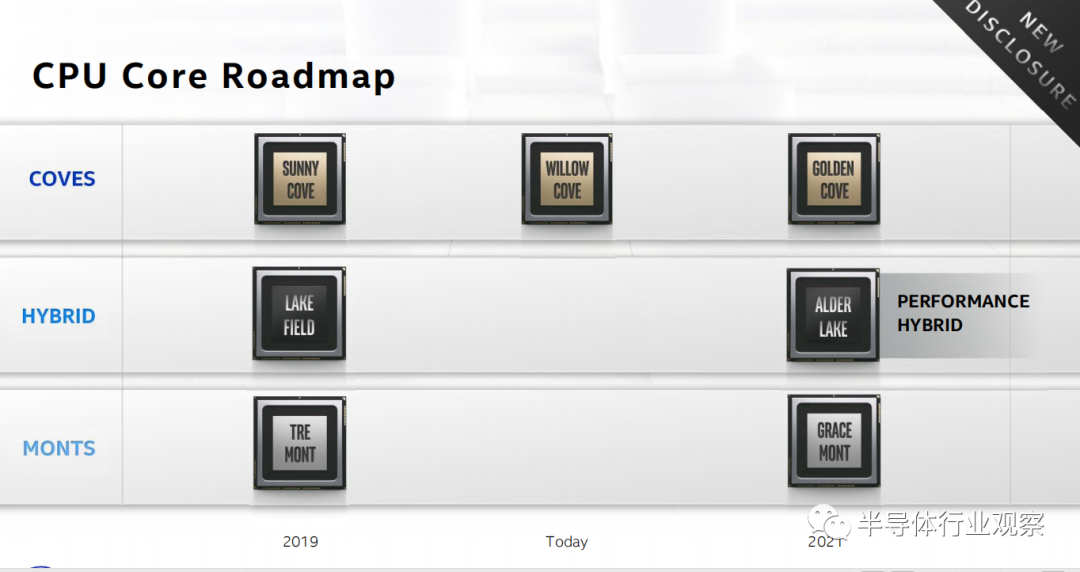

昨日晚间,英特尔在其2020年架构日中更新了他们在六大技术支柱方面所取得的进展,揭秘了Willow Cove,Tiger Lake和Xe架构以及全新的晶体管技术。这为我们展现了一个不服输,甚至还在挑战新领域的英特尔。

英特尔本次发布的全新晶体管技术是这次架构日中的亮点之一。

一直以来,英特尔在晶体管技术的发展中扮演着重要的角色。大约十年以前,晶体管结构开始从平面结构转向FinFET。在这个转变过程当中,英特尔是第一个将FinFET实现商业化的企业——2011年,英特尔将之用于22nm工艺的生产。两年后,其他企业才跟进有关FinFET的生产。从16/14nm开始,FinFET成为了半导体器件的主流选择。时至今日,FinFET仍旧是现代纳米电子半导体器件制造的基础,支持着7nm,甚至是未来5nm、3nm的发展。

但在先进工艺不断向前发展的过程当中,FinFET技术也需要不断地进行更新,才能满足晶体管性能上的提升。因此,在英特尔从14nm走向10nm的过程中,他再次重新定义了晶体管。

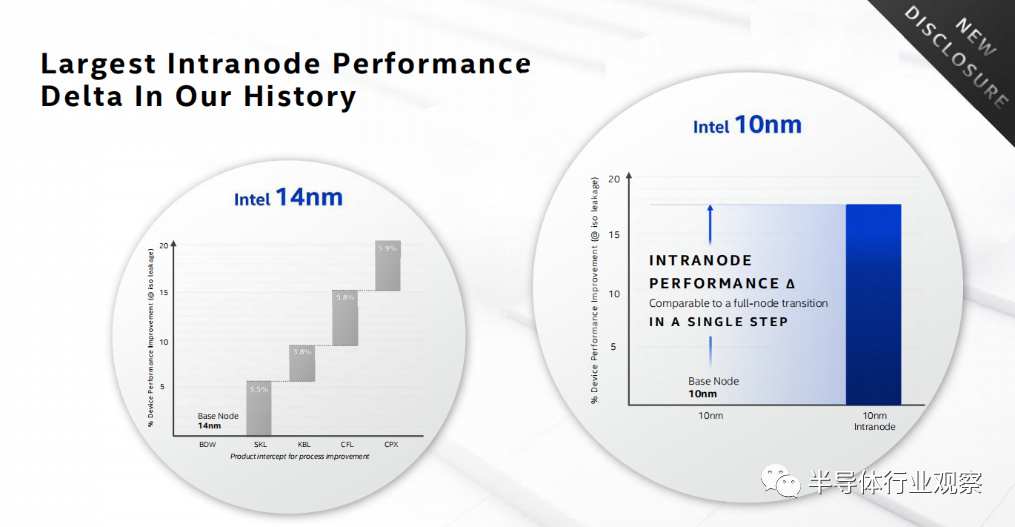

在本次架构日当中,英特尔推出了10nm SuperFin技术。英特尔称,这是该公司有史以来最为强大的单节点内性能增强,带来的性能提升可与全节点转换相媲美。换言之,在SuperFin技术的加持下,英特尔推出的10nm工艺效能可以等同于7nm。

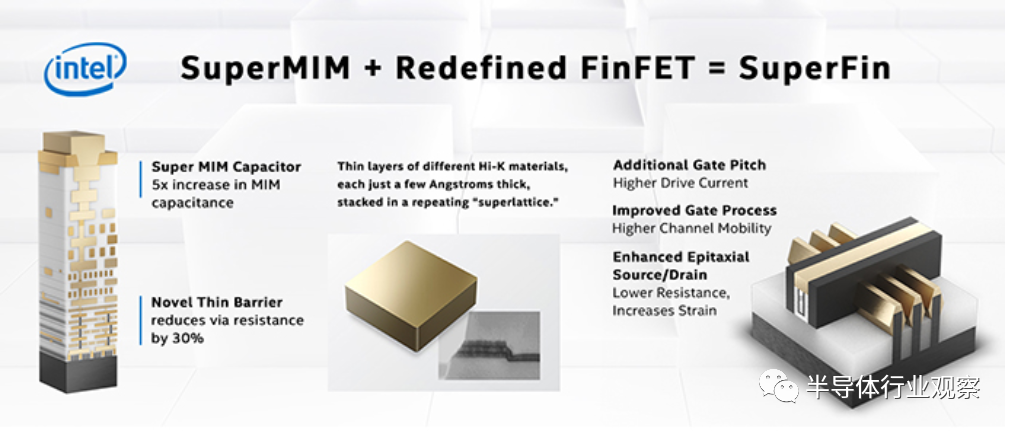

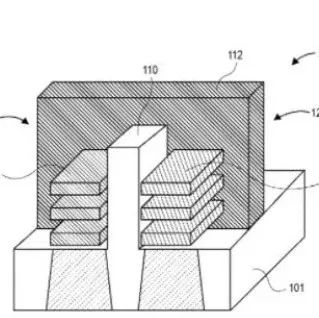

从英特尔公布的信息中看,10nm SuperFin技术还实现了英特尔增强型FinFET晶体管与Super MIM(Metal-Insulator-Metal)电容器的结合。据其官方资料显示,Super MIM在同等的占位面积内电容增加了5倍,从而减少了电压下降,显著提高了产品性能。英特尔成,该技术由一类新型的“高K”( Hi-K)电介质材料实现,该材料可以堆叠在厚度仅为几埃厚的超薄层中,从而形成重复的“超晶格”结构。这是一项行业内领先的技术,领先于其他芯片制造商的现有能力。

为什么说SuperFin技术重新定义了晶体管。这就要从单节点内性能提升幅度的角度看。从英特尔提供的数据来看,如今加强版14nm在性能上相比第一代已经提升了超过20%,而这种提升幅度是经过了四次修订才达到的。但有了SuperFin技术,英特尔的10nm做到这种提升却只花了一代。因而,可以说这是相当于一代制造工艺的飞跃。

从英特尔的介绍中看,SuperFin技术无疑是推动其先进制程快速向前发展的利器。在笔者看来,这也是英特尔对市场质疑其先进工艺落后的回击(前不久英特尔公布了其第二季度财报,当时英特尔称其7nm芯片考虑由其他企业代工,引起了市场质疑其先进工艺的水平)。

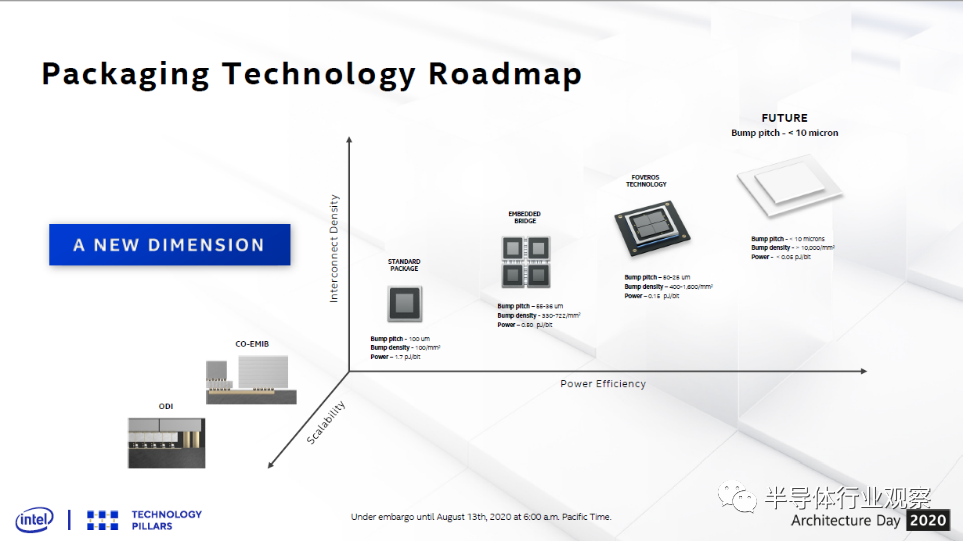

众所周知,先进工艺的进步需要相关企业对此进行的投入越来越大,但在大规模投资下所诞生的制程微缩所带来的单位成本降低的效益却明显下降,在这种环境下,先进封装成为了各大厂商竞逐的新领域。

近几年,异构架构的出现推动了先进封装的发展。在此期间,英特尔发布了2.5D封装 EMIB、3D封装Foveros以及被视为是两者结合的Co-EMIB。

在本次架构日当中,英特尔介绍了继Foveros后又一新的先进封装技术。英特尔称其为“混合结合(Hybrid bonding)”技术。英特尔的官方资料显示,当今大多数封装技术中使用的是传统的“热压结合(thermocompression bonding)”技术,混合结合是这一技术的替代品。这项新技术能够加速实现10微米及以下的凸点间距,提供更高的互连密度、带宽和更低的功率。

据透露,使用“混合结合(Hybrid bonding)”技术的测试芯片已在2020年第二季度流片。

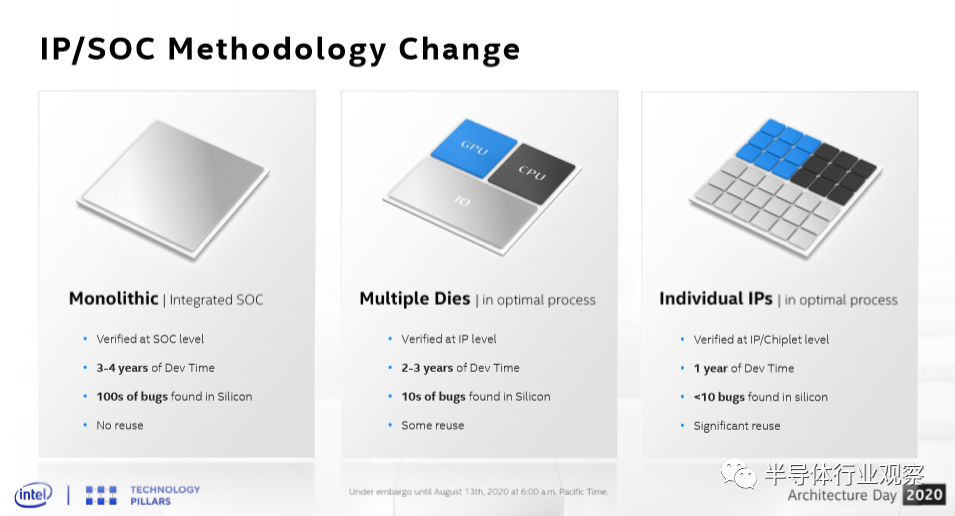

这些先进封装到底能解决什么样的问题?从市场情况中看,异构已经成为了未来芯片发展的一种趋势,越来越多的硬件将会集成到一块芯片当中,未来这种趋势还将发展成将更多的IP集成到一块芯片当中。英特尔将这种设计定义为“分解设计”。

如下图所示,利用这种分解设计可以大幅缩短整个开发时间。众所周知,采用新的工艺就意味着相关器件要重新进行验证,但随着终端领域所需要的功能越来越大,越来越多的器件都将加入其中,这就导致开发或者是验证的时间越来越长。

而采用这种分解设计则可以化繁为简,先把它做成几个大的部分,比如可以分为CPU、GPU、IO等(这些硬件可以采用不同的工艺),再分别进行更新或验证。举例来说,CPU可能是一个已经验证过的,在这种分解设计下,CPU就不再需要重新验证。而GPU则是要用更新的,但由于它与CPU是分离的,所以仅需要对GPU进行重新验证。这也就是说,不会因为CPU和GPU互相纠缠在一起,而出现新的Bug出现,这也就大大缩短了产品验证的时间。

要达到这种设计效果,其中的互联就变得尤为重要,而这就是先进封装所能解决的问题。EMIB、Foveros或是Co-EMIB能够保障这些硬件能够分解,又能保证它们在低功耗下拥有足够的数据传输带宽。也正是利用这些技术,英特尔才能够将来自其他供应商的IP和处理节点混合并匹配到异构封装中,从而加快产品上市时间。

而英特尔的技术价值将在Tiger Lake中得以体现。据透露,Tiger Lake将由英特尔全新的Willow Cove架构提供动力,该架构也是基于新的“ SuperFin”晶体管打造而成。

英特尔指出,Tiger Lake将在关键计算矢量方面提供智能性能和突破性进展。同时他也是英特尔第一个采用全新 Xe-LP微架构的SoC架构,可以对CPU、AI加速器进行优化,使CPU性能得到超越一代的提升,并实现大规模的AI性能提升、图形性能巨大飞跃,以及整个SoC 中一整套顶级IP,如全新集成的Thunderbolt 4。

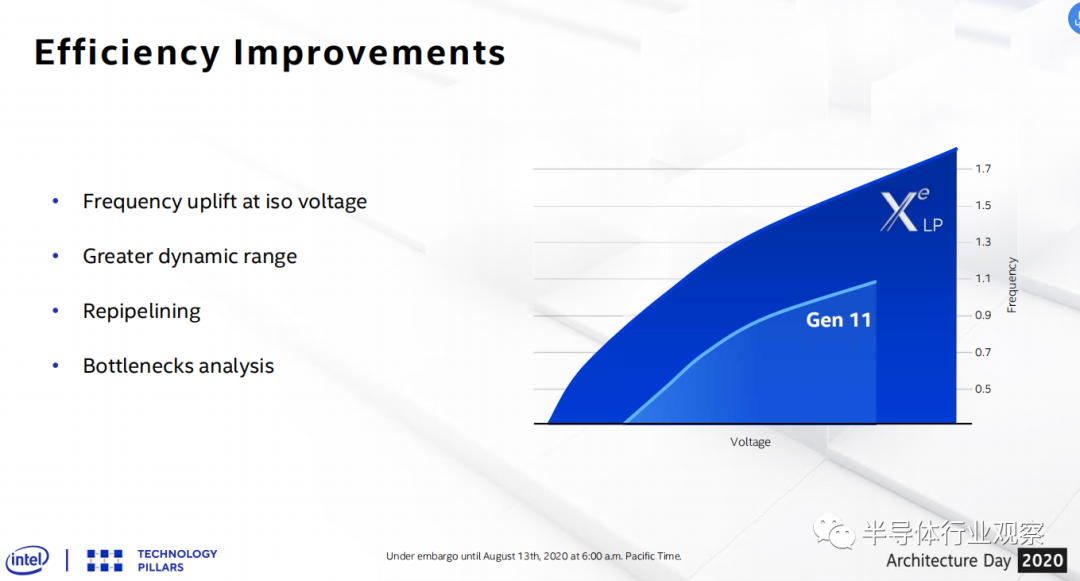

Tiger Lake中所采用的Xe-LP是Intel面向PC和移动计算平台的最高效架构,拥有多达96个EU,并采用了包括异步计算在内的新架构设计,以提供更大的动态范围和频率提升。根据英特尔提供的官方数据显示,与Gen11相比,Xe-LP能够在更低的功耗下,提供更高的性能。

当然,Xe-LP只是英特尔发展路线图中的一部分。除此之外,英特尔还提供了Xe-HP的更新版本,据介绍, Xe-HP是业界首个多区块(multi-tiled)、高度可扩展的高性能架构,可提供数据中心级、机架级媒体性能,GPU可扩展性和AI优化。它涵盖了从一个区块(tile)到两个和四个区块的动态范围的计算,其功能类似于多核GPU。据悉,该款GPU有望在2021年发布。

同时,英特尔还发布了另一款GPU架构:Xe-HPG。据介绍,它是专门针对游戏而设计。据英特尔官方消息显示,Xe-HPG添加了基于GDDR6的新内存子系统以提高性价比,且将具有加速的光线跟踪支持。因此,也有外媒猜测,这可能代表着英特尔将首次围绕着游戏所需的GPU,与AMD和Nvidia展开竞争。据透露,Xe-HPG预计将于2021年开始发货。

除了Tiger Lake之外,英特尔还在本次发布会中提到了另外一款产品——Alder Lake。据介绍,该产品是英特尔的下一代采用混合架构的客户端产品。Alder Lake将结合英特尔即将推出的两种架构——Golden Cove和Gracemont,并将进行优化,以提供出色的效能功耗比。

据此前消息显示,集众多新技术于一身的Tiger Lake将于今年当中面市,而这也会是验证英特尔技术的时刻。

其实除了在备受瞩目的架构、先进制程与封装、互联等领域外,英特尔还在安全、软件、存储方面都有了一些新的进展。例如,在软件方面,英特尔oneAPI的正式版本将于今年当中面市。

自从2018年,英特尔提出这六大支柱后,我们就可以看出,英特尔早已不是那个依赖于某一单独领域去领导半导体产业发展的企业了,将多个不同领域的技术组合起来而形成产品的领导力正在英特尔身上凸显出来。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2401期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

美国|蓝牙

|

5G|华为|台积电|FPGA|ARM|晶圆

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie