[原创] 开发者的“新思”偏要猜

2020-09-10

14:00:24

来源: 半导体行业观察

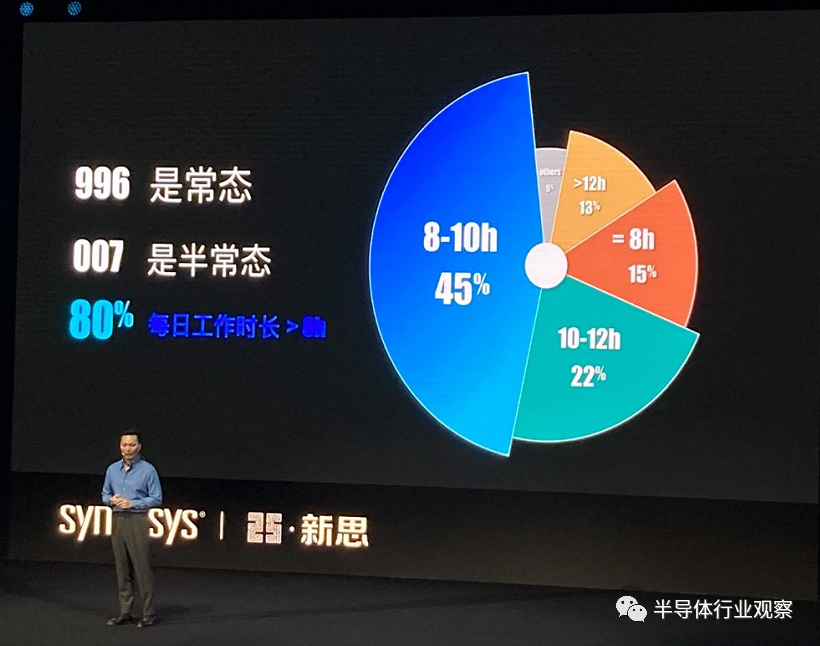

9月8日,一年一度的新思开发者大会在上海举行,本届开发者大会以“芯际探索”为主题,共吸引了超过1000位全球开发者的参与,通过主题峰会和近40场技术论坛与60多位行业顶级专家共同分享前沿科技趋势,交流以芯片赋能科技应用的成功经验。大会期间所播放的随机路人街访,询问对集成电路开发者的看法时,大致可以总结为“闷、聪明、加班、秃头、学历高、格子衫”这几个词。

似乎一一对应着新思科技中国董事长兼全球资深副总裁葛群在演讲中提到的《创芯说开发者调研》的结论,知其然还得知其所以然,剖开表象,真正的开发者到底怀揣着什么心思?

葛群的演讲主题为《与开发者共思同行》,解读了新思科技主导的业界首个“创芯说”开发者调研结果,剖析芯片开发者职场现状与未来发展。

新思科技中国董事长兼全球资深副总裁葛群解读《创芯说开发者调研》

据葛群介绍,这份开发者白皮书的调研囊括北京、上海、江苏等8个一线城市,收到超过2700多份的回复。“一入IC深似海。”葛群这句话揭示了开发者圈子的状态,所谓不疯魔不成活。

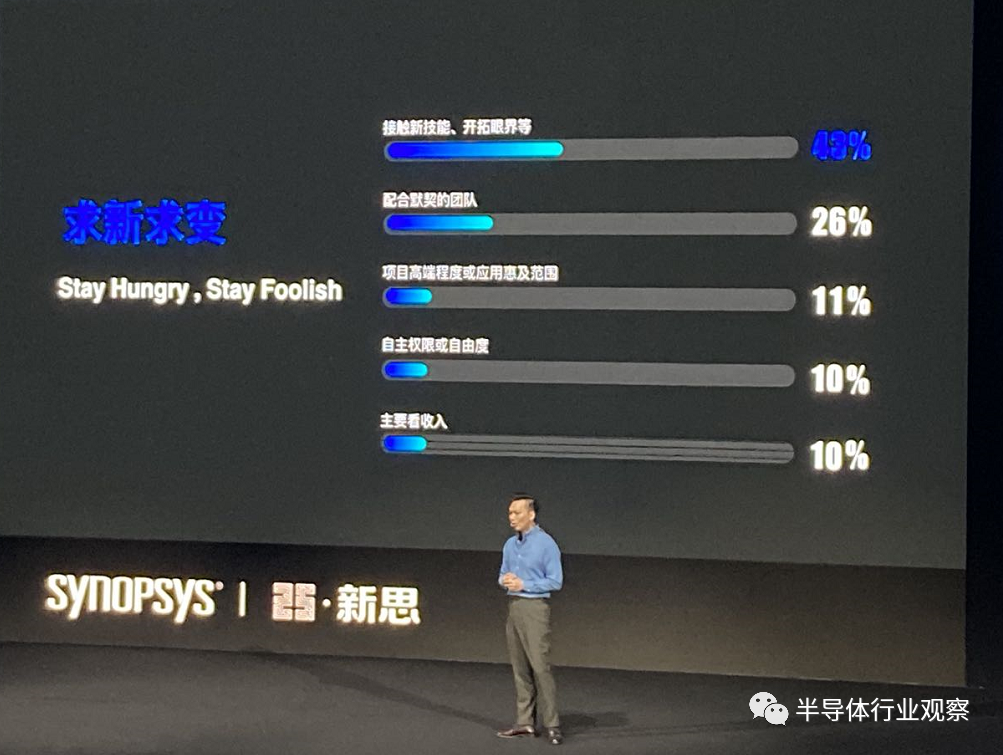

48%的开发者认为,接触新技能、开拓眼界是快乐的。再往下是配合默契的团队、项目高端程度或应用惠及范围,只有10%的人谈到了钱。显然,大部分人选择了月光,六便士踩在脚下。

关于挑战,如下图。38%的人认为产品定义和客户及市场需求把握最难办,19%的人表示确保项目及时完成最难,还有19%的人表示协调合作方确保流片成功难度大。葛群认为:“产品的成功不在于技术的进步,早期的定义和规划更为重要,我们需要让开发者更早的把握市场。”

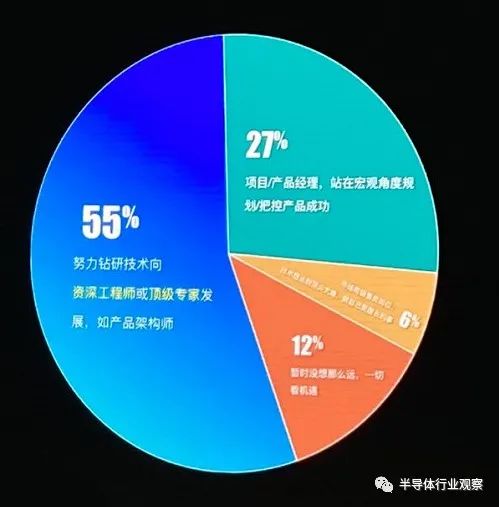

在职业规划方面,如下图。有55%的开发者想继续努力钻研技术向资深工程师或顶级专家发展。27%的开发者希望成为项目/产品经理,站在宏观角度规划/把握产品。

对于开发者来说,使命必达是一种信仰,这种信仰按交付日期、确保一次流片成功、及时需求响应、节省成本进行排序。

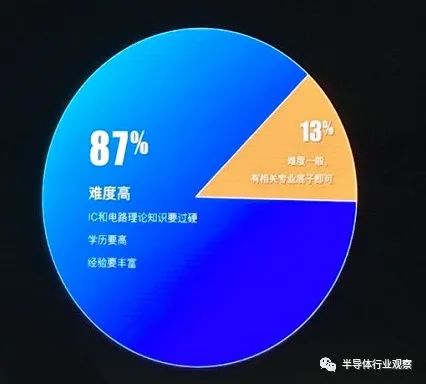

此外,从下图来看,IC开发者对自身的职业焦虑感很重,87%的人认为,该行业技术要求难度非常高,不仅学历要求高,经验也要不断积累。面对产业快速变革,需要保持终身学习的习惯。

关键是当遇到问题时,92%的人会在固有圈子这里寻找建议,如下图,只有8%人会对外寻找建议。

“跨出圈子,拓展思维,与行业伙伴交流,才是开发者们快速升级的秘籍。”葛群表示:“这也是新思举办开发者大会的初衷,创造一个IC开发者的嘉年华,让开发者尽情切磋,寻找志同道合的小伙伴。愿与所有开发者共思同行,探索更多未知边际,带领国内技术研发力量走向更深远未来,以创新改变世界。”此外,葛群近年来也成功推动新思全球人工智能实验室在中国的设立,赋能更多开发者。据资料显示,新思科技人工智能实验室已成功帮助国内第一颗云端级人工智能芯片的发布。通过早期融合,将算法和芯片实现早期优化,缩短了至少1/3的运算时间。

现在看上面这些饼状图,与路人甲乙丙丁所假想出来的形象非常接近,而百分比数字背后藏着的是原因,知其因,才能出对应的策略。那么,除了举办的开发者大会、线上培训等,新思在技术上是怎么做的呢?

有人将EDA工具比作皇冠上的明珠,总感觉不够准确和接地气,毕竟这是开发者们都可以触摸到的东西。芯片/电路像一袭华美的长袍, EDA工具如同快速移动的梭子,在追求速度和质量的同时,织出美丽的长袍。

新思是如何织起华美长袍的,这事还得从新思科技总裁兼联席首席执行官陈志宽博士回顾历史的演讲说起。

陈志宽从微米时代一直聊到纳米时代,在1999年时,复杂性最大的挑战已经不再只是在设计,还有验证方面和IP复用。而新思在1992年就开始IP复用方面的研究。

到了2007年,整个系统的复杂度和规模复杂度需要有很多不同的工具。

2008年,全球遭遇金融风暴,65nm的CPU维持了很长时间,背后可能是经济问题,也可能是技术问题,漏电流难点是当时一个很大的挑战。

到了45nm,High-K栅极电介质出现,我们才有方法来应对漏电流。所以到2011年,有很多32-45nm的设计。

2015年,万物趋向智能、IoT时代,我们需要不同的设计来满足不同的需求。最大的挑战就是验证,如何Shift Left(验证左移)、怎么去比较早一点找到Bug都是难题,不仅在模拟下功夫,更是要在形式化验证、原型仿真、调试上下功夫。

2018年,进入AI时代,验证技术的考验只是一部分,我们要考虑AI跟IP 要怎么去帮忙做AI芯片、解决AI问题。也要处理怎么把AI引入EDA方面的应用。

2019年,中国新思团队把用户大会变成开发者大会,不仅促进开发者之间的交流,也在技术方面探索前端和后端的技术加在一起的方法。

如今2020年,陈志宽表示:“我们要为大家解决设计、验证和IP方面的所有复杂性问题,此外还要在设计工具与软件安全合并下,提供帮助,提升制造技术,从应用层服务开发者。”

说到当下,新思科技首席运营官Sassine Ghazi通过隔空连线介绍了新思为支持开发者创新所推出的多款全新技术——DSO.ai、RTL Architect、3DIC Compiler。

新思科技首席运营官Sassine Ghazi介绍新思科技最新技术

就资料介绍,DSO.ai能够通过AI技术在芯片设计的巨大求解空间里搜索优化目标,大幅提升芯片设计团队整体生产力。据悉,三星芯片设计团队利用这一技术实现的突破,“仅用3天就实现了原本需要一个多月才能完成的芯片设计工作”。RTL Architect则是业界首个物理感知RTL设计系统,可将芯片设计周期减半,并提供卓越的结果质量。此外,3DIC Compiler技术则提供了一个集架构探究、设计、实现和signoff于一体的环境,能够帮助开发者实现多裸晶芯片集成、协同设计和更快的收敛。

关于未来最期待的EDA技术趋势,Sassine表示:“定制设计与仿真、硅生命周期管理(Silicon Lifecycle Management)是我最为期待的两个技术发展方向。新思科技近年来在定制设计与仿真领域投入巨大,之后也即将在一些创新方向上取得突破。而硅生命周期管理则是新思科技所关注的一个全新领域,这一技术将帮助开发者管理从SoC层面、硅片层面到应用层面的整个芯片生命周期。”

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2428期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

IC设计|蓝牙

|

5G|封装|博通|台积电|中芯国际|EDA

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie