[原创] Chiplet究竟能否解决我国卡脖子难题?

2020-10-27

14:00:09

来源: 半导体行业观察

2020年7月8日,具有历史意义的一天,作为AI计算架构的代表英伟达市值达到2480亿美元,超过传统计算架构寡头Intel 2460亿美元市值,而五年前,英伟达的市值仅为Intel的1/10。这预示着新架构和新产业正势不可挡的快速崛起。

作为一种芯片级IP整合重用技术,Chiplet技术近年来受到广泛的关注。与传统的单芯片(Monolithic ASICs)集成方式相比,Chiplet异构集成技术在芯片性能功耗优化、成本以及商业模式多方面具有优势和潜力,为CPU、FPGA以及网络芯片等多领域芯片的研制提供了一种高效能、低成本的实现方式。Chiplet技术涉及的互连、封装以及EDA等关键技术和标准逐渐成为学术界和工业界的研究热点。

10月22日,由中国计算机协会(CCF)主办的计算领域年度盛会中国计算机大会(CNCC)在北京隆重召开,会议针对Chiplet技术特设了主题技术论坛。来自中科院、新思科技、摩尔精英等机构企业的专家学者共同探讨Chiplet技术以及对未来芯片产业的影响。

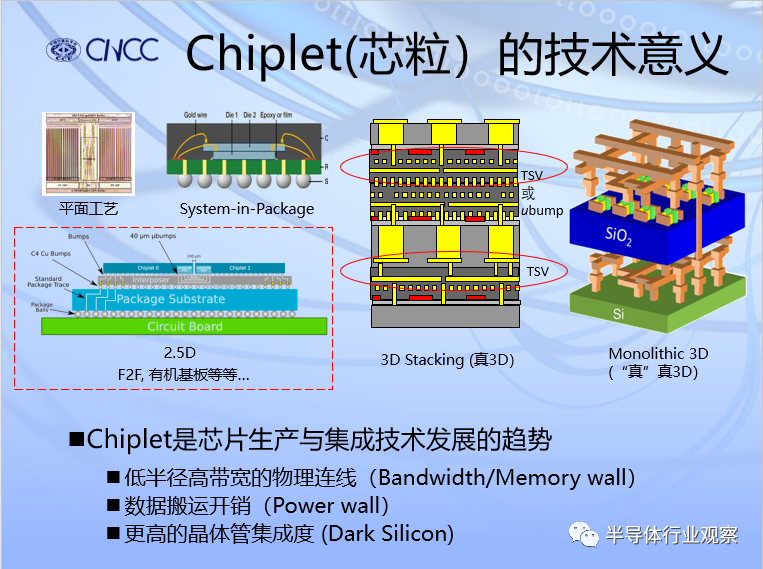

中科院计算所副研究员王颖博士在开场就谈到了Chiplet的意义。他谈到,从技术意义上来看,Chiplet是芯片生产与集成技术发展的趋势,它所依赖的2.5D封装或者3D堆叠技术具有低半径高宽带的物理连接特性,较低的数据搬运开销以及更高的晶体管集成度;从工业意义上来讲:Chiplet同时也是一种新的设计/商业模式,相比复用IP的单片SoC以及真三维芯片,Chiplet具有成本优势;再者

通过复用现有Die,它还具有开发敏捷度优势

;通过集成Known-good Die,能提升大规模芯片良率;另外通过异质集成还能降低对工艺的依赖。

当然Chiplet还面临着诸多挑战,例如在封装技术与生产工艺、EDA工具链、热耗散,时钟与功耗运输网络、片上互联(NoC)或Interposer上互联、Chiplet间接口与协议标准化、Chiplet模块的DFT、验证、可靠性与DFM、新的IP共享与授权模式上、体系结构设计,系统级设计的片间划分等等。因此,Chiplet的发展还需要产业界的共同努力。

中国科学院计算技术研究所研究员韩银和就《机器人专用处理器-多智能处理的异构架构和集成》主题发表了精彩的演讲。他讲到,随着摩尔定律迟缓,需要更多结构创新,图灵奖得主David Patterson的研究也表明芯片体系结构的黄金时代正在来临。而具体到机器人领域上,机器人处理器是一个全新的芯片种类,他需要支持机器人应用所涉及到的主要功能的加速。我们也正在机器人专用处理器领域进行探索,并开发出了多款芯片。

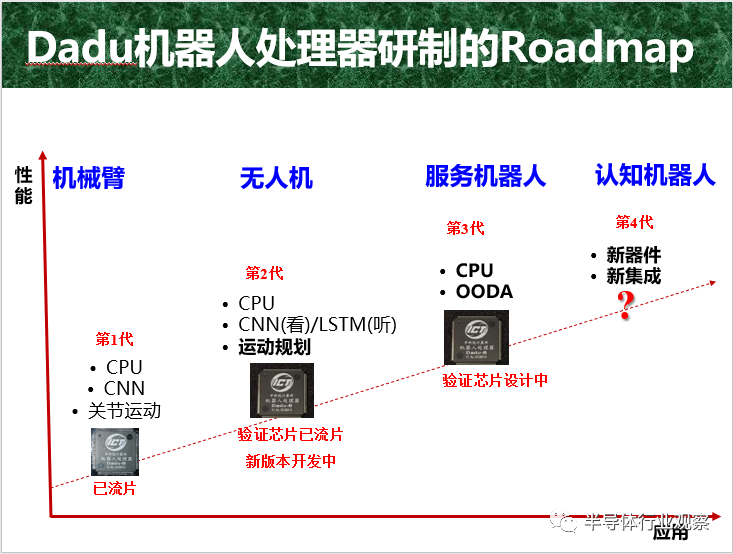

“机器人处理信息的流程,可以抽象为感知-判定-决策-行动四个步骤,我们提出了Dadu、Dadu-P、Dadu-CD等多种异构并行架构,从宏观上的路径规划,以及微观上的关节控制计算两个核心步骤上着手,加速机器人上运行的核心处理步骤。Dadu机器人处理器路线图分为4代,第一代机械臂以CPU、CNN和关节运动为主,目前已流片;第二代主要是无人机,侧重在运动规划,验证芯片已流片,新版本正在开发中;第三代则是服务机器人,采用CPU和OODA,相关的验证芯片正在设计中;第四代将属于认知机器人范畴,或许将采用新器件新集成的方法,我们也正在探索用Chiplet集成的方法,快速扩展芯片功能,降低芯片设计周期和制造成本。”韩银和在会上介绍到。

在韩银和看来,

专用处理器是星星之火,专用处理器种类型多了,也能成燎原之势,弥补我们在通用处理器上的不足。

据Gartner预测,到2023年,计算产业的规模将超过2万亿美元。这2万亿美元不是延用传统架构的计算产业,而是突破能效墙、散热墙、优化墙、内存墙、高速IO墙的基于系统架构、晶圆拼装工艺创新的增量市场。

在立足国情扬长避短,谋求与美国同位乃至错维竞争的问题上,国家数字交换系统工程技术研究中心研究员刘勤让指出,需最大程度的发挥芯片技术在新结构、新计算、新互联以及新集成上的后发优势,同时要充分兼顾国内在加工、封装、测试和工具上的实际水平,以此来探索工艺与体系协同迭代的创新。因此,在深刻剖析集成电路发展困局的基础上,结合软件定义体系结构创新成果,软件定义晶上系统(SDSoW)提出。

刘勤让讲解到,SDSoW从互连密度驱动智能涌现出发,用TCB集成代替PCB集成,实现3个数量级的互连密度提升;联合体系结构的创新,用晶圆级资源倍增软件定义的功能、性能和效能增益,实现1~3个数量级的性能和效能增益。通过软件定义晶上系统的创新,在体积、带宽、延迟、功耗、等方面可以获得4~6个数量级的综合增益,由此带动集成电路从片上系统迈入晶上系统新时代,并全面刷新新型基础设施的技术物理形态。

此外,SDSoW还将催生新经济性的衡量指标和商业模式。

现在靠卖物化的芯片来获得利润,

目前主要以芯片设计/流片的费用对比芯片的预期销售规模作为经济性衡量指标;未来则是

靠卖云化的服务获得利润

,以芯片设计/流片的费用对比芯片的预期服务次数作为经济性衡量指标。服务模式在发生转变,微电子技术经济性的边界也在转变,因此,

我们需要探索出一条以“新赛场、新赛道”实现一流系统的集成电路发展的新道路。

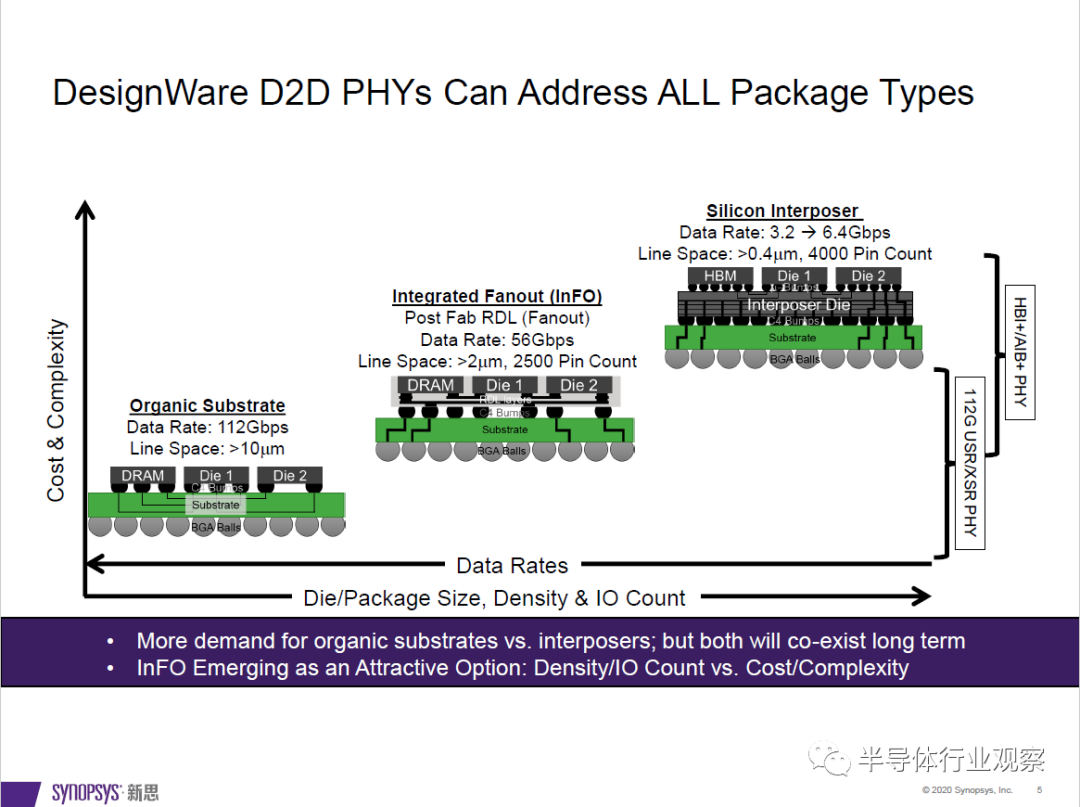

新思科技高级技术经理王迎春的演讲主题为《DesignWare Die-to-Die PHY Solution for Chiplet》。他介绍了Chiplet的典型的应用场景,如Scale SoC, Split SoC和异构计算等,以及与之适配的Synopsys DesignWare PHY IP solution,重点说明了PHY IP的技术指标对这些系统应用的意义。同时,简要介绍了PHY IP的结构,完整的Chiplet设计流程和测试方案。Synopsys有最新的3DIC Compiler,这也是行业内

第一个完整的Chiplet设计平台

,具备360

o

视角的3D视图,支持2.5D/3D封装设计和实现的自动化和可视化,同时面向供电、发热和噪声进行优化。

在摩尔精英董事长兼CEO张竞扬看来,Chiplet无疑是未来芯片行业最重要的趋势之一,这与整个电子和半导体产业的分工协作是一脉相承的。尤其是Foundry和IP授权模式的诞生,承担了产业链一头一尾的工作,大大降低了半导体产业的推入门槛。而随着芯片定制成本攀升和碎片化市场的矛盾不断凸显,芯片行业需要大幅提升芯片研发效率。

回看“摩尔定律”其实暗藏伏线,其中一条路是按照每18个月集成度翻倍发展,另一条没被大家关注的路径是,通过封装的形式将小功能模块合在一起,可能是更经济的方式。

“Chiplet推广困难重重,六大要素互为因果。第一个是市场需求和采购不明确,不明确的原因是Chiplet的分工和互联标准还没有确认,因为没有这些标准就没有稳定多样的Chiplet供给,而对于SiP封装设计和整合方面又面临着软件、模型和平台上的难题,再就是现在还不具备柔性快速生产能力,最后就是品质管控和保险赔付问题比较复杂。”张竞扬指出。

好在中国2000多家芯片公司中,有很多小公司愿意尝试新的服务模式。而摩尔精英也正在探索建立一个SiP的平台,

通过严选的SiP芯片、借力现有的KGD裸片过渡,统一芯片生产和品质控制

,建立一站式Chiplet研发、生产、销售协作平台,从而能让更多的芯片企业享受到SiP设计和柔性生产的服务。

中国科学院微电子研究所研究员王启东针对《Chiplet与异质集成-摩尔定律延续的一些思考》的主题做了报告。王启东讲到,Chiplet与异质集成有本质区别:Chiplet的发起者主要是IDM和Foundry,如AMD和Intel,

Chiplet主要解决Foundry的制造和成本问题,解决IDM的产品差异化问题

,

解决off-the-shelf的多品种小批量问题

。而异质集成的发起者主要是OEM和Packaging house,对于数字、模拟、射频、电源、天线等芯片来说,

小型化、高功能化,一体化将是最终诉求。

Chiplet的技术内涵其实是一个自上而下的革命,通过先进封装技术如2.5D/3D TSV封装、Fanout封装、先进功能性基板等,结合标准的接口、协议形成Chiplet。但如前文所说,Chiplet在设计和制造等方面还面临诸多挑战,据王启东介绍,微电子所的先进封装平台华进半导体是一家以先进封装/系统集成技术研究与开发为主的企业化独立运营的国家级研发平台。目前中科院微电子所拥有Chiplet所需的先进封装技术,覆盖了设计、仿真、制造、测试的链条环节,希望与国内企业、院所一道开发标准接口与协议,打造国内基于Chiplet的生态。

中科院计算所副研究员王郁杰博士主持了最后的圆桌会议,会议中针对“Chiplet设计技术是不是未来芯片敏捷开发的使能技术?对芯片的设计流程有何影响?Chiplet是否有利于我国摆脱现有EDA与芯片制造行业卡脖子现状?国内Chiplet制造、集成与封装技术的现状与未来?”这几个问题,几位演讲人展开了激烈的讨论。

刘勤让认为Chiplet是对整个设计、技术以及产业形态的重塑,无论是从成本、摩尔定律的困局以及未来的云化服务商来看,Chiplet是技术和产业双重需要的发展趋势,这对我们摆脱现有困局具有现实意义。

王迎春也认为,从EDA发展的角度来看,Chiplet的发展是必然的趋势,国际诸多组织都纷纷在Chiplet上发力。但EDA的创新是在核心基础创新,解决卡脖子的问题不仅仅在Chiplet上,在EDA的布局布线、逻辑综合以及最底层的算法上都要有创新。当下芯片行业备受重视,人才不断涌进芯片行业,这对我们来说是一大利好。

张竞扬指出,解决卡脖子问题不是把别人的手挣脱开,而是Chiplet可以孕育出更多创新的应用。全球芯片产业为4600多亿美金,而全球GDP有80多万亿美金,还有很多芯片应用场景待开发。目前包括智能家居和机器人在内的诸多应用,按照今天的芯片设计成本攀升曲线,短期内是很难大规模普及的。如果能通过Chiplet技术,大幅降低芯片的成本,再借助中国的生态优势,打通更多的碎片化应用场景,则能产生更多的订单,进一步扩大中国的消费市场。

王启东表示,Chiplet可以缓和目前卡脖子的现状,但它并不能从根本上解决这个问题。从系统应用角度来看,Chiplet可以支持大家百花齐放。而在关键的CPU、GPU、FPGA以及模拟工艺、特色工艺来看,集成电路的先进工艺技术仍是必修课,需要工艺人员的不懈努力解决高端制造问题,并与前端的IP、EDA进行互动形成协同的发展才可以解决现在的问题。

王颖认为,长远来看,Chiplet技术确实是一项很重要的形式,但并不会完全替代PCB这样的集成技术。对于当前卡脖子问题,Chiplet作为权宜之计,可以通过异质集成弥补先进IC工艺短板,追求系统级的效能优势,但不能从根本上解决问题,因为到新赛道之后,还是要考验核心技术,例如Chiplet设计方法涉及的2.5D,3D集成制造技术,三维版图设计、电源网络、物理设计仿真等EDA技术。他期待有机构和工业界联合起来,通过开源与标准化组织方式,率先把Chiplet设计模式所需的重要物理IP或者接口协议标准搭建起来,让大家在上面做迭代,真正在Chiplet的赛道上避免卡脖子问题。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2475期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

存储|晶圆

|

SiC|AMD|射频|台积电|美国|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie