RISC-V能改变GPU吗?

来源:本文内容来自[electronicdesign],谢谢。

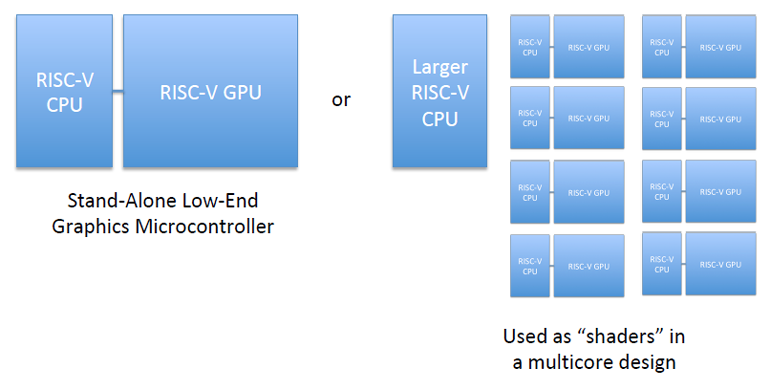

RISC-V能处理GPU的事务吗?这项工作正在进行中,可以通过创建一个具有自定义可编程性和可扩展性的小型区域高效设计来实现这一目标。

GPU + RISC-V

-

这有点像VLIW(但不是真的)。

-

指令块之前带有寄存器标记,这些标记为该块内的标量指令提供了额外的上下文。

-

子块包括向量长度,旋转,向量/宽度覆盖和预测。

-

所有这些都添加到标量操作码中!

-

没有矢量操作码(也不需要任何操作码)。

-

在矢量上下文中,它是这样的:如果标量操作码使用寄存器,并且该寄存器在矢量上下文中列出,则将激活矢量模式。

-

激活会导致硬件级别的for循环发出多个连续的标量运算(而不只是一个)。

-

实现者可以自由地以他们想要的任何方式来实现循环-SIMD,多问题,单执行;几乎任何东西。

RV64X

-

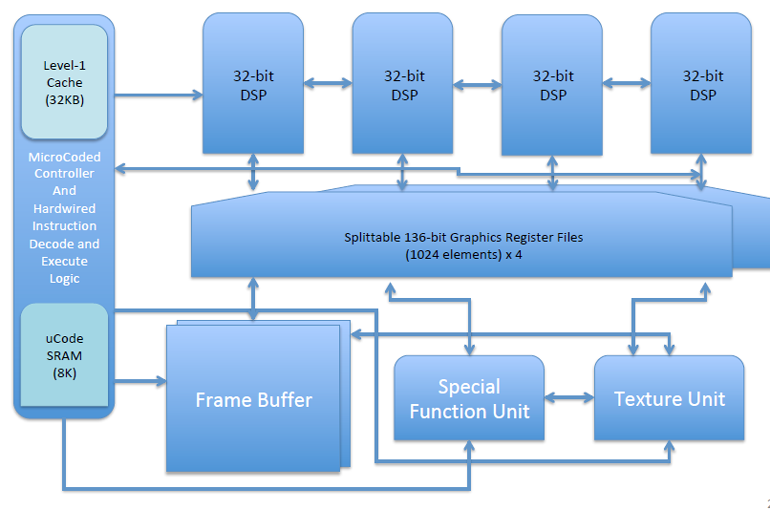

指令/数据SRAM缓存(32 kB)

-

微码SRAM(8 kB)

-

双功能指令解码器(实现RV32V和X的硬连线;用于自定义ISA的微编码指令解码器)

-

四向量ALU(32位/ ALU-固定/浮动)

-

136位寄存器文件(1k个元素)

-

特殊功能单元

-

纹理单位

-

可配置的本地帧缓冲区

下一步是什么

点击文末【 阅读原文 】。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2578内容,欢迎关注。

推荐阅读

★ 成熟制程工艺Top榜单:中芯国际与台积电之间只差一个UMC

原创

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|MCU |射频|封测|美国|苹果|华为|汽车芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 象帝先计算技术与鸿合科技在第83届中国教育装备展示会上举行战略签约

- 2 从芯来到“香山”,芯华章助力国产RISC-V生态做了哪些事?

- 3 四年17颗芯片,思特威实现CIS高端手机应用突围

- 4 Arm发布新一代NPU,助力边缘AI腾飞