来源:内容由于半导体行业观察(ID:icbank)编译自「

semiwiki

」,谢谢。

在2月举行的SPIE高级光刻会议上,ASML展示了有关其深紫外线(DUV)和极紫外线(EUV)曝光系统的最新信息。笔者最近采访了ASML的Mike Lercel,就这些演示文稿进行了深入讨论。

尽管EUV得到了所有关注,但大多数层仍仍然使用DUV系统曝光,在可预见的将来,这可能仍然适用。

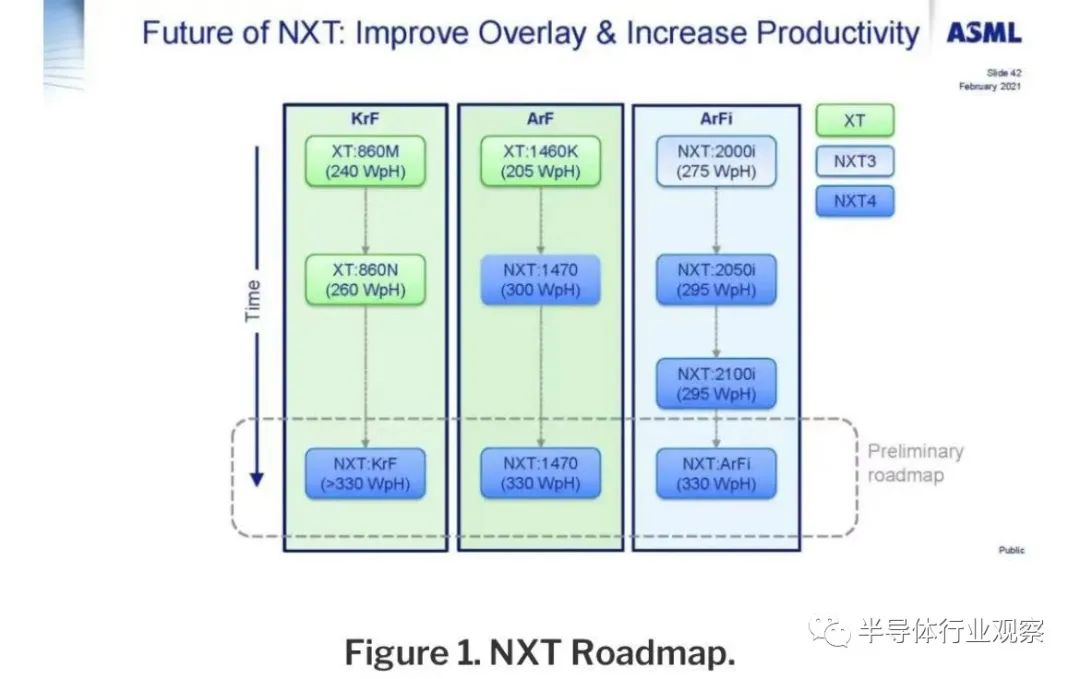

ASML已生产了两个DUV平台,即用于干式曝光工具的XT平台和用于浸没的NXT平台。NXT是更快,更复杂的平台。

对于领先的沉浸式技术,ASML推出了面向ArF浸入(ArFi)的第四代NXT平台——NXT:2050i。新系统具有新的晶圆处理机(wafer handler

),晶圆载物台(wafer stage

),标线片载物台(reticle stage

),投影透镜(projection lens

),激光脉冲展宽器(laser pulse stretcher)和浸没罩(immersion hood)。

这样就可以更快地进行硅片对硅片的排序,更快的测量,防护膜偏斜校正(pellicle deflection )以及具有改善覆盖率的改善斑点。

新系统的吞吐量为每小时295个晶圆(wph)。

较长期的计划是建立一个330 wph的系统(见图1)。

ASML现在正在采用NXT平台,并在第一台面向ArF Dry的NXT:1470系统上移植干镜,该系统提供300wph(比NXT:20250i快一点,因为它没有沉浸开销)。NXT:1470的300 wph吞吐量高于XT:1460K的约200 wph的吞吐量。将来,NXT:1470的吞吐能力将进一步提高到330 wph(见图1)。

还计划以330 wph的速度将KrF干镜移植到NXT平台上(见图1)。

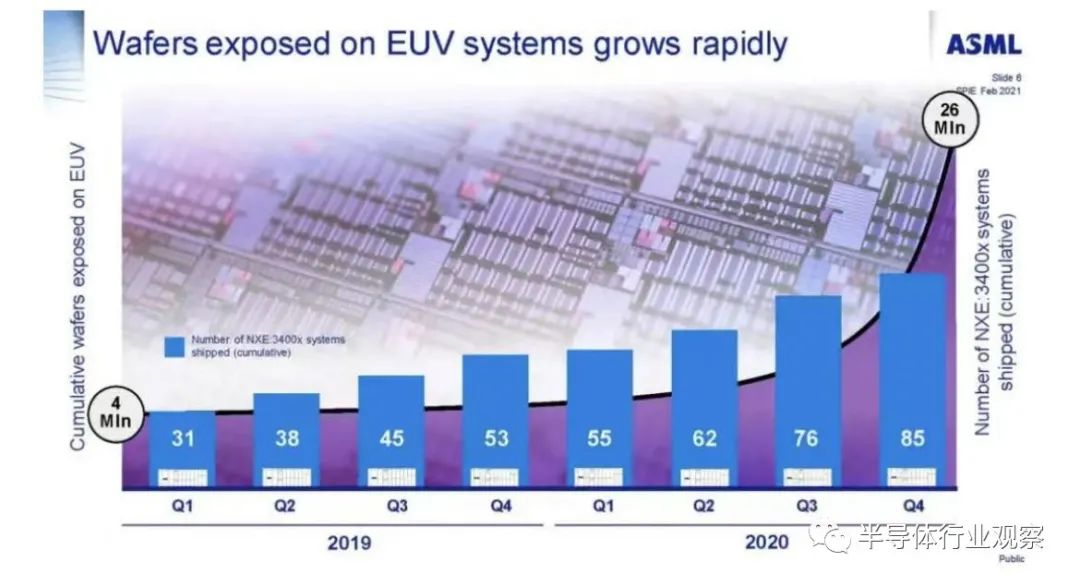

随着三星和台积电在7nm和5nm逻辑生产以及三星在1z DRAM生产中加大对标准0.33数值孔径(NA)系统的使用,EUV曝光的晶圆数量正在迅速增长(见图2)。

NXE:3400C系统自2019年底推出以来一直在发货,而新的NXE:3600D应该在今年晚些时候开始发货。每个新系统都提供了改进的吞吐量和覆盖。

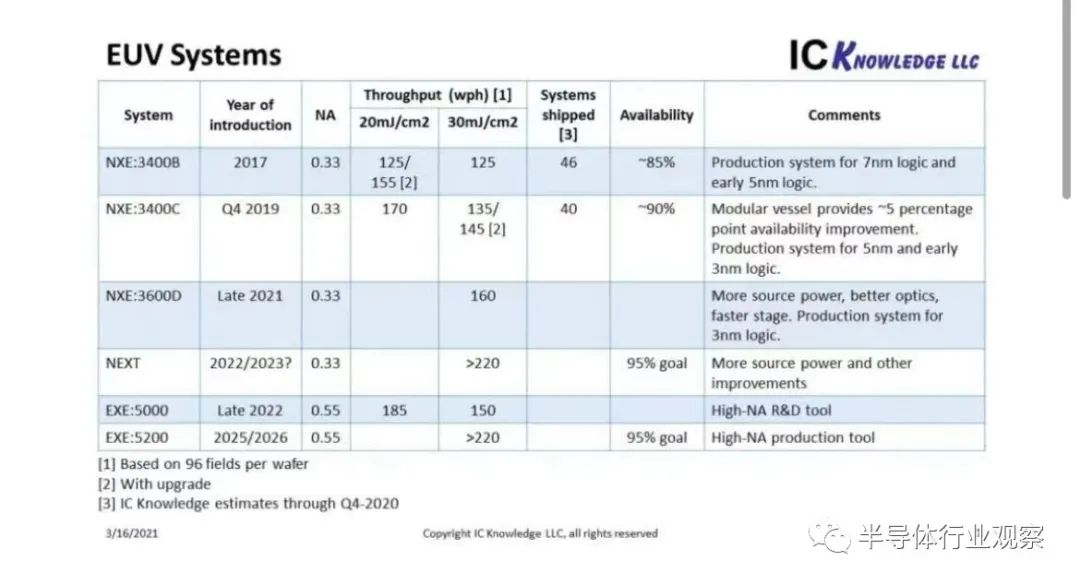

图3给出了将在下一部分讨论的0.33 NA和High-NA 0.55NA系统的摘要。

1.第一列列出了从NXE3400B系统(最初的生产系统)开始的过去,现在和将来的系统。

2.第二列提供每个系统的引入日期。值得注意的是,新的NXE:3600D应该在今年晚些时候以更高的性能交付,而第一批高NA系统应该在2022年晚些时候交付。

3.第三列给出了系统的数值孔径,其中0.33NA代表当前系统,而0.55NA代表正在开发的高NA系统。

4.接下来的两列显示了ASML证明的20mJ / cm 2和30mJ / cm 2剂量的通量。这些吞吐量基于更典型的DRAM应用中每个硅片的96 field。

5.发货的系统数量是IC Knowledge对2020年第4季度按类型发货的NXE:3400B和NXE:3400C系统数量的估计,ASML不提供这个。

6.下一栏是NXE:3400B当前的可用性约85%,NXE:3400C当前的可用性约90%。3400C具有新的模块化容器,可减少停机时间。长期ASML的长期目标是使其达到DUV系统典型的95%可用性。

7.最后一栏介绍了有关系统和用法的一些注释。我们认为7nm逻辑生产主要在3400B上进行,而5nm在3400C上进行。我们预计即将在未来一到两年内投入生产的3nm工艺将主要在3600D系统上生产。

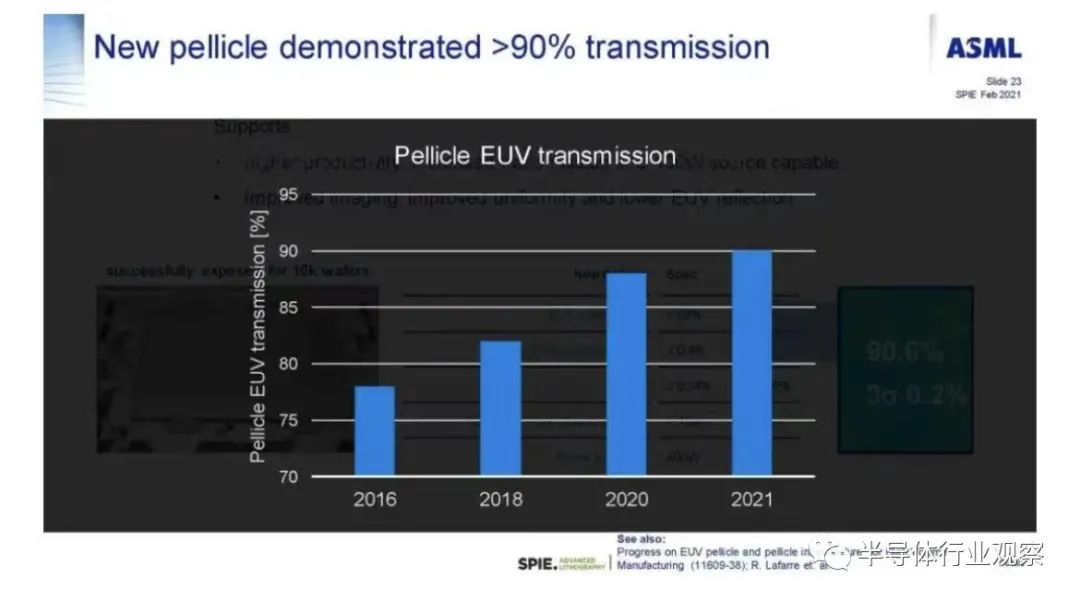

密集图案EUV的关键推动因素是Pellicles的可用性,现在有可用Pellicles可用。Pellicles的使用会降低生产量,是否使用Pellicles取决于你所打印的图案密度。图4显示了EUV Pellicles透射的状态。

High-NA现在已经从PowerPoint幻灯片发展到工程设计,再到构建模块和框架。预计首批High-NA工具(0.55NA)将于2022年下半年交付。这些EXE:5000系统可能与EXE:5200系统一起用于研发,原因是EXE:5200系统将于2025/2026年成为第一批High-NA生产系统。(见图3)。

当前的0.33NA系统一次曝光即可打印到大约30nm的间距。现在正在进行工作以一次曝光来演示28nm以及最终26nm的线条和空间。台积电目前正在生产的5nm工艺的M0间距为28nm,我们认为这一层在当前生产中可能是双图案的EUV,而其余使用EUV的层则是单图案。对于将于今年晚些时候开始出现风险试产的的台积电3nm工艺,我们预计将有几个EUV双图案金属层。目前估计0.55NA系统进入生产的时间大约在2025/2026时间范围内,我们可能会看到2nm的代工厂和Intel的5nm工艺正在生产,然后再进行广泛的EUV双重打样。055NA EUV可能会首先出现在晶圆厂的生产中。

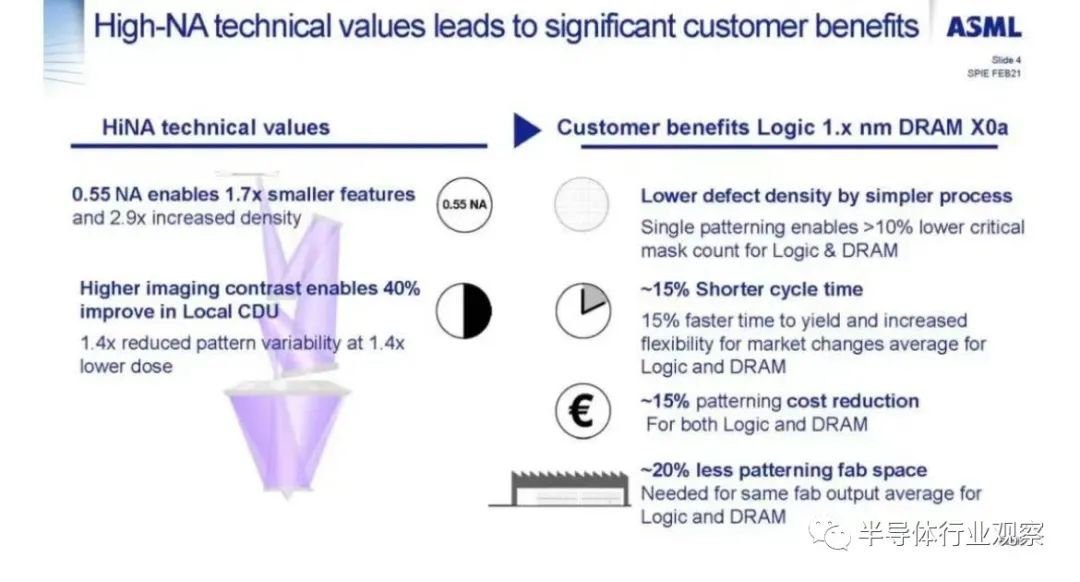

与0.33NA EUV相比,0.55NA EUV的另一个值是较高的对比度,这就让他们可以以低得多的剂量打印出密集的特征,从而提高了通量(图3是特定剂量的通量,不考虑降低剂量)。图6展示了0.55NA的优势。

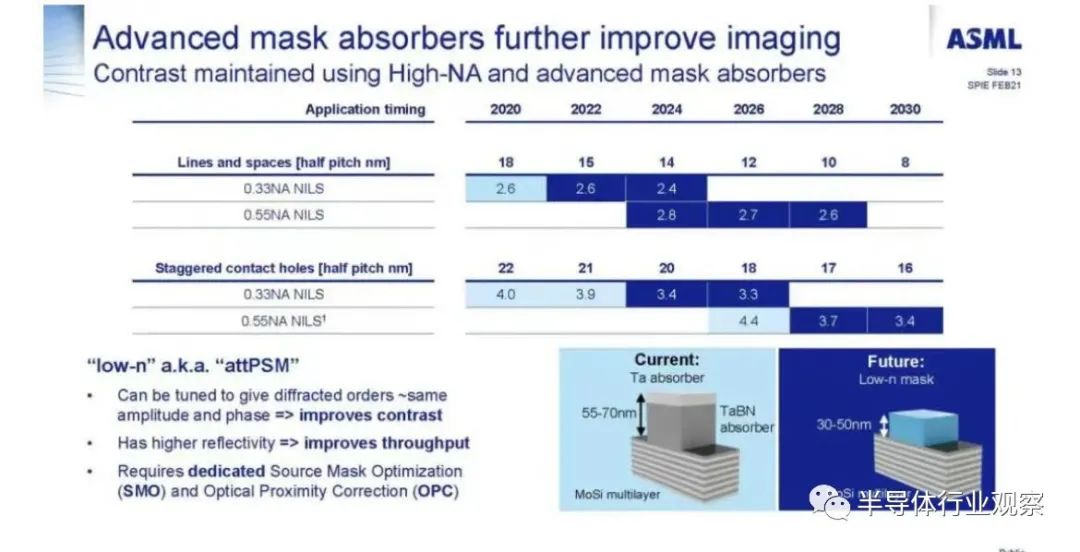

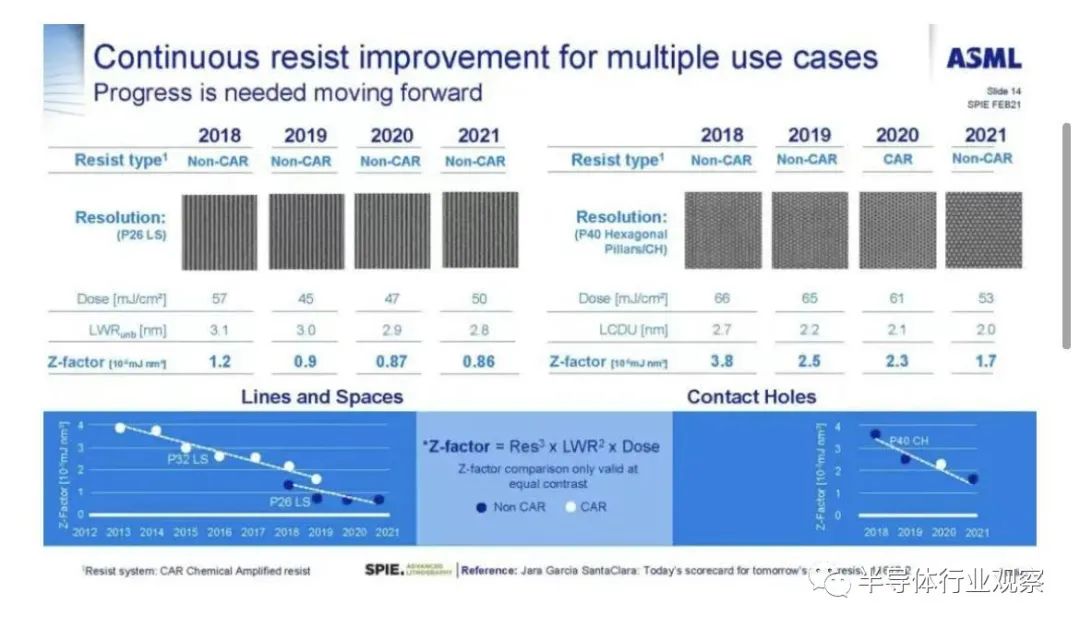

还正在进行改进的EUV掩模吸收层的工作,以提高对比度和分辨率,请参见图7,并要改进光刻胶,请参见图8。

ASML继续在其整个DUV和EUV系统产品组合中提高吞吐量和分辨率。随着高NA系统制造的进行,通往1.5nm逻辑及更高工艺的道路正在酝酿之中。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2618内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备|模拟芯片

|射频|传感器|晶体管|ASML

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!