全新架构数字仿真器——穹鼎Galaxsim

2022-02-16

14:19:52

来源: 芯华章科技

点击

在芯片前端设计工程师的日常工作中,需要用硬件描述语言Verilog HDL将各种算法/协议等实现后,再进行RTL的功能仿真,以便在软件环境中,验证电路的行为和设想中的是否一致。这也意味在流片前,工程师需要花大量时间利用数字仿真器来验证芯片,保证其功能的正确。

作为芯片验证必不可少的一个环节,仿真技术是保证芯片功能正常的关键签核(sign-off)技术,通过计算机结合测试激励来模拟芯片在真实环境下的运行状况,帮助工程师通过各种调试手段来判断运行结果是否符合预期。数字仿真器主要是针对数字电路的仿真,设计工程师需要应用硬件描述语言来设计电路,而验证工程师也需要用抽象层的HDL来搭建测试环境;仿真工具需要解释编译这些HDL代码,并计算出仿真结果,以便工程师检查结果。

伴随设计验证语言和方法学不断推陈出新,各种应用平台也层出不穷。这一系列的技术发展都给数字仿真器带来了前所未有的挑战。设计具有竞争力的片上系统(SoC)需要合理地利用各种高精尖的技术。对于数字仿真器来说,它面临的挑战不仅仅是芯片规模上的增长,还有伴随而来的一系列问题,包括:算力受限、调试效率低下、平台单一化等。

多年来,业内人士通常认为一款好的数字仿真器,应该具备以下条件:

• 保障仿真结果的正确性和一致性,满足sign-off (签核)的要求

• 具备对IEEE1364和IEEE1800标准语法的支持,具有语法点、功能点的合规性

• 仿真器核心可以实现高效的调度器,灵活强大的随机求解器

• 在调试方面,工具应当紧密融合各种调试应用,提高调试有效性

但更进一步,针对产业发展现状的痛点,先进的数字仿真器还应该具备以下特质:

• 为了进一步利用新的计算架构和平台,除了传统的X86,更能无缝地支持如ARM等其他新型处理器架构及原生云计算架构,并能有效利用并行计算支撑高性能编译与运算

• 仿真器和其他验证工具具有高度的融合性,及统一覆盖率的数据结构,以保证各种工具覆盖率收集的有效性

芯华章仿真器核心研发团队具备数十年相关领域研发经验,曾在跨国公司成功主导过大型仿真器项目,对验证语言、方法学、仿真器核心构架、算法、优化有着丰富的技术储备。

基于对前沿技术发展趋势的的判断,并结合行业现实的挑战进行深入的研究和探索,芯华章在经过一年多的研发积累,并得到国内多个知名客户配合打磨后,推出一款独立自主、全新架构的国内领先水平仿真器——穹鼎 GalaxSim。该产品创新性地使用新的软件框架,提供多平台支持,并且已在多个基于ARM平台的国产架构上测试通过。

目前,穹鼎GalaxSim支持IEEE1800 SystemVerilog 语法、IEEE1364 Verilog 语法,以及IEEE1800.2 UVM方法学,在语义解析、仿真行为、时序模型上,已达到主流商业仿真器水平。穹鼎GalaxSim仿真器能够提供统一的覆盖率数据库,并兼容芯华章旗下穹瀚GalaxFV等其他验证工具,结合穹景GalaxPSS智能验证系统提供的丰富测试场景,可以加速覆盖率收敛,高效地解决业界其他工具缺乏兼容性的问题,进一步提高验证效率。

使用穹鼎GalaxSim的验证实例

为了验证GalaxSim仿真的功能正确性,调试的易用便捷性,以及性能上是否能够满足客户的需求,我们特地把基于Verilog语言的蜂鸟E203开源 RISC-V CPU设计运行在芯华章的仿真器上,作为一个演示demo。

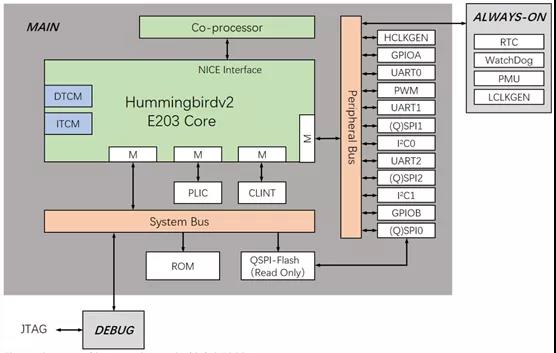

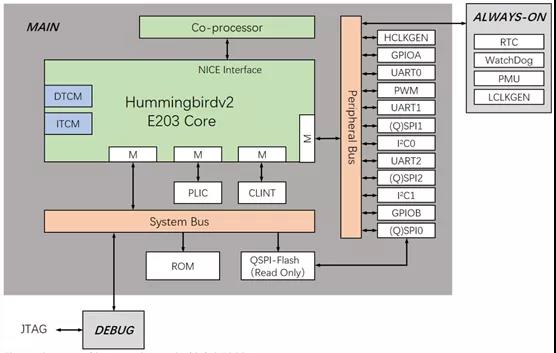

蜂鸟E203是国内首个开源RISC-V处理器,从2018年发布至今,积累了广泛的用户。E203内核采用2级流水线结构,能够运行RISC-V指令集,支持RV32IMAC等指令子集的配置组合,具备工业级开发标准,符合当前处理器架构往DSA(Domain Specific Architecture)发展的新趋势,因而具有广泛的代表性。

开源蜂鸟E203 SoC整体框图

穹鼎仿真器首先需要读取芯片设计,之后经过解析和抽象,转换为仿真器内部紧凑高效的数据结构,并基于新一代编译技术,快速生成原生平台仿真程序。同时,我们打开波形调试工具,IC工程师即可以运行仿真程序来进行验证。

编译完成后,我们执行仿真程序。程序在运行后,同时进行信号波形的文件转储,以供调试。本次验证实例中的环境技术包含多款国产化产品,涉及芯片设计、处理器、服务器、操作系统等环节。

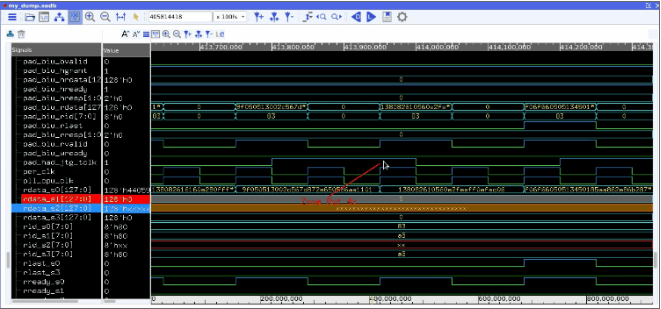

穹鼎 GalaxSim基于芯华章FusionVerify 智V验证平台,支持自主研发的新波形格式及波形调试工具,用户能够方便地查看信号波形,快速定位到缺陷的时间片和异常信号,从而进行修复。

同时,我们还用同样的设计放在第三方仿真器上运行。这样,一方面对比仿真结果以探索功能的正确与否,另一方面可以对比仿真的效率,便于对比工具的性能指标。

经过实测和比较,GalaxSim运行结果完全和商业仿真器一致,性能也达到预期的要求。多个客户试用在GalaxSim上运行蜂鸟的demo后,表达了对产品的高度认可:调试工具使用流畅,用户界面操作友好易用,且支持不同处理器架构。

产品亮点

国内率先提出多架构支持的仿真器,具备:

• 灵活的可移植性,友好的软硬件生态支持

• 支持不同的处理器计算架构,包括X86、ARM、MIPS、RISC-V、NPU、GPGPU等

传统的EDA工具大多数和单一CPU构架耦合度高,例如某些EDA工具仅支持X86的平台。一旦需要迁移到另一种平台上,所需要的研发工作量是巨大的。如今,处理器生态越来越多样化,未来的平台不再是某个单一处理器的平台,降低EDA工具对底层CPU构架的耦合度,可以让用户更加有效地把工具部署在任何平台上,也让产品有更多应用空间。

全面支持多种HDL语法,语义解析一致性强

• 兼容Verilog标准IEEE1364

• 全面支持SystemVerilog、UVM标准(IEEE1800,IEEE1800.2)

• 原生支持,不需要修改客户源代码

仿真器对语法正确解析决定了它能否正确理解设计意图,同时也可以避免相同的编码在不同的仿真器下产生不同仿真结果。Verilog标准(IEEE1364)和SystemVerilog标准(IEEE1800)定义的这两种语言的语义非常的复杂,关键字众多,各种组合情况近乎无穷。穹鼎GalaxSim可以在构建仿真器的测试用例时考虑语法的各个方面,以及各种边界场景,做到全面完整的测试。

调试功能卓越,可观测性表现形式丰富

• 支持VCD和FSDB 波形导出(配合第三方库)

• 支持芯华章自研波形格式XEDB

• 支持快速的代码覆盖率(Code coverage)

调试的重点在于可观测性和可控制性。穹鼎GalaxSim针对不同的场景提供各种有效的数据表现形式,并在不同数据形式间可以同步数据标注(annotation)。此外,穹鼎GalaxSim降低了工具的使用门槛,可以让初级用户也非常快速地掌握调试技术,并且提供通用语言的二次开发的接口。

穹鼎GalaxSim的优异性能得到了生态伙伴的高度认可。

陈 刚 中科院半导体所副研究员

利用芯华章仿真工具GalaxSim,我们在两周内就将设计调通。和其他商用仿真器对比结果显示,芯华章GalaxSim对RTL行为仿真行为正确,在性能上,很多场景和其他商用工具已经基本一致。我们期待和芯华章的进一步合作。

黄 武 芯华章科技产品和业务规划总监

为了保证语法的合规性和仿真精确度,我们对产品进行了严苛的各种测试,包括对IEEE1364、IEEE1800各个语法点的分析,和结合主流商业仿真器的对比测试,确保工具在语义解析、仿真行为、时序模型上保持一致,从而有效帮助用户提高验证效率,加快验证收敛速度。

引用:

[1] https://doc.nucleisys.com/hbirdv2/overview/overview.html#introduction

责任编辑:sophie

-

- 半导体行业观察

-

- 摩尔芯闻