iPhone7上的秘密武器,完全解码扇形封装

本文来自新电子、半导体技术等相关资料整理,感谢原作者付出,如转载不当,请及时联系后台,谢谢。

从今年年初就传出,苹果将在iPhone 7上的A10处理器和天线开关模组使用扇形晶圆级封装(Fan-out Wafer Level Packaging,简称FoWLP)技术取代传统PCB,而A10的制造商台积电正式FoWLP技术的领先者。在台积电内部,他们把FoWLP称作InFoWLP,其中In代表integrated,也就是集成的意思。如无意外,FoWLP将如约出现在iPhone7上。

研究机构Yole Developpement指出,2016年是扇出封装发展史上的重要转折点。在苹果(Apple)与台积电的领导下,已发展多年的扇出封装技术未来将被更多芯片业者采纳。

研究机构Yole Developpement指出,2016年是扇出封装发展史上的重要转折点。在苹果(Apple)与台积电的领导下,已发展多年的扇出封装技术未来将被更多芯片业者采纳。

Yole先进封装与制造分析师Jerome Azemar表示,对扇出封装技术发展而言,2016年是重大转折点的原因有三:第一,苹果处理器的采用,为扇出封装创造出庞大的需求量,奠定规模经济的基础;第二,在台积电的技术突破下,扇出封装技术可支援的I/O数量大增。在此之前,扇出封装主要锁定的都是I/O数量较少的应用。第三,苹果可望发挥示范作用,吸引其他芯片业者加入使用扇出封装的行列。

扇出型封装的市场营收预测(按市场类型划分)

Yole进一步预估,未来扇出封装可能会分成两种典型应用,其中之一是一般的单芯片的扇出封装,主要应用是基频处理器、电源管理、射频收发器等芯片。这是扇出封装的主要市场。另一个主流则是高密度扇出封装,主要针对应用处理器、记忆体等具备大量I/O接脚的芯片。Yole认为,前者是稳定成长的市场,后者则还需要搭配出更多新的整合技术,因此发展上还有些不确定性,但未来的成长潜力非常巨大。

既然前景那么看好,我们有必要对FoWLP有深入的了解

什么是扇形晶圆级封装?

理论上,晶圆级封装由于不需要中介层(Interposer)、填充物(Underfill)与导线架,并且省略黏晶、打线等制程,因此能够大幅减少材料以及人工成本;除此之外,WLP大多采用重新分布(Redistribution)与凸块(Bumping)技术作为I/O绕线手段,因此WLP具有较小的封装尺寸与较佳电性表现的优势,目前多见于强调轻薄短小特性的可携式电子产品IC封装应用。

WLP封装优点包括成本低、散热佳、电性优良、信赖度高,且为芯片尺寸型封装,尺寸与厚度皆可达到更小要求等。WLP封装另一项优势在于封装制程采取整批作业,因此晶圆尺寸越大,批次封装数量越多,成本能压得更低,符合晶圆厂由8吋转进12吋发展趋势,WLP专业封测厂利润空间也可提高。

晶圆级封装的优势

传统的WLP封装多采用Fan-in型态,应用于低接脚(Pin)数的IC。但伴随IC讯号输出接脚数目增加,对锡球间距(Ball Pitch)的要求趋于严格,加上印刷电路板(PCB)构装对于IC封装后尺寸以及讯号输出接脚位置的调整需求,因此变化衍生出扩散型(Fan-out)与Fan-in加Fan-out等各式新型WLP封装型态,其制程甚至跳脱传统WLP封装概念。

Fan-In WLP与Fan-Out WLP的结构比较图

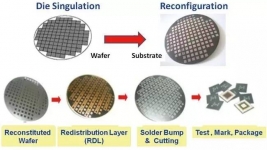

Fan-Out WLP技术是先将芯片作切割分离,然后将芯片镶埋在面板内部。其步骤是先将芯片正面朝下黏于载具(Carrier)上,并且芯片间距要符合电路设计之节距(Pitch)规格,接者进行封胶(Molding)以形成面板(Panel)。后续将封胶面板与载具作分离,因为封胶面板为晶圆形状,又称重新建构晶圆(Reconstituted Wafer),可大量应用标准晶圆制程,在封胶面板上形成所需要的电路图案。由于封胶面板的面积比芯片大,不仅可将I/O接点以散入(Fan-In)方式制作于晶圆面积内;也可以散出(Fan-Out)方式制作于塑胶模上,如此便可容纳更多的I/O接点数目。

Fan-out WLP构装技术

Fan-out WLP的市场现状

大家都知道台积电本身是一个晶圆代工厂,但其实很多年前,台积电就布局封测产业。当时业界还为台积电的布局所震惊,而到了现在也是收成的时候了。

很多年前,台积电就透露已延伸于高阶封测的布局,有意力拱InFO(Integrated Fan-out)作为次世代大宗量产产品的主流封测技术,此举在封测产业投下震撼弹。

业界评估,台积电跨足低成本的InFO产品线,应将着眼于手机应用处理器(AP)所采用的PoP封装市场,现已有至少4家重量级客户正评估或即将采纳此方案,将成为目前主流封装厂的强劲威胁。

台积电原本在高阶封装技术上,定调将以CoWoS(Chip on Wafer on Substrate)作为2.5D/3D IC重点研发方向,不过CoWoS因价格过高而为人诟病,近来在客户端的进展并不显著。为了取得主流应用产品,台积电近年来也积极开发Fan-out PoP技术,首波攻势便将聚焦于手机AP与存储堆叠的PoP封装型态,而目前也已经成功夺得众家手机芯片重点厂商的关注。

封测业者指出,Fan-out最显著的优势就是可以省去载板,因而成本可以较传统的PoP封装至少下滑约2~3成以上,大幅节省芯片封装的成本,并可以应用于手机AP或其他RF、电源管理IC等大宗应用市场,这足以说明台积电想要抢快推出Fan out技术的意图。

业界普遍看好Fan-out技术在进入量产后,将有相当潜力来取代传统的覆晶封装如FCCSP、FCBGA等,因此,早在台积电宣布之前,近3年各家专业封测厂包括新科金朋(Stats ChipPAC)、艾克尔(Amkor)、硅品、日月光等,均已将Fan-out技术或者系出同源的内埋载板技术纳入先进制程蓝图中。

台积电购入高通龙潭厂后,正密集改造成该厂区,目标成为台积电先进封测重镇。台积电正积极购入先进封测设备,上周董事会通过核准1,253.58亿元资本预算,加速先进制程及封装产能扩充及布建。

半导体设备厂表示,台积电将以提供具成本优势的InFO先进封装,提供主力客户苹果从晶圆代工到后段封测的统包服务,其中,单是为苹果提供的月产能即高达8.5万至9万片。

三星为了和台积电角逐,也在跟进这个技术。

根据韩国英文媒体《THE KOREA TIMES》的报导,目前三星正研发新的扇形晶圆级封装技术,以企图在与台积电(TSMC)的激烈竞争中,多取得苹果iPhone智能手机的处理器订单。未来,在该技术成功研发后,在高阶芯片的封装上将不再需要用到印刷电路板,可以使得智能手机未来的设计达到更薄、更高效能的发展。

报导中指出,被称做FoWLP 的扇形晶圆级封装技术,未来将是三星从台积电手中抢回苹果订单的重要利器。报导引述一位匿名的分析师指出,虽然几乎已经笃定,台积电已经成为苹果2016 年将推出新款iPhone 手机(iPhone 7) 的处理器制造商。但是,透过FoWLP 的扇形晶圆级封装技术,三星期望在下一代新款iPhone 手机(iPhone 7S) 从台积电手中抢回部分的订单。

不过,该名分析师强调,如果三星要从台积电手中抢回部分iPhone 的订单,其关键就在于三星能有多少比例的产能将采用FoWLP 的扇形晶圆级封装技术。因为,现阶段相对于三星来说,台积电未来将持续保有50% 到60% 的产能采用晶圆级封装技术。据了解,未来若采用三星的FoWLP 扇形晶圆级封装技术之后,将可为新款手机降低超过0.3 毫米厚度,以及提升30% 以上的手机总体效能。

报导中还强调,根据韩亚金融投资的一份报告中指出,继台积电之后,三星也新发展扇形晶圆级的封装技术,有助于减低该公司在先进电路连接(ACI) 上的投资,间接减少了三星集团减少对中长期潜在的风险。不过,该报告仍质疑三星的扇形晶圆级封装技术要到2017 年上半年才能大量生产,而台积电的晶圆级封装技术,则从2016 年第3 季开始就将开始量产嵌入式芯片,这时间点上对三星来说仍是处于劣势。

除了台积电和三星之外,STATS ChipPAC(新加坡星科金朋)将利用JCET(江苏长电科技)的支持进一步投入扇出型封装技术的开发(2015年初,江苏长电科技以7.8亿美元收购了新加坡星科金朋);ASE(日月光集团)则和Deca Technologies建立了深入的合作关系(2016年5月,Deca Technologies获日月光集团6000万美元投资,日月光集团则获得Deca Technologies的M系列扇出型晶圆级封装技术及工艺授权);Amkor(安靠科技)、 SPIL(硅品科技)及Powertech(力成科技)正瞄准未来的量产而处于扇出型封装技术的开发阶段。

Fan-out WLP面临的瓶颈

虽然Fan-Out WLP可满足更多I/O数量之需求。然而,如果要大量应用Fan-Out WLP技术,首先必须克服以下之各种挑战问题:

Fan-Out WLP面临的挑战

(1)焊接点的热机械行为: 因Fan-Out WLP的结构与BGA构装相似,所以Fan -Out WLP焊接点的热机械行为与BGA构装相同,Fan-Out WLP中焊球的关键位置在硅芯片面积的下方,其最大热膨胀系数不匹配点会发生在硅芯片与PCB之间。

(2)芯片位置之精确度: 在重新建构晶圆时,必须要维持芯片从持取及放置(Pick and Place)于载具上的位置不发生偏移,甚至在铸模作业时,也不可发生偏移。因为介电层(Dielectric Film)开口,导线重新分布层(Redistribution Layer; RDL)与焊锡开口(Solder Opening)制作,皆使用黄光微影技术,光罩对准晶圆及曝光都是一次性,所以对于芯片位置之精确度要求非常高。

(3)晶圆的翘曲行为: 人工重新建构晶圆的翘曲(Warpage)行为,也是一项重大挑战,因为重新建构晶圆含有塑胶、硅及金属材料,其硅与胶体之比例在X 、Y、Z三方向不同,铸模在加热及冷却时之热涨冷缩会影响晶圆的翘曲行为。

(4)胶体的剥落现象: 在常压时被胶体及其他聚合物所吸收的水份,在经过220~260℃回焊(Reflow)时,水份会瞬间气化,进而产生高的内部蒸气压,如果胶体组成不良,则易有胶体剥落之现象产生。

而由于传统Fan-Out WLP是在含有芯片(Chip)及铸模(Molding)的表面进行布线(Routing),如图6所示,在芯片朝下作灌胶铸模时,可能会有胶液渗透(Mold Flash)到芯片边角,当胶液覆盖到芯片的接合垫(Bonding Pad)时,将会造成良率上之损失。如果硅芯片与铸模的交接过渡区(Transition Zone)不平顺,以及硅芯片与铸模的热膨胀系数不同,会对重新布线(Redistribution Layer; RDL)结构产生应力引发之可靠度问题(Stress Induced Reliability Issue) 。

传统Fan-Out WLP在含有芯片及铸模的表面进行布线

针对以上传统Fan-Out WLP所面临之挑战点,B. Rogers等提出一种新型的完全铸模(Fully Molding)Fan-Out WLP技术,可以解决以上所述之问题,如图所示为Fully Molding Fan-Out WLP构装结构与横截面照片。

完全铸模Fan-Out WLP构装结构与横截面照片

Fully Molding Fan-Out WLP制造包含四大制程,各制程简单描述如下:

1.铜柱制造(Copper Pillar):先将铜柱(Copper Pillar)制造于原来半导体晶圆的I/ O点上。

2.面板制造(Penalization):进行铸模(Molding)之镶板制程(Penalization Process)。镶板制程会将芯片正面及侧边使用铸模灌胶作完全覆盖,镶板正面进行研磨(Front Grind)以露出铜柱,只让铜柱由晶圆正面穿越铸模作电流传输路径。

3.散出制程(Fan-Out Process):制作导线重新分布层(RDL)及凸块(Bump),将铜柱与凸块阵列(Bump Array)作连接。

4.完成构装(Package Finishing):镶板背面研磨(Back Grind),最后用环氧树酯(Epoxy)将晶圆背面封住,进而完成Fan-Out WLP构装结构。

完全铸模(Fully Molding)Fan-Out WLP技术制造流程

前段IC制造技术的快速进展,以及行动电子产品对于可携式及多功能之需求,微电子构装持续朝小尺寸、高性能、及降低成本发展。使得传统Fan-In WLP构装面对极大的技术瓶颈,所幸业界后续发展出Fan-Out WLP构装技术。至于未来会怎样发展,那就看业界怎么进一步努力发展了。

【关于转载】:转载仅限全文转载并完整保留文章标题及内容,不得删改、添加内容绕开原创保护,且文章开头必须注明:转自“ 半导体行业观察icbank”微信公众号。谢谢合作!

【关于投稿】:欢迎半导体精英投稿,一经录用将署名刊登,红包重谢!来稿邮件请在标题标明“投稿”,并在稿件中注明姓名、电话、单位和职务。欢迎添加我的个人微信号MooreRen001或发邮件到 jyzhang@moore.ren

点击阅读原文,查看更多半导体高薪职位

-

- 半导体行业观察

-

- 摩尔芯闻