历史上的一些“大”芯片回顾

2021-12-11

14:00:09

来源: 半导体行业观察

来源:内容来自

痴汉水球

,谢谢。

英特尔这间世界第一半导体大厂,过去几十年来,都习惯靠制程技术优势与庞大产能「辗压」竞争对手,时过境迁,随着专业晶圆代工商业模式崛起,现在反倒变成「双A」 (AMD、苹果)看似按着英特尔的头在地上摩擦。

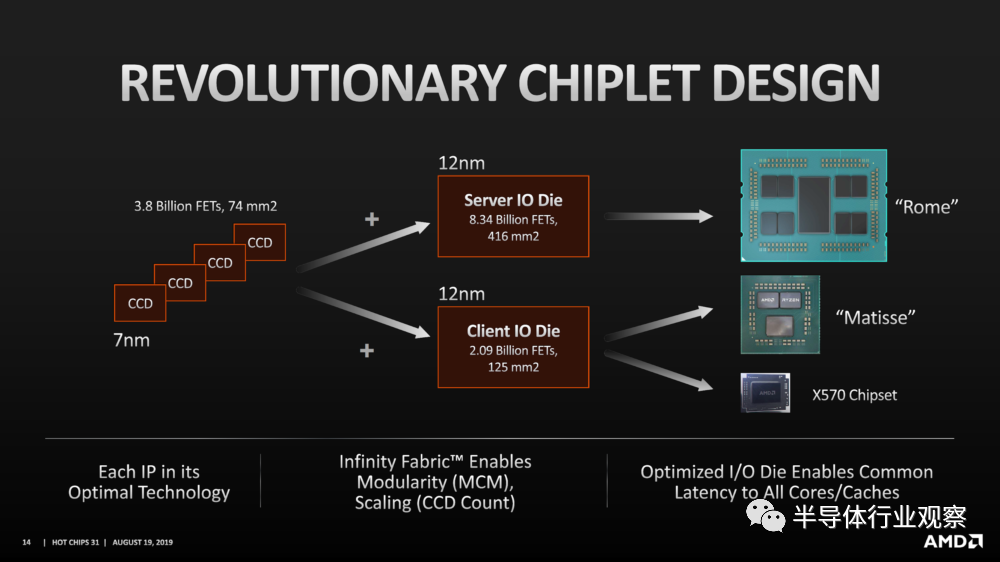

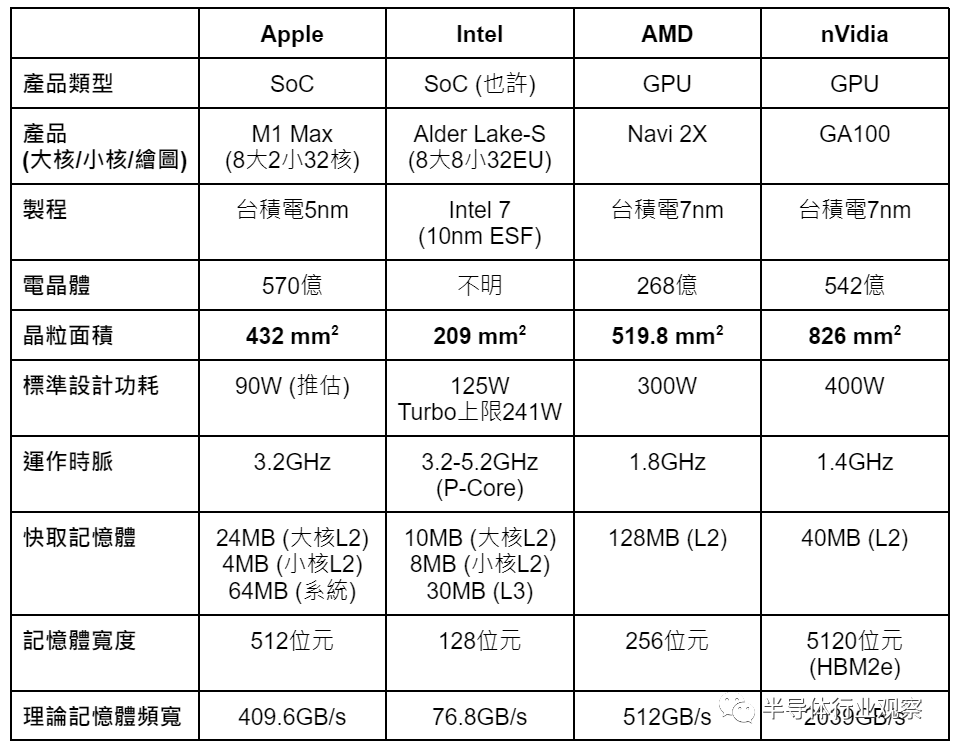

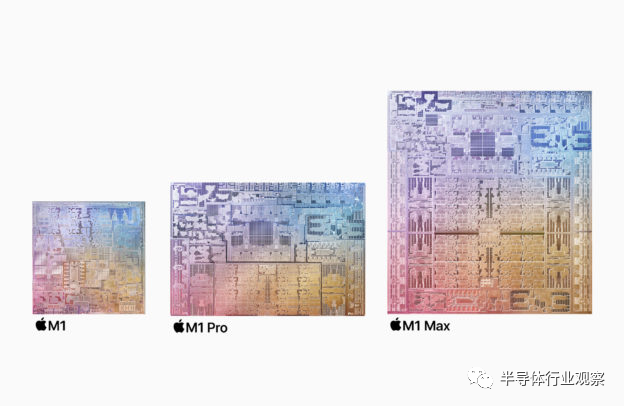

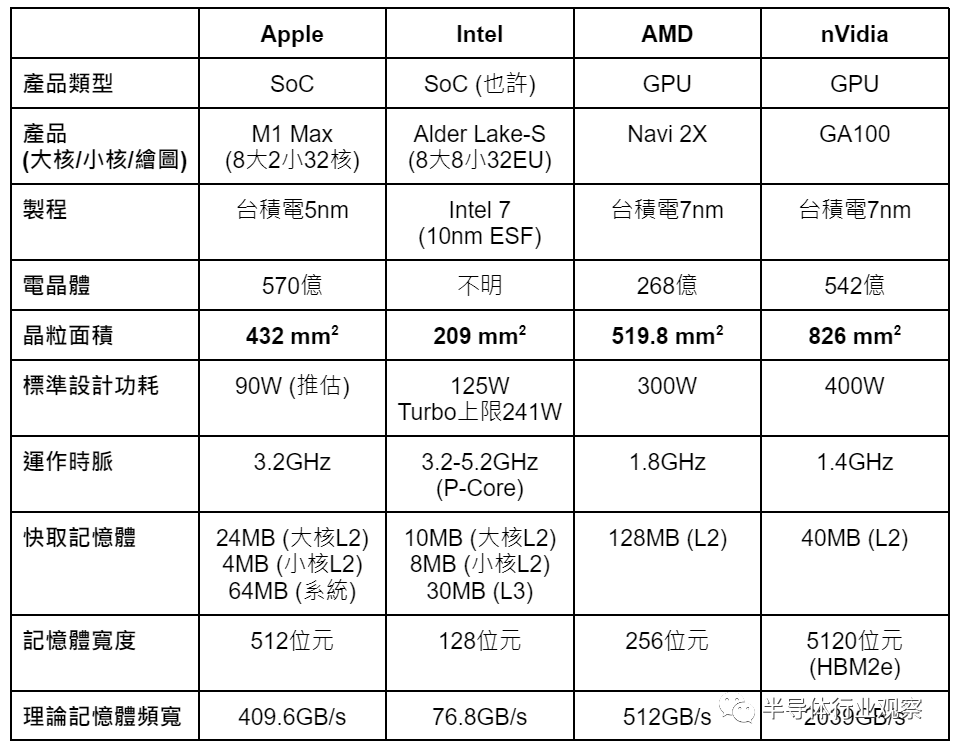

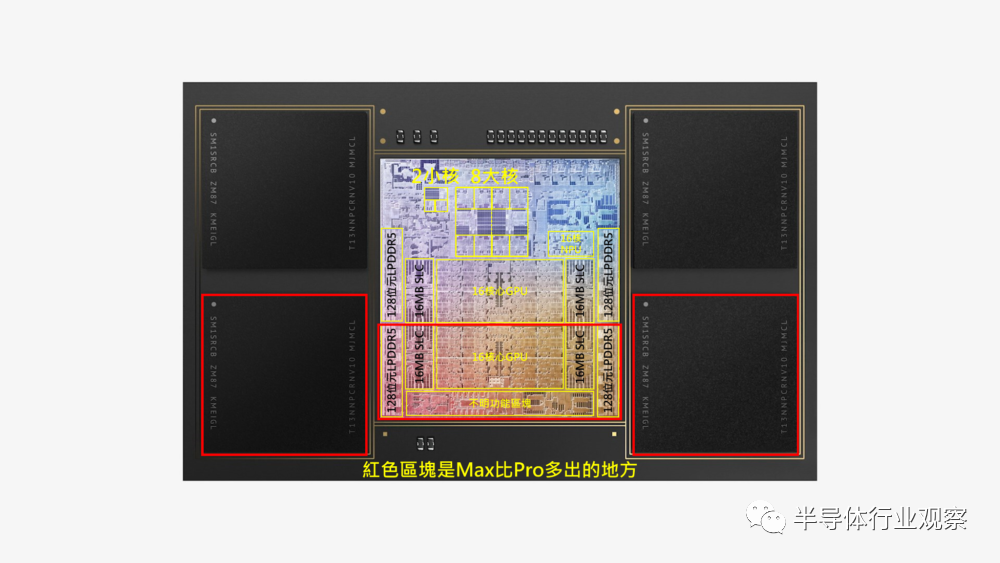

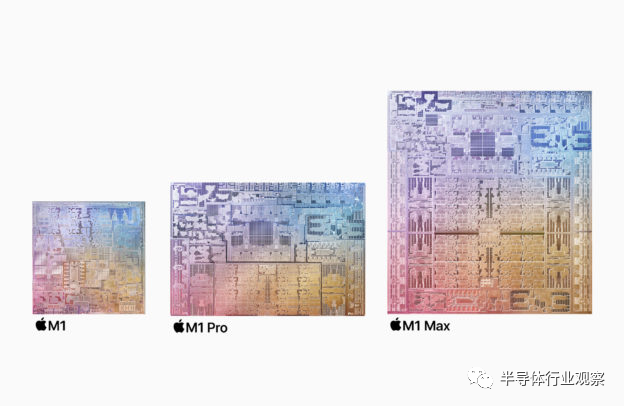

基于不同产品发展策略和客户需求,AMD走向小芯片Chiplet大玩「包水饺」,苹果却走向截然不同的单一巨无霸芯片:苹果M1 Max在432平方公厘面积内,塞了多达570亿晶体管,而标准设计功耗依据外界预估,却仅区区90W。

这是一个怎样的概念?直接比较一下英特尔、AMD、Nvidia近期有确认晶粒面积的产品:

这里会特别提及运作时钟与记忆体宽度,主要是这两者都跟芯片面积息息相关,时钟越高、记忆体汇流排越宽,无论外部封装还是晶粒本身,都更不利缩小面积。

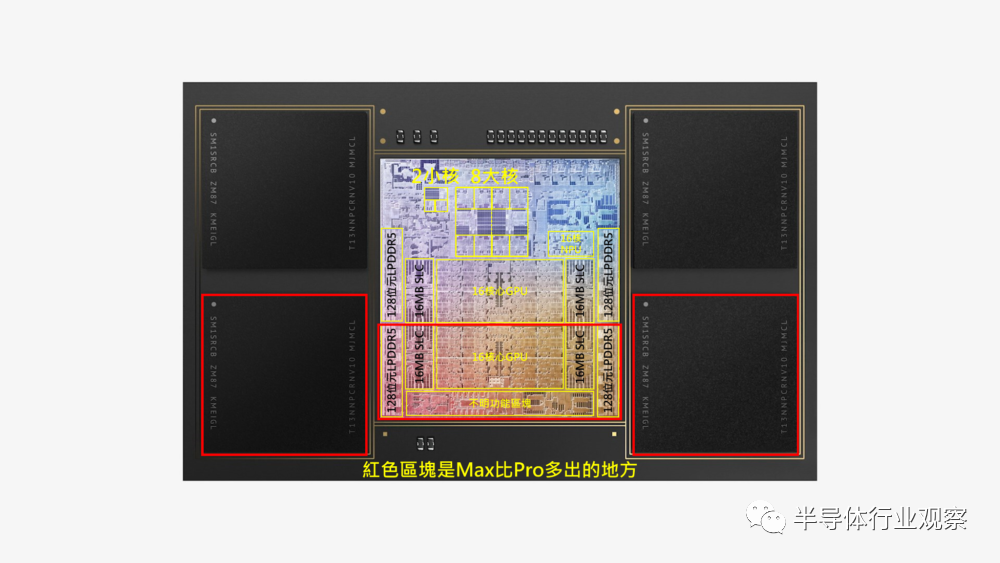

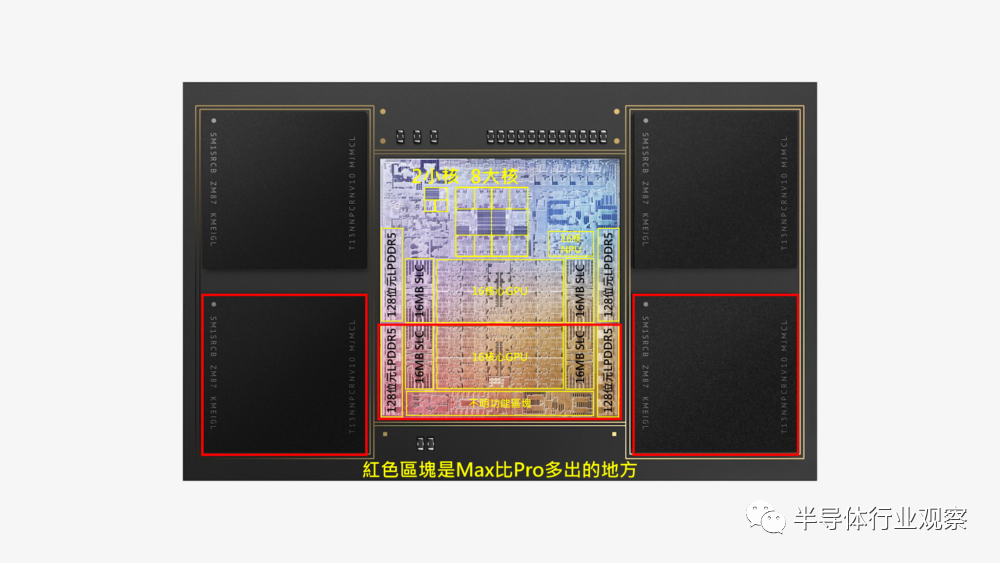

总之,据已知测试数据,M1 Max GPU的确展现足以匹敌AMD与Nvidia高阶GPU的潜力,无愧巨大的晶体管数量与「占地甚广」的GPU面积。请各位再复习一次M1 Max的功能单元布局,这里暗藏巨大的伏笔。

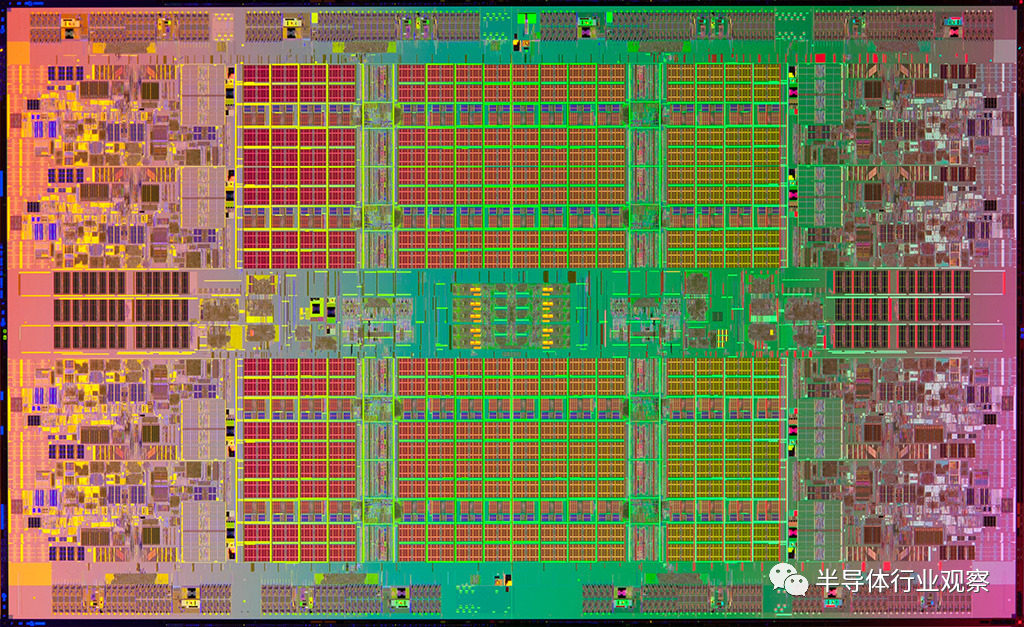

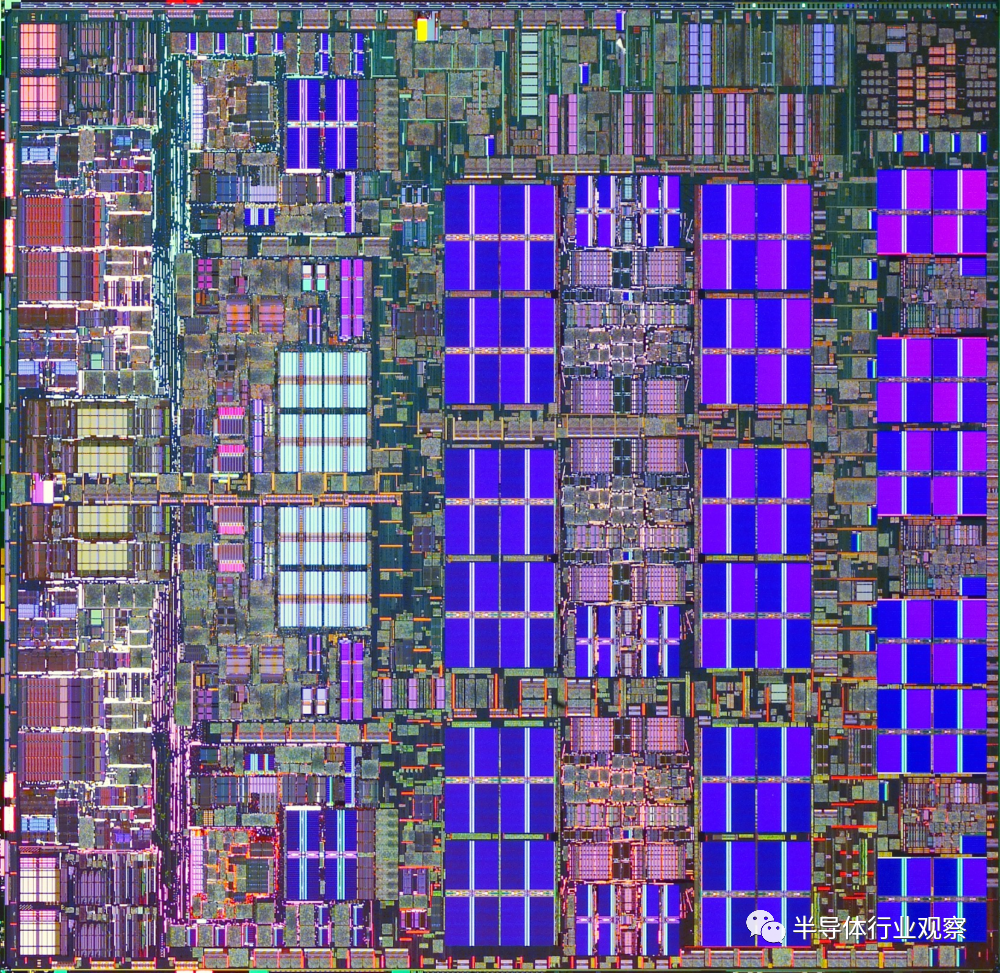

▲ 苹果M1 Max(面积432平方公厘,5纳米制程)。

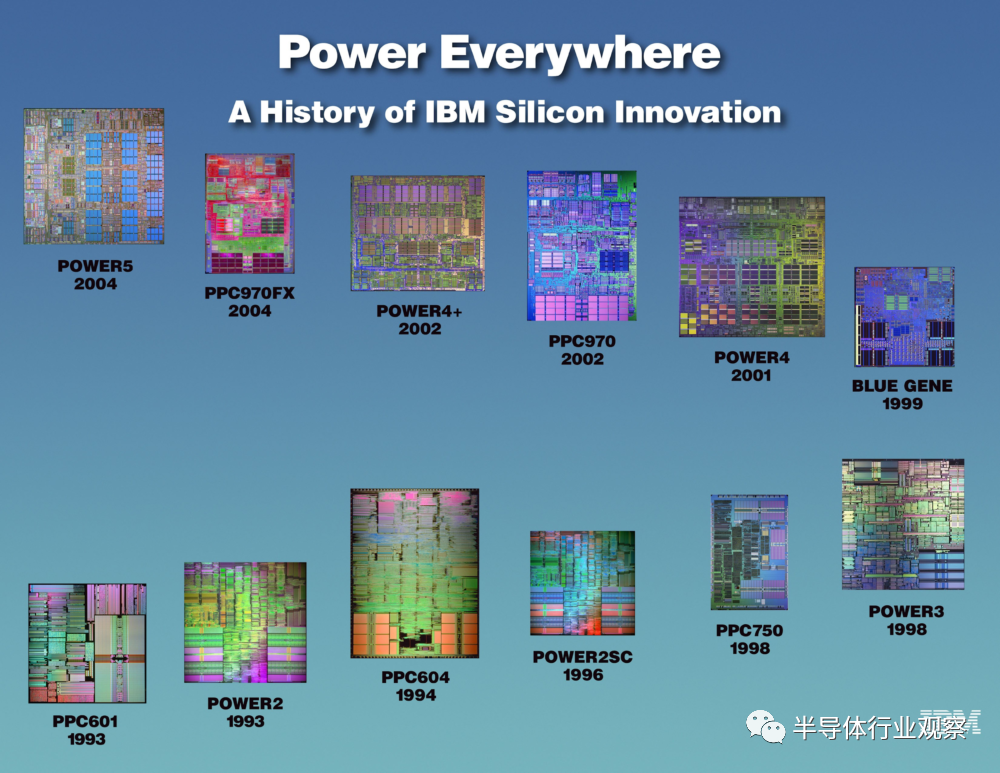

不过「恐龙化」处理器在计算机工业历史并非稀有物种,其实随处可见,让我们先从1990年代初期开始讲起,也请大家先把M1 Max的432平方公厘记在心里,接着改变心情,用逛美术馆的心态,慢慢欣赏这些半导体产业的高科技艺术品。

今天「一颗晶粒=起码一个处理器核心」似乎是常识中的常识,但很久以前不是如此。

距今超过30年前的古老年代,那时半导体制程和芯片设计工具都难以支撑巨大的单芯片处理器。日后被AMD并购的NexGen(K6起源),创业时首款386相容处理器,是「8颗」芯片产物。

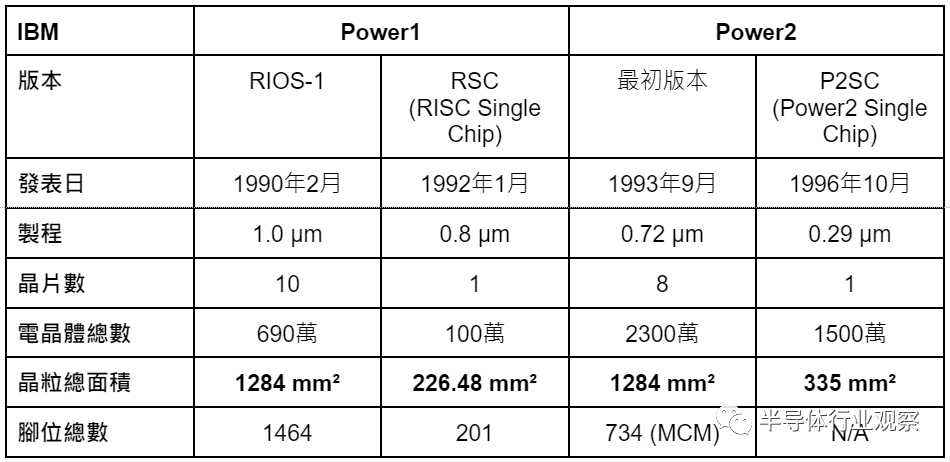

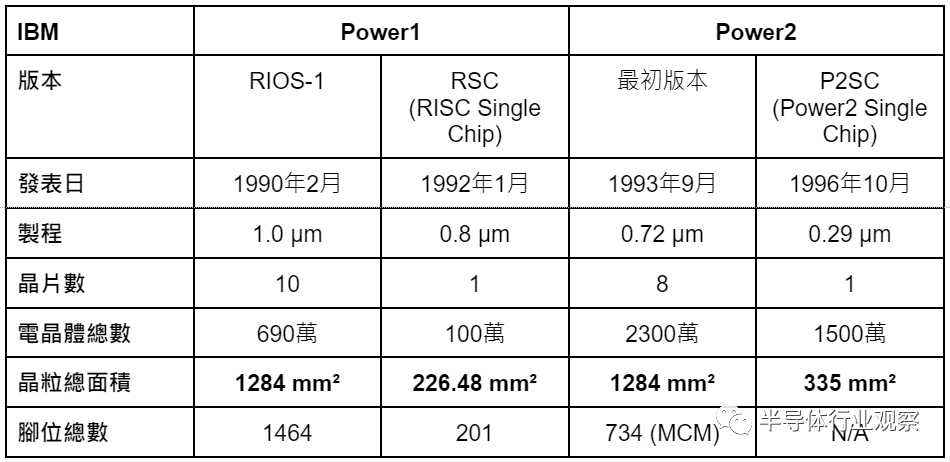

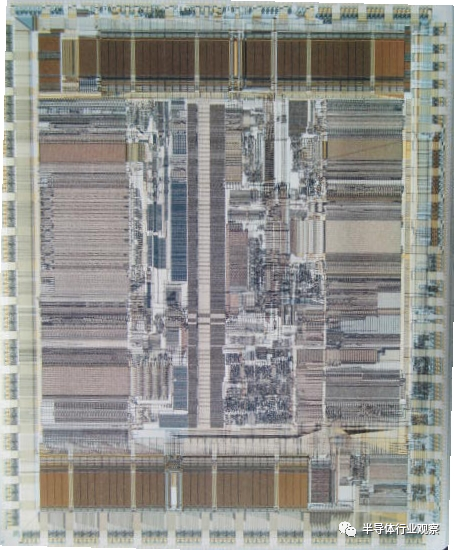

以IBM Power1初代RIOS-1为例,由「10颗」芯片构成,制程是1.0μm (相当于1千纳米),晶体管总数690万,晶粒面积总计1,284平方公厘,讯号脚位1,464只,后继Power2也是「8颗」芯片的怪物(0.72μm,2,300万晶体管,1,284平方公厘)。1992年1月RSC(RISC Single Chip),是IBM Power家族首颗单芯片实作(0.8μm,100万晶体管,226.48平方公厘,讯号脚位201只)。从以下这些不可思议的数字,尤其是做成多芯片浪费的晶体管和讯号脚位,就可了解能否设计成单芯片会这么重要。

▲ IBM Power1 RIOS-1(总面积1,284平方公厘,1.0μm制程)。

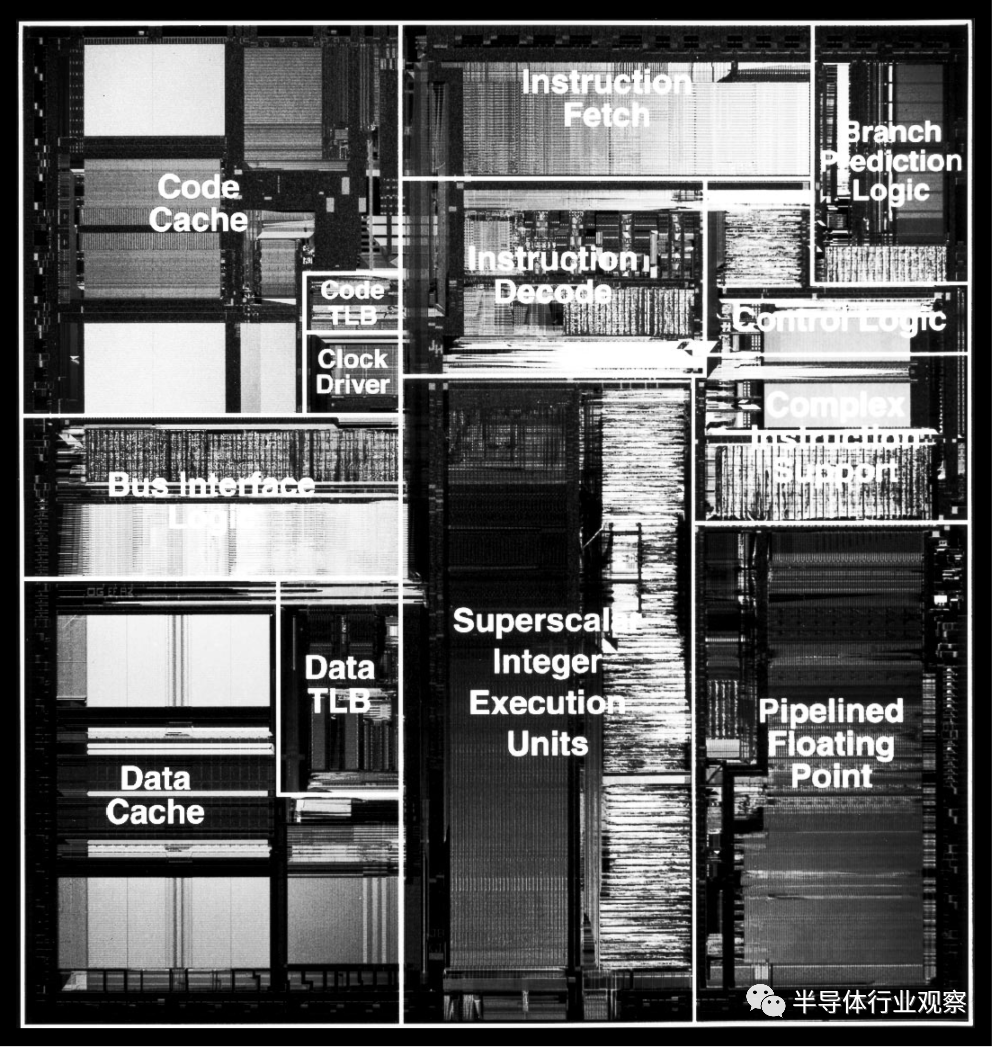

再回头看当时跟IBM Power2争夺效能王者的DEC Alpha。打从一开始Alpha就是单芯片,初代Alpha 21064(EV4)的晶粒面积只有233.52平方公厘(0.75μm,168万晶体管),后面又缩小至186平方公厘(0.675μm),时钟更上看200MHz,不难想见当时Alpha独领风骚的风光程度。

▲ DEC Alpha 21064(面积233.52平方公厘,0.75μm制程)。

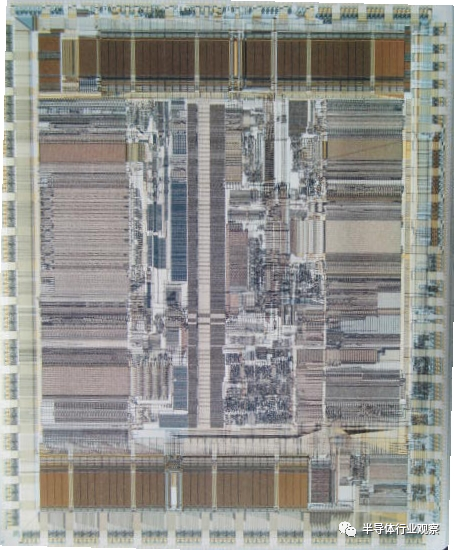

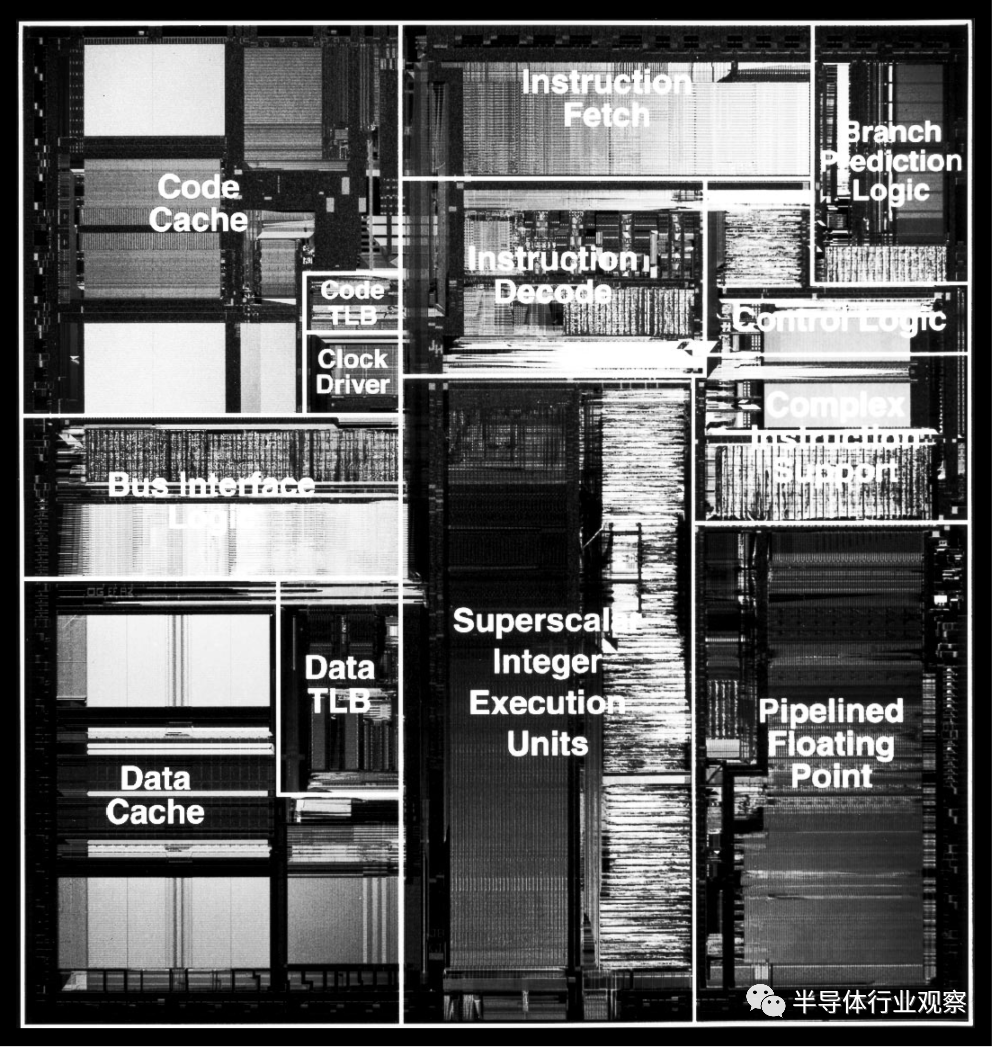

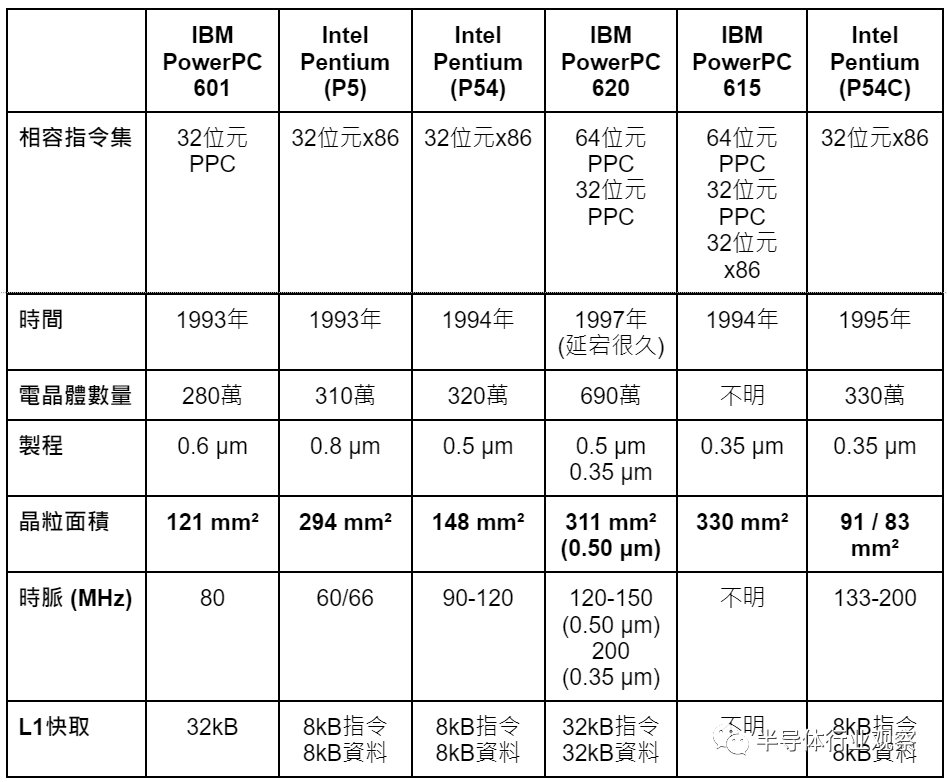

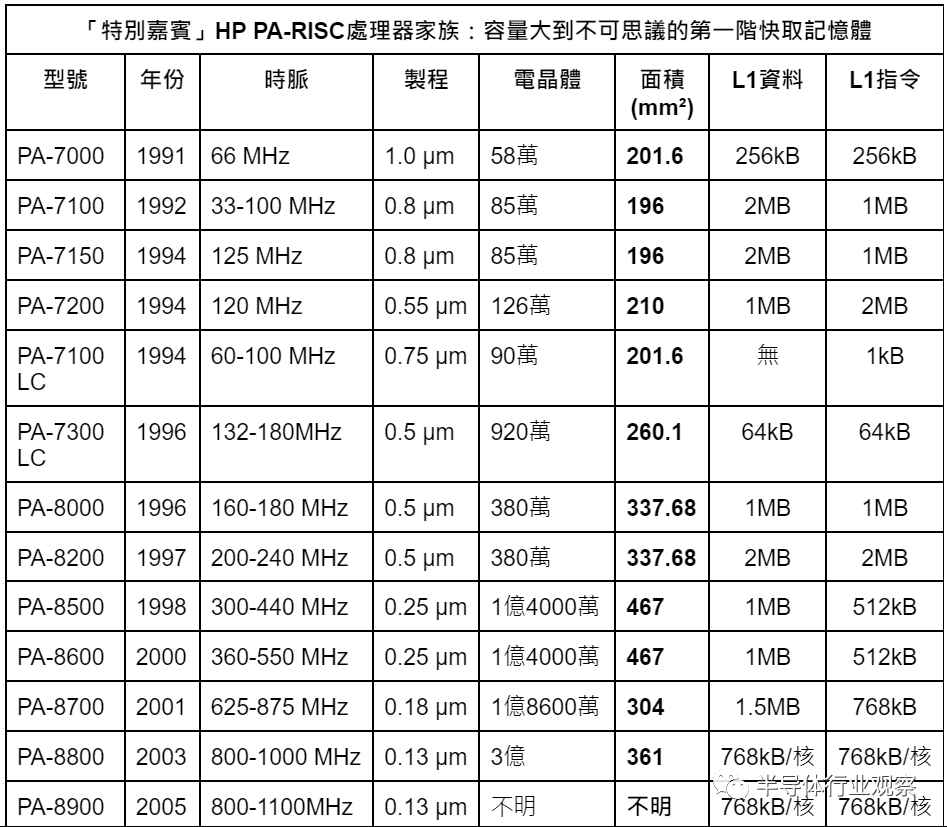

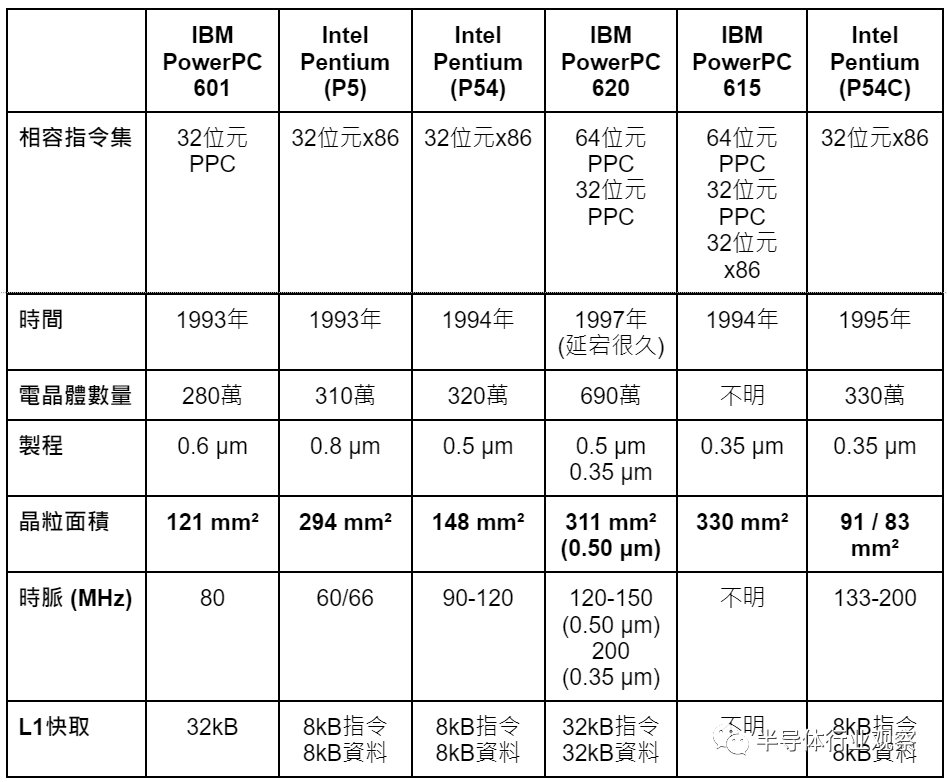

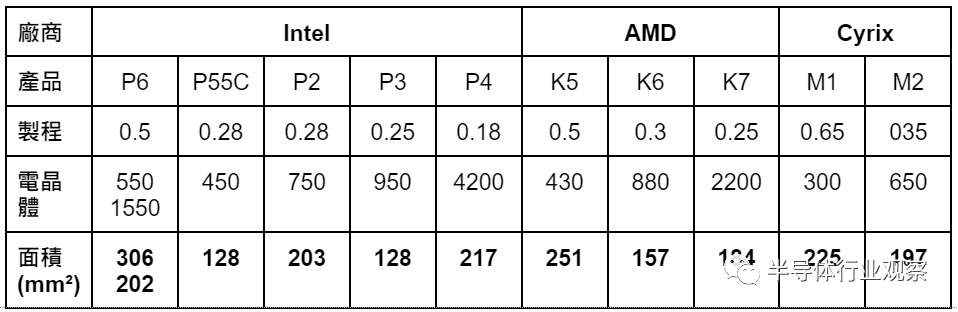

同场加映1990年代中期的个人电脑处理器,个人电脑市场因Windows 95作业系统急速成长的关键时刻,奠定「主流桌机处理器的晶粒面积约100平方公厘」标准。

可多少看出指令集架构复杂度和「毫无规则可寻的程度」,对晶体管数量和晶粒面积的影响。像PowerPC 601就比初代Pentium拥有更高时钟、1.5倍指令执行能力与两倍容量的L1快取记忆体。英特尔当时表示,相较同等级RISC处理器,Pentium有约30%晶体管都「贡献」给x86指令集的相容性,结果就反映至PowerPC 601两倍多晶粒面积(16.7×17.6mm=294平方公厘)。

▲ 英特尔初代Pentium(面积294平方公厘,0.80μm制程)。

爬文至此,相信眼尖的读者绝不会放过某颗看起来制程最先进、也最大颗的怪物:IBM PowerPC 615。

这颗处理器采用当时最先进的0.35μm制程(英特尔晚了IBM近一年),晶粒面积330平方公厘,同时支援64位元PowerPC、32位元PowerPC和当时还是32位元的x86指令集,并相容英特尔Pentium脚位(应是Socket 5)。最有意思的部分,在IBM是透过「硬塞」x86核心,直接实现相容性,摆明想将PowerPC推动x86处理器战场。

换句话说,这是历史第一个完全出于IBM之手的x86核心微架构。曾出现原型样品的PowerPC 615是可怕的巨无霸芯片,IBM宣称「一人吃,两人补」看起来不像喊假的,晶体管数量粗估突破1千万。IBM至今尚未公布晶粒图,实在很可惜。

很不幸的是,微软拒绝支援这颗神奇的混血妖怪,也导致对应的作业系统,只有特化版MINIX(传说中Linux前身) 和自家OS/2。或许也考量到PowerPC 615价格与耗电量将高不可攀,主机板相容性也很可能是一大问号,IBM索性放弃PowerPC 615,让世人无缘见识IBM亲手打造的x86处理器核心究竟有多厉害。但论「巨无霸」桌机处理器,就不得不谈谈从未正式量产的Cyrix 6×86 ″M1″初期试产版,比PowerPC 615还夸张,但主因并非太多晶体管,而是制程严重落后才使其如此臃肿。

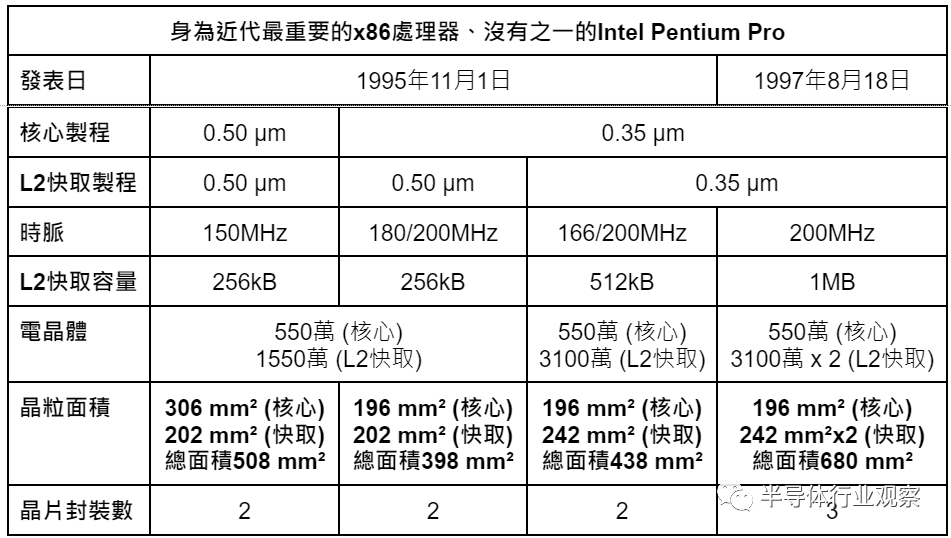

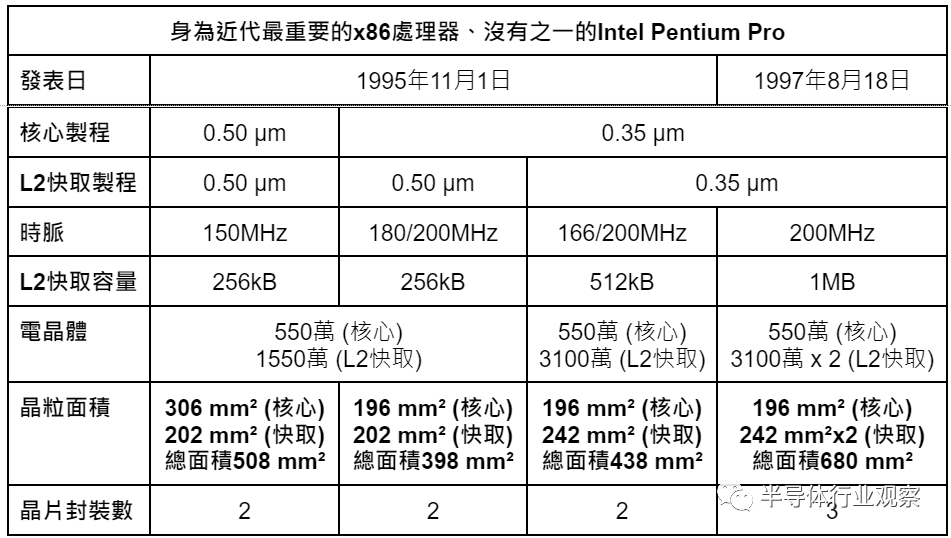

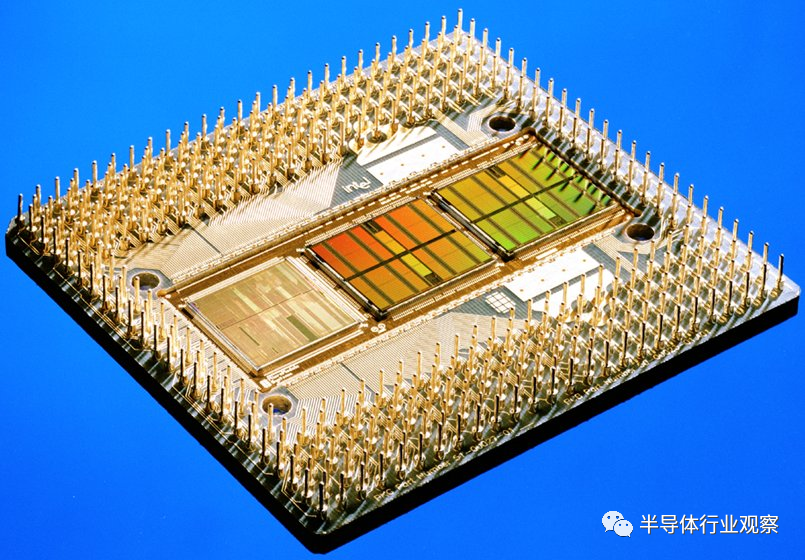

今日一提到「大芯片」,一般人会马上想到的,不外乎高阶伺服器处理器或旗舰级GPU。1995年11月1日和世人正式见面的英特尔Pentium Pro,不仅替x86敲开伺服器天堂大门,更替RISC诸神敲响黄昏丧钟。

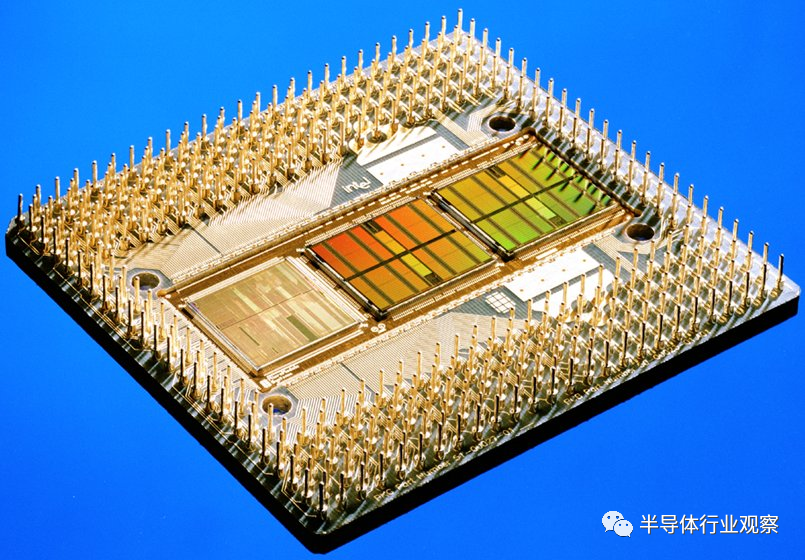

Pentium Pro采用多芯片封装(MCM,Multi-Chip Module),包含一颗处理器核心与第二阶快取记忆体,分别用不同制程的核心与快取,配出六种产品规格,也理所当然是当时最高档也最先进的x86处理器,心脏P6微架构也让英特尔维持近四年的技术优势。

▲ 英特尔Pentium Pro 1MB L2(总面积680平方公厘,0.35μm制程)。

觉得英特尔Pentium Pro不够大颗?就得搬出Cyrix 6×86「M1」了,最初量产前测试版竟多达394平方公厘(0.65μm,三层金属导线),比初代Pentium还大,预估制造成本高达340美元,根本就贵到保证亏钱,所以实际上市的量产版改成五层导线的IBM CMOS-5S制程(同PowerPC 620),才缩小到225平方公厘,但还是比英特尔AMD同期产品肥许多,也意味更低的利润。

总而言之,随着个人电脑市场的快速发展与对低价电脑的需求,所有x86处理器厂商在20世纪末期,都很严格控制芯片「体重」,唯一例外是整合2MB第二阶快取、面积385平方公厘的英特尔Pentium III Xeon「Cascade 2M」。对x86处理器发展史和英特尔自己,这颗都意义重大,建立起「英特尔(与其他处理器厂商)的最重要业务,不是生产处理器核心,而是快取记忆体」的刻板印象。

▲ 英特尔Pentium III Xeon「Cascade 2M」

(面积385平方公厘,0.18μm制程)。

顺便一题,AMD在K7时期曾计画推出内建2MB第二阶快取的Mustang(野马),目标也是伺服器市场,但因K8即将到来而取消,否则也很可能是颗不小的芯片。

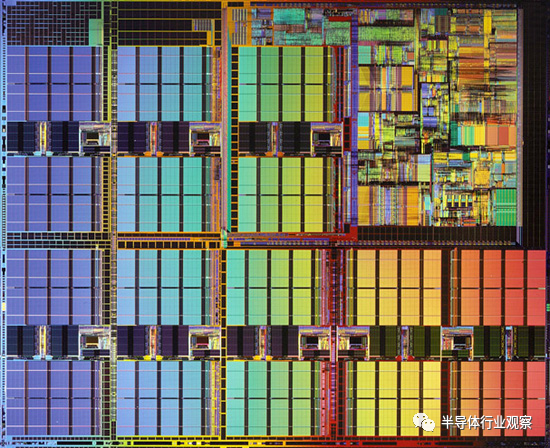

再瞧瞧20世纪末期的主流x86处理器厂商「御三家」,「空照图」最显眼的那颗,皆为同系列的第一版。

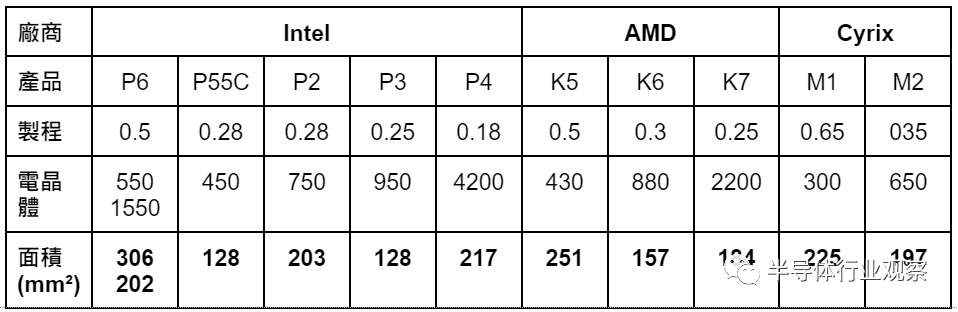

不可思议的巨大L1快取记忆体:HP PA-RISC家族

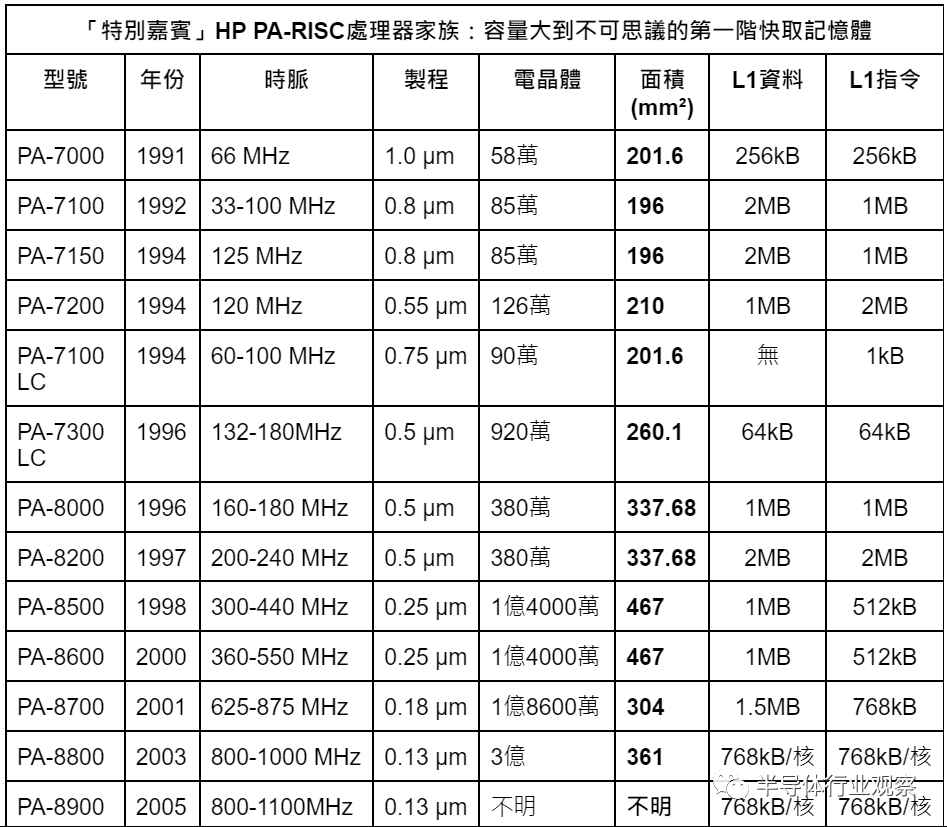

说到1990年代高阶伺服器市场叱咤风云的「RISC诸神」(IBM Power、Sun / Fujitsu SPARC、DEC Alpha、SGI MIPS、HP PA-RISC),最不出风头的HP PA-RISC,容量大到不可思议的第一阶快取记忆体,值得特别拿出来跟各位分享。

1991年PA-7000就内建分别多达256kB的第一阶指令与资料快取,1992年PA-7100更是惊世骇俗的「1MB指令和2MB资料」,把第一阶当成第二阶甚至第三阶来做,后继家族成员几乎都如法炮制。

照理说,越接近处理器运算核心的快取,须尽其所能缩短延迟,所以容量不能太大,让多层快取记忆体形同某座「金字塔」,不禁让人不得不好奇HP的考量点,难道HP-UX作业系统常用的应用程式,是只要一碰到系统主记忆体,效能就会马上火烧摩天楼的那种?

▲ HP PA-7100 (面积196平方公厘,0.8μm制程)。

被Itanium「不彻底取代」的HP PA-RISC家族,除了很神奇的PA-7100LC(没有L1资料,L1指令只有1kB,完全靠外部L2)和整合8MB L2的PA-7300LC,清一色都是超大型L1的诡异存在,晶粒面积也略大于同期的「RISC同侪」。但这和踏入21世纪后的「恐龙」相比,还是完全小巫见大巫。

就让我们再次回顾20世纪末期的RISC诸神家族最大那颗。当然,这里只挑单晶粒产品。各位也能从比较表感受到不同厂商「底力」的差距。

但英特尔与HP联手开发IA-64指令集与Itanium处理器,企图一统RISC与高阶伺服器江山,却意外引爆21世纪初期「巨兽化」。如果你是钢弹迷,说当时是「宇宙世纪0087」,或听过什么是ZZ Gundam还是S Gundam,大概也猜得到笔者想表达的意思了。真糟糕,这年头写个专栏还会不小心暴露大家的年纪。

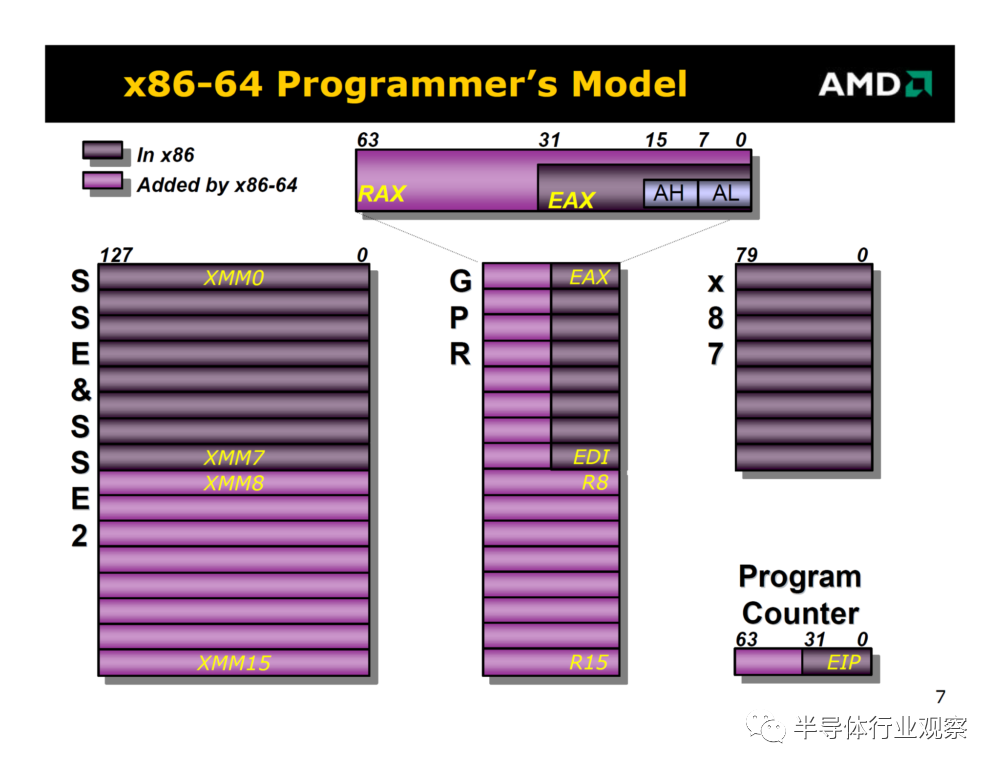

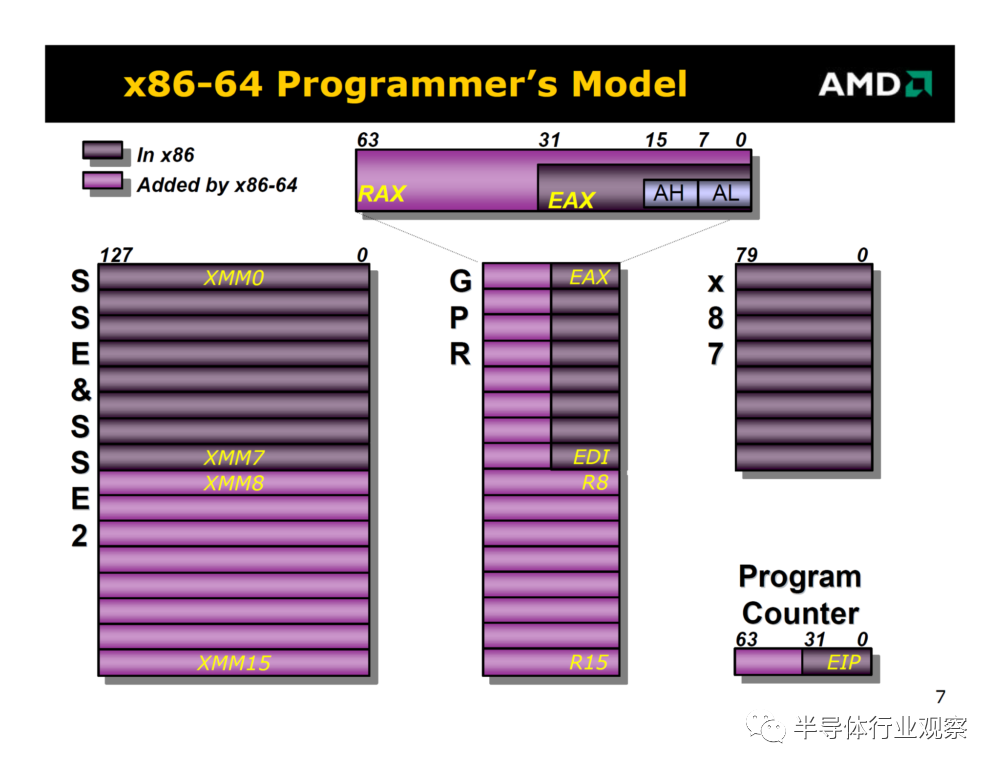

如果说引起第一次世界大战的背后因素来自工业革命影响,那21世纪初期引爆巨大化泛用处理器的根源,就是64位普及了。1990年代,64位清一色都是RISC诸神的专利,也成为x86难以越过的天险。

你也许会觉得纳闷:64位跟CPU肥大化根本八竿子打不着,但假若有某间「半导体业界第一大厂」想趁机打垮「RISC诸神」,一口气吃下所有高阶伺服器市场,企图仰仗快取记忆体的技术优势,歼灭所有竞争对手,那又是另一回事。

微软暗助下,AMD推动x86-64更逼出英特尔的底力,不管IA-64指令集的Itanium和x86指令集的Xeon,英特尔陆续创造无数仿佛「快取记忆体不用钱」的世界奇观,让晶粒面积突然一飞冲天,令人叹为观止。

最后,这艘载满众多放弃自有研制处理器伺服器大厂的观光邮轮还是沉没了,还拖Alpha、PA-RISC与MIPS一同殉情,只留下超大型快取记忆体的经验,让英特尔x86处理器继续发扬光大到今天。

指令集为电脑「语言」,软件与硬件间的介面,众所皆知,80×86是很糟糕的设计,不限于撰写教科书的计算机结构大师和众多竞争者的批评,连创造80×86的生父英特尔也不很欣赏这先天不足又后天失调的子嗣。1980年代如雨后春笋一个个钻出泥土的RISC(精简指令集电脑)和企图将复杂度从硬件转移到软件的VLIW(超长指令集),风潮也影响到渴望进军伺服器市场的英特尔。

并购1980年代VLIW技术先驱Multiflow和Cydrome的HP,1989年启动VLIW化PA-RISC指令集(没错,就是前面提到那票L1快取大到夸张的家族)研发案,1994年和英特尔一拍既合,目标取代x86的IA-64指令集与相对应的Itanium处理器,就此展开。

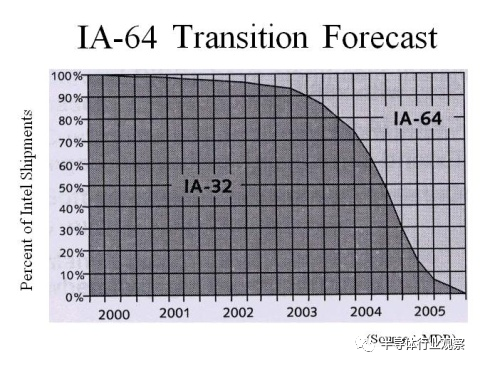

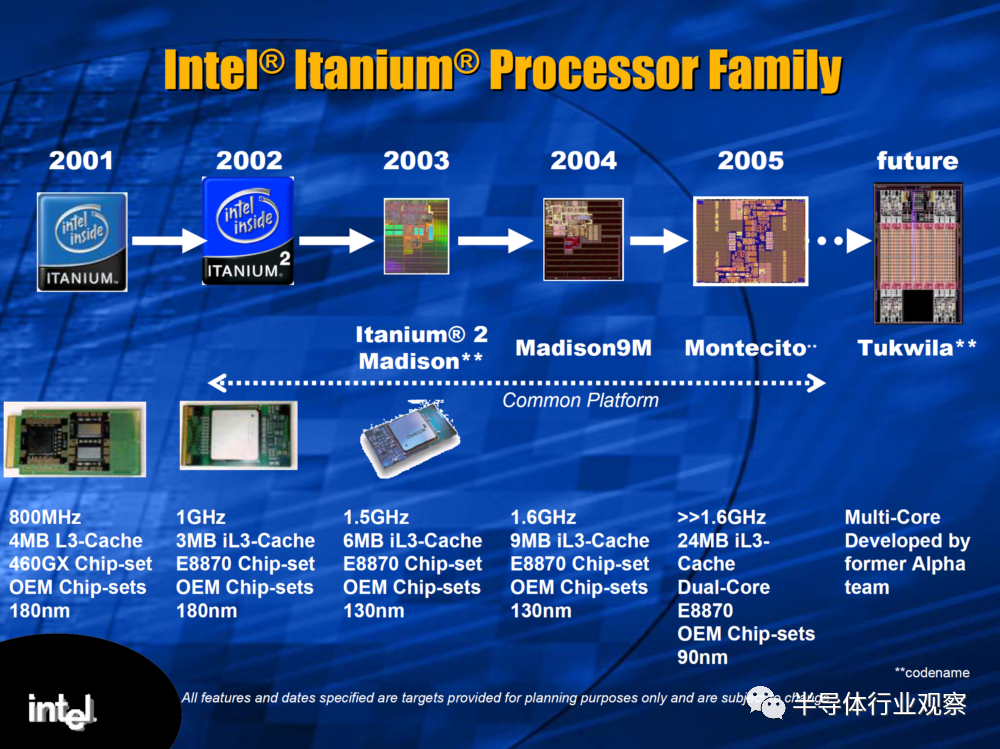

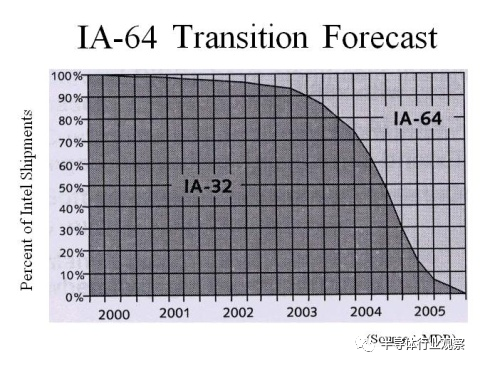

以下就是英特尔对IA-64的原始期待:不只在2002年,就在伺服器市场横扫所有RISC家族、市场规模达300亿美元,更要进入桌上型市场,2005年就彻底取代80×86。现在看来不可思议,当时却着毋庸议,不可质疑。世人普遍看好英特尔的原因也很简单:相比其他厂商,英特尔更有充沛的研发资源稳定推出新产品。

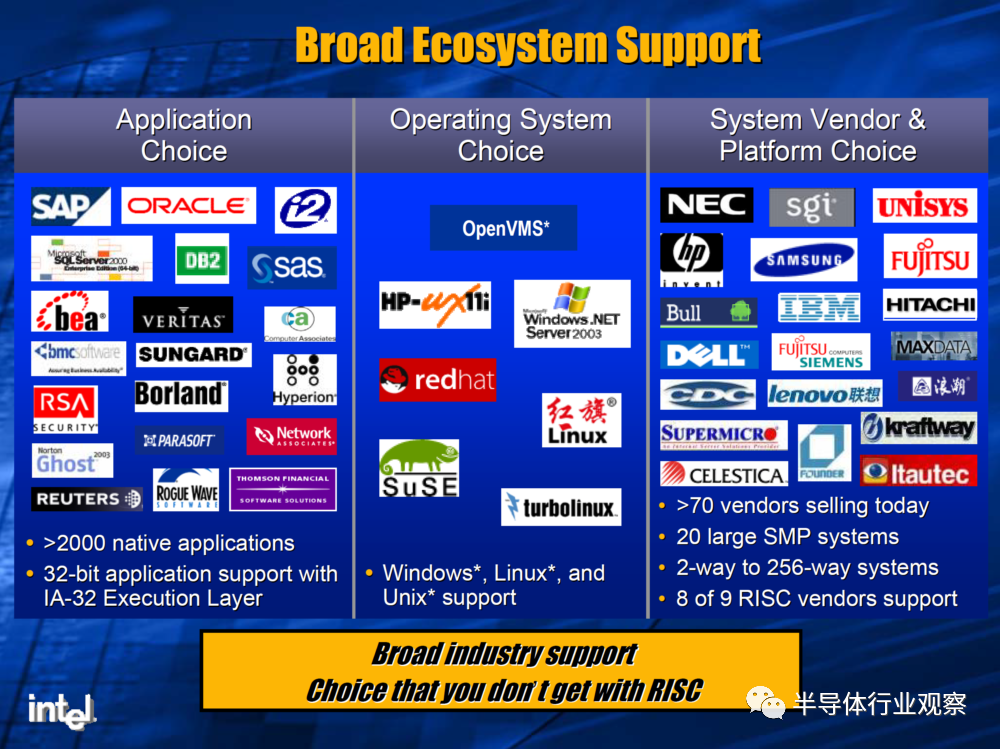

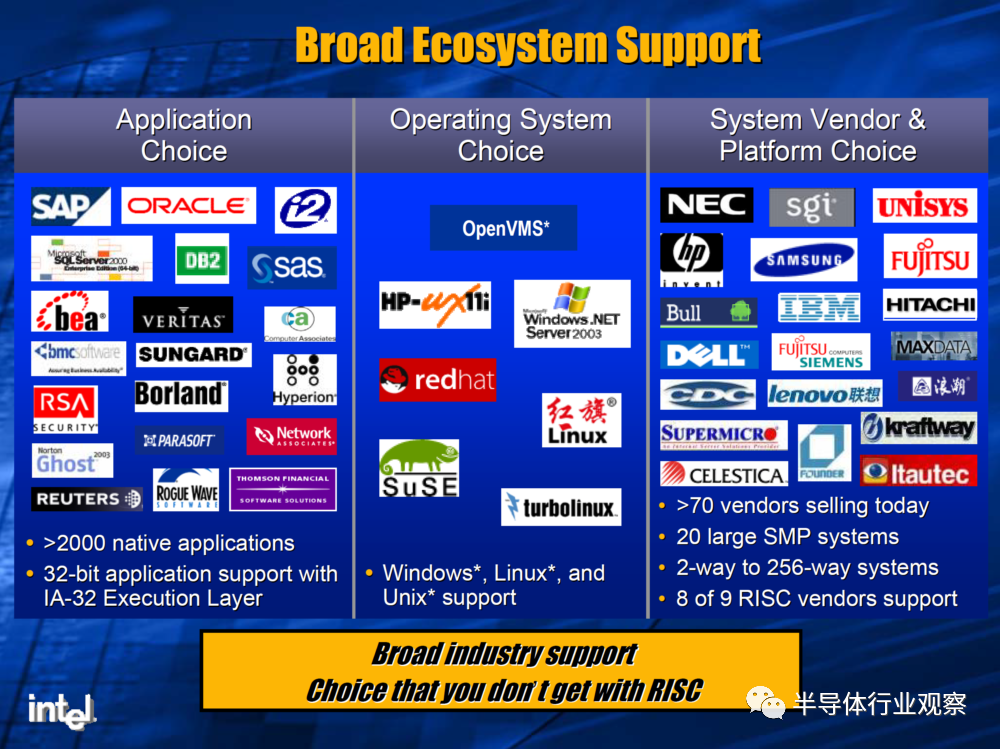

Itanium先以高阶伺服器为市场切入点,英特尔理所当然找来一堆人帮忙站台造势,且宣称享有比当时RISC体系(MIPS、Alpha、SPARC、PA-RISC、Power) 更广泛的业界支援。

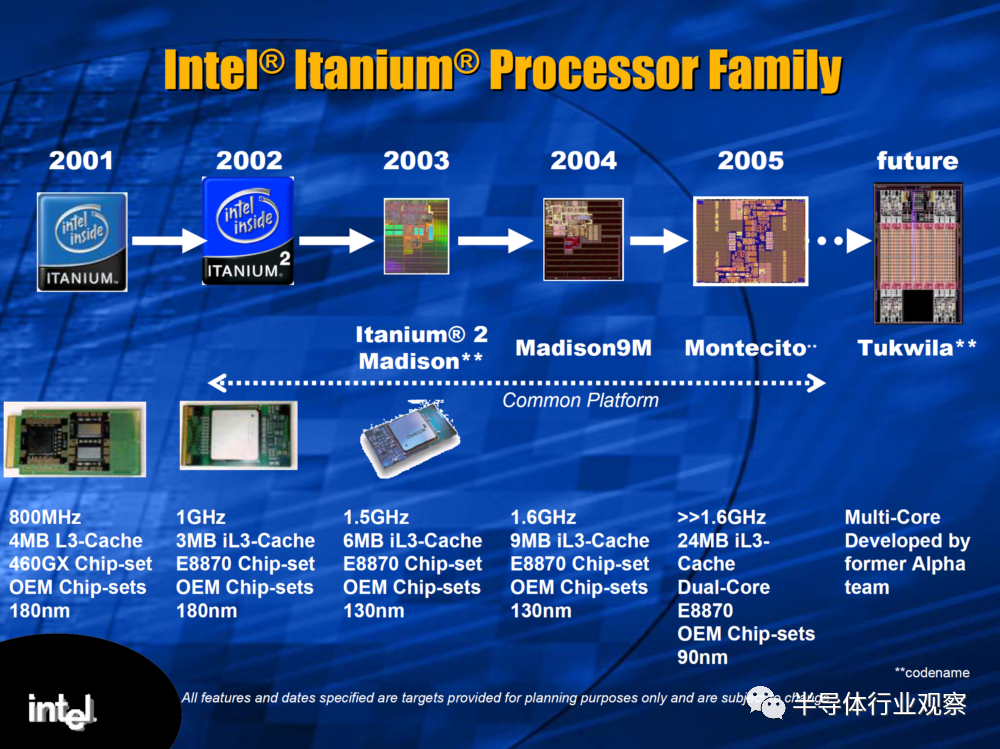

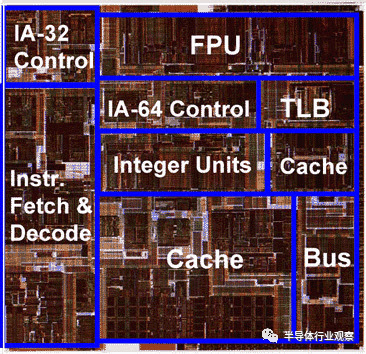

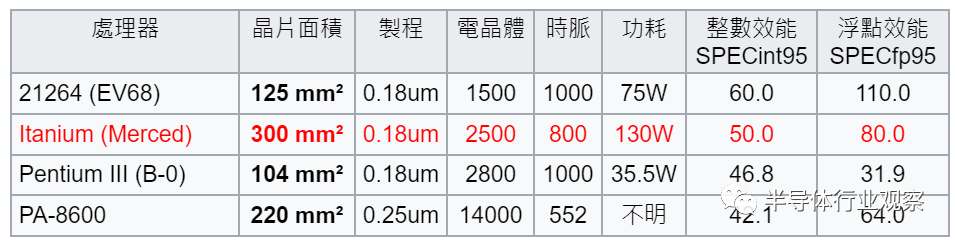

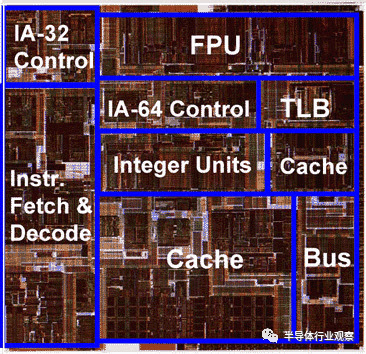

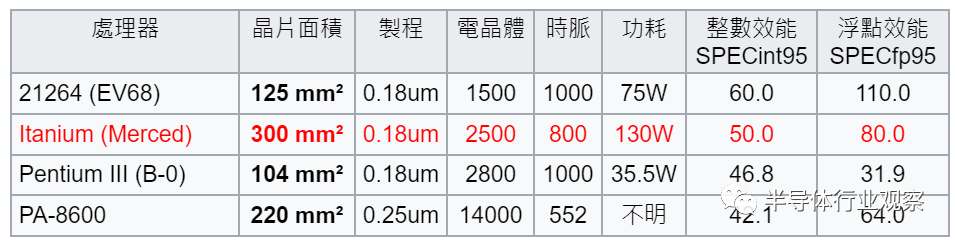

但预定1998年上市的初代Itanium处理器「Merced」,却因英特尔与HP合作模式的种种问题(为了保密而在办公室设「隔离防火墙」之类),拖延至2001年才出现。光从失控的芯片面积和耗电量,各位就可轻易看出此专案失控的程度有多严重。更讽刺的是,操刀Merced设计的团队,还位于英特尔加州Santa Clara总部。

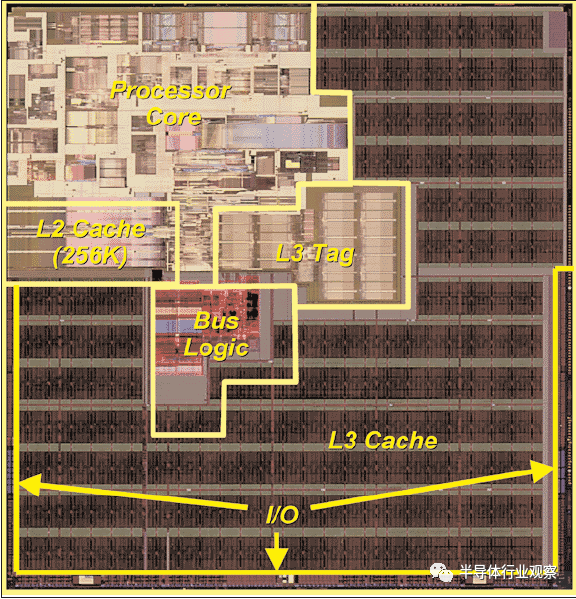

▲ 英特尔Itanium「Merced」(面积300平方公厘,180纳米制程,4MB第三阶快取记忆体)。

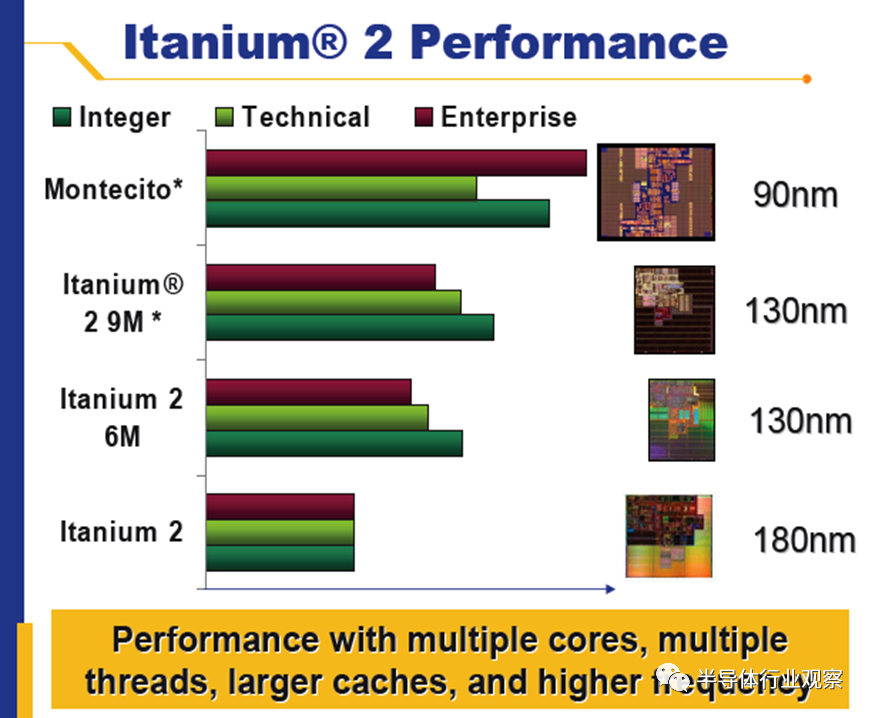

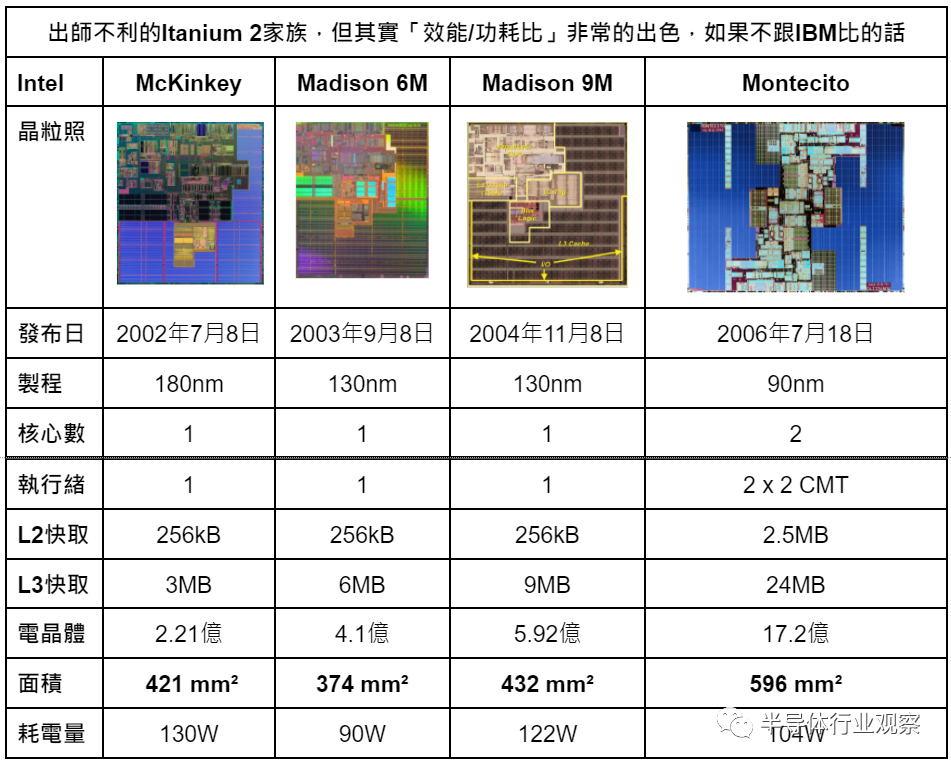

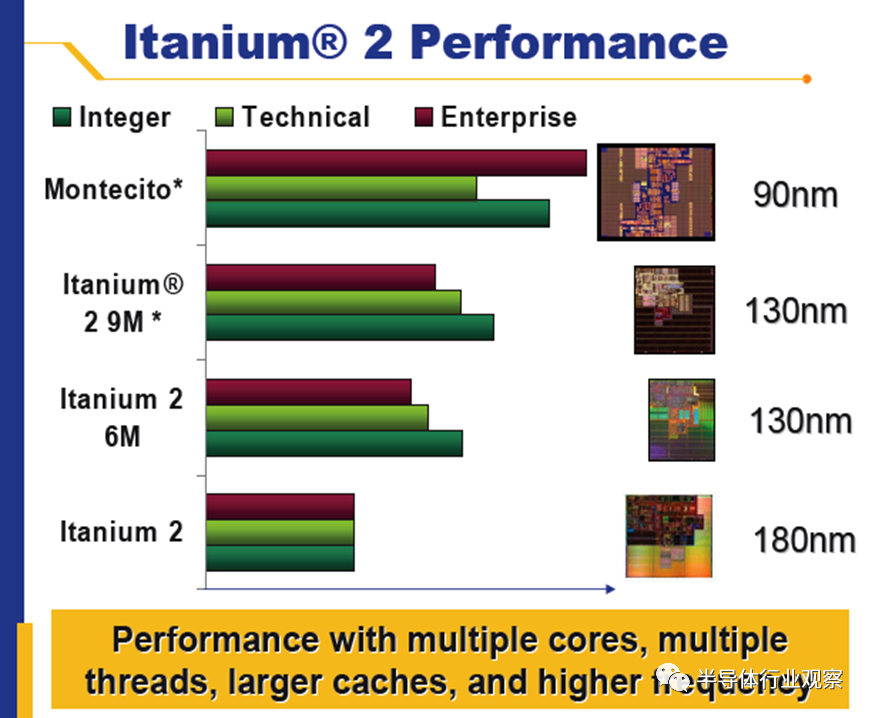

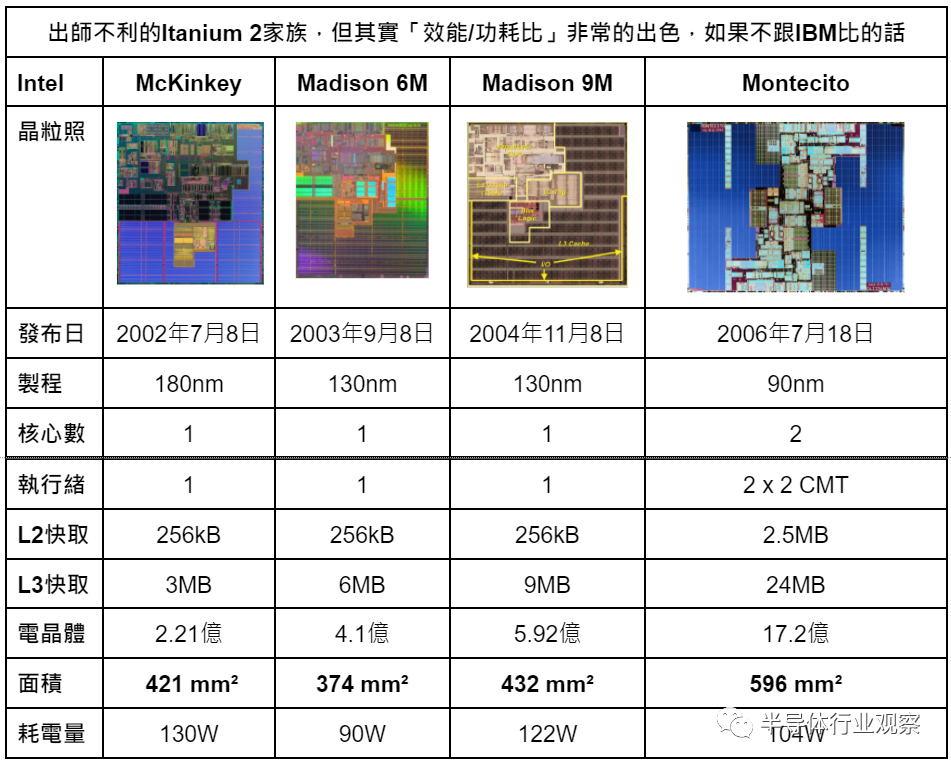

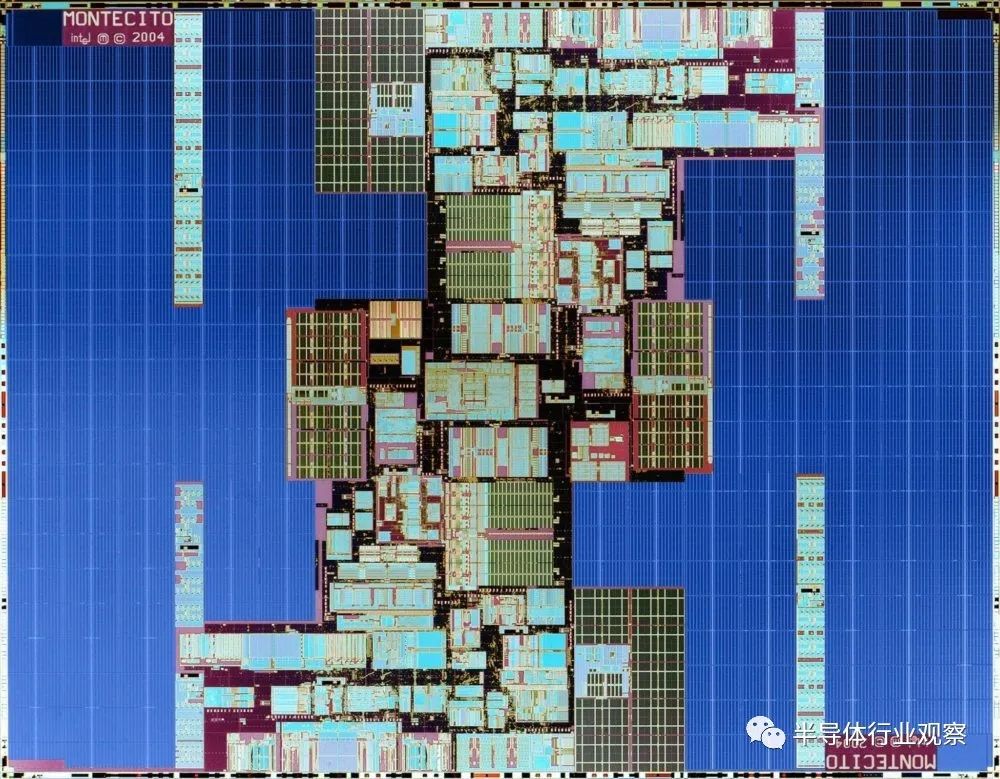

Itanium随即被外界揶揄为「Itanic」,比喻为当年撞上冰山沉没的Titanic邮轮,直到2002年,前HP团队负责的Itanium 2才勉强站稳脚跟,原订2005年却延误到2006年的双核心Itanium 2「Montecito」,让英特尔寄以厚望的旗舰处理器,总算有勉强跟当时王者IBM Power5+一拼的能耐。

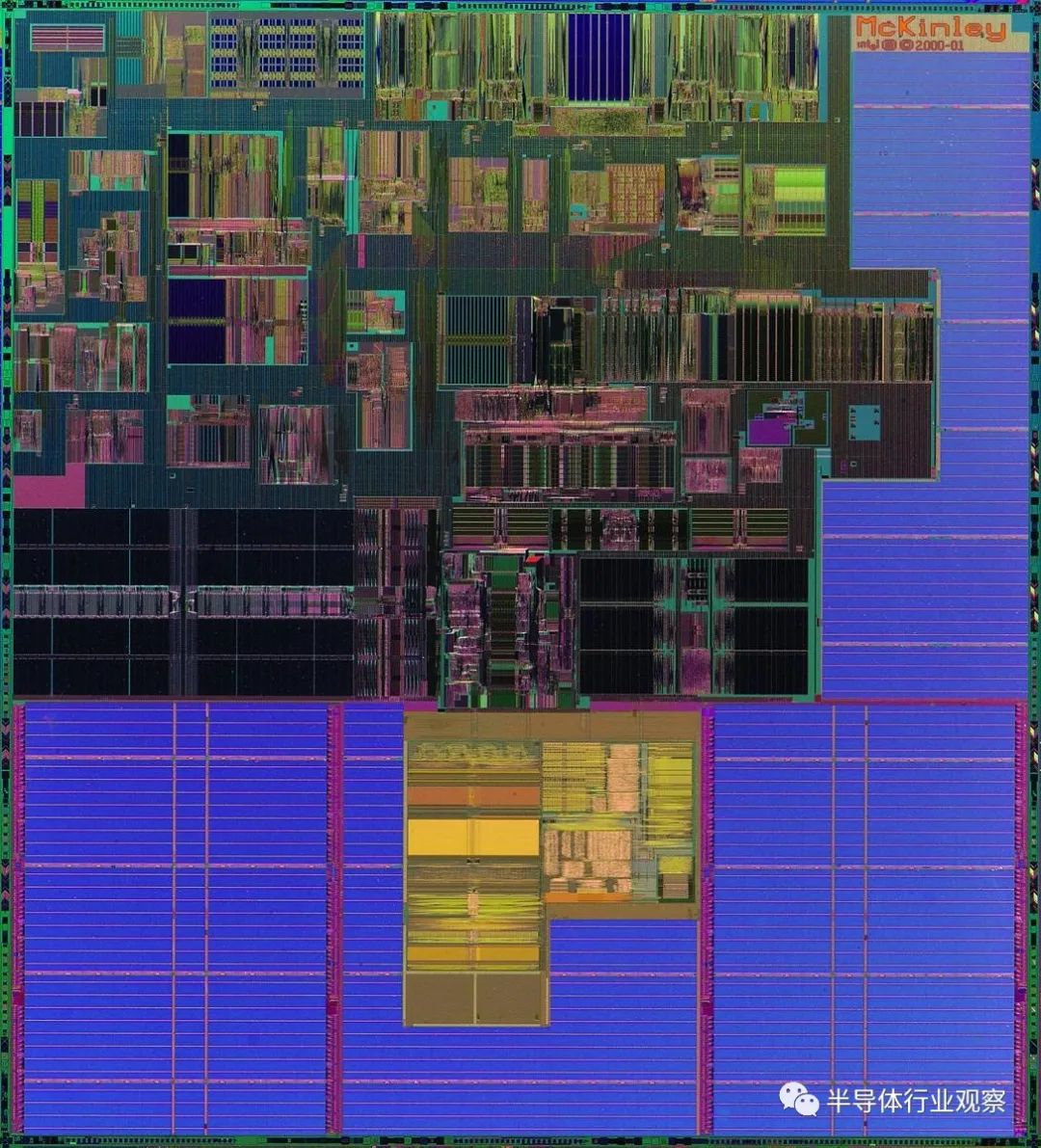

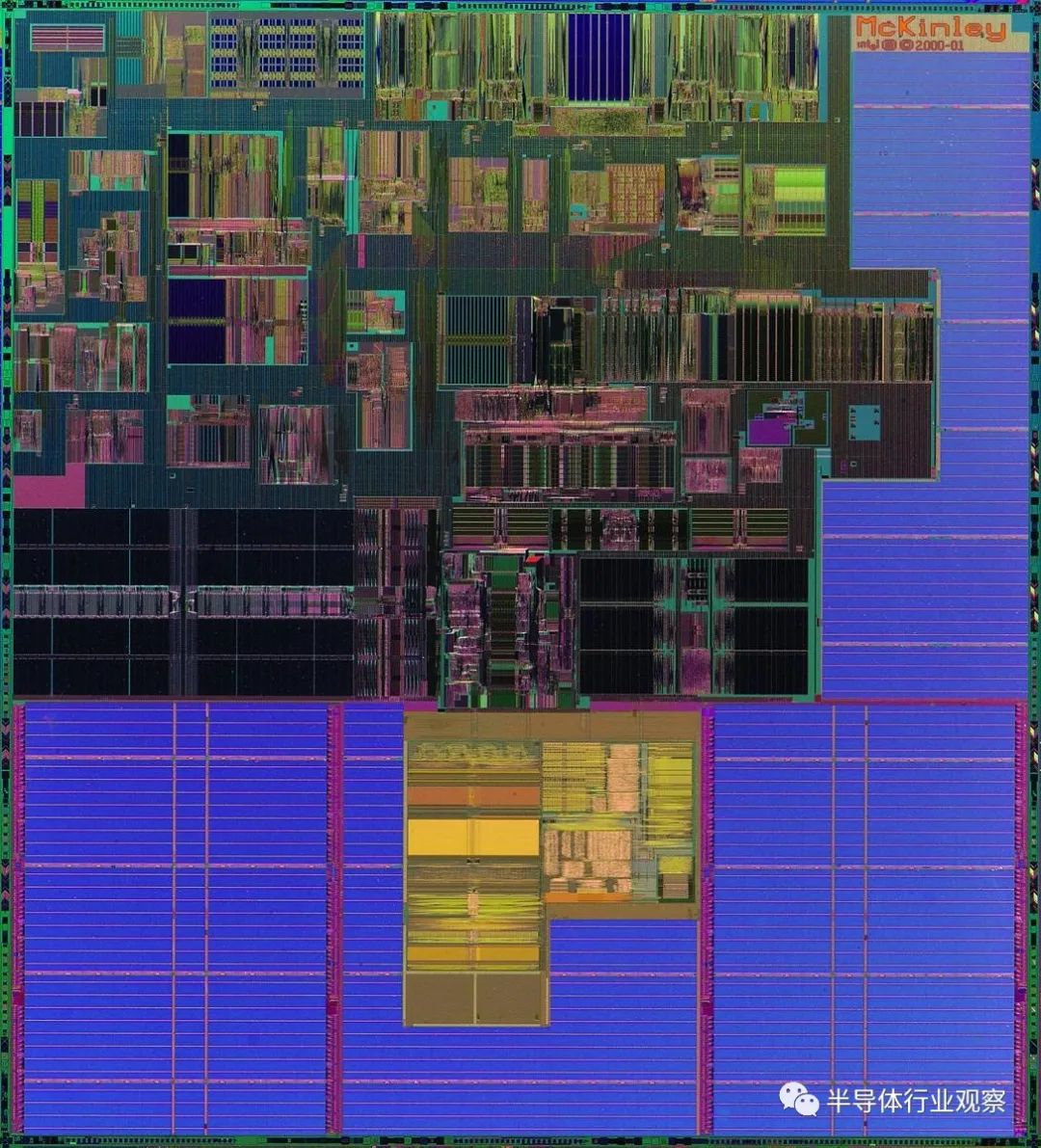

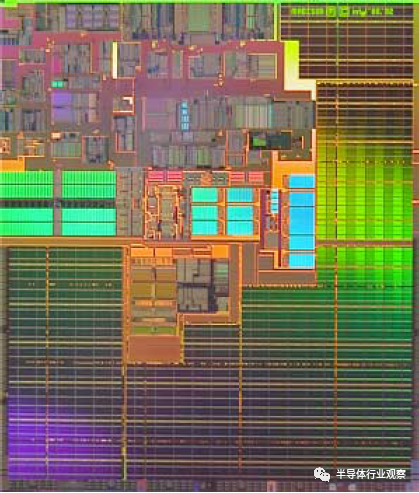

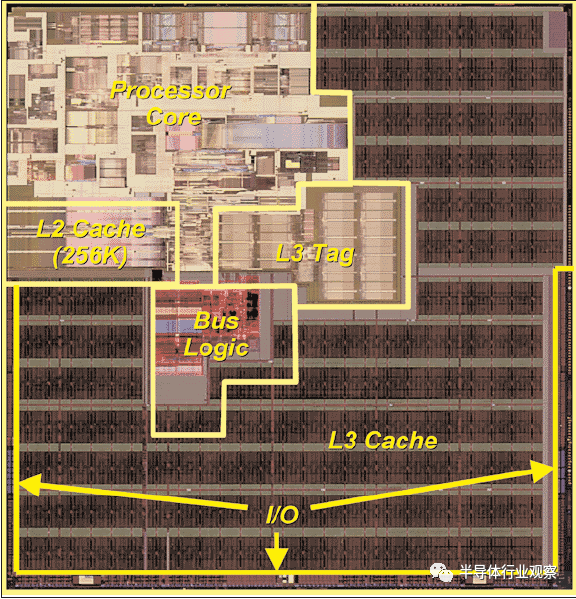

但Itanium处理器需要特别大的快取记忆体,并非单纯要「善用晶圆空间」,而是IA-64指令集的诸多特性,使程式码体积是x86指令集3.7~4.8倍,意味需要更巨大的记忆体频宽,快取记忆体的容量就对提升效能颇具立竿见影之效。以「实际算第一个上市产品」的Itanium 2「McKinley」来说,就包含3MB的第三阶快取记忆体。

▲ Itanium 2「McKinley」(面积421平方公厘,180纳米制程,3MB第三阶快取记忆体)。

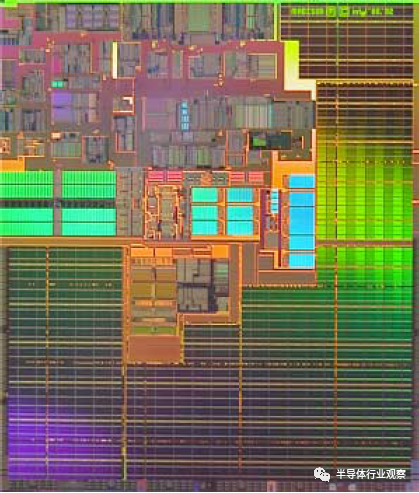

这还不打紧,英特尔和HP继续再接再厉,130纳米制程微缩款Madison 6M加倍到6MB。

▲ Itanium 2「Madison 6M」(面积374平方公厘,130纳米制程,6MB第三阶快取记忆体)。

英特尔和HP并未停下脚步,很快又推出容量增加50%的Madison 9M,面积「重回」400平方公厘水准。

▲ Itanium 2「Madison 9M」(面积432平方公厘,130纳米制程,9MB第三阶快取记忆体)。

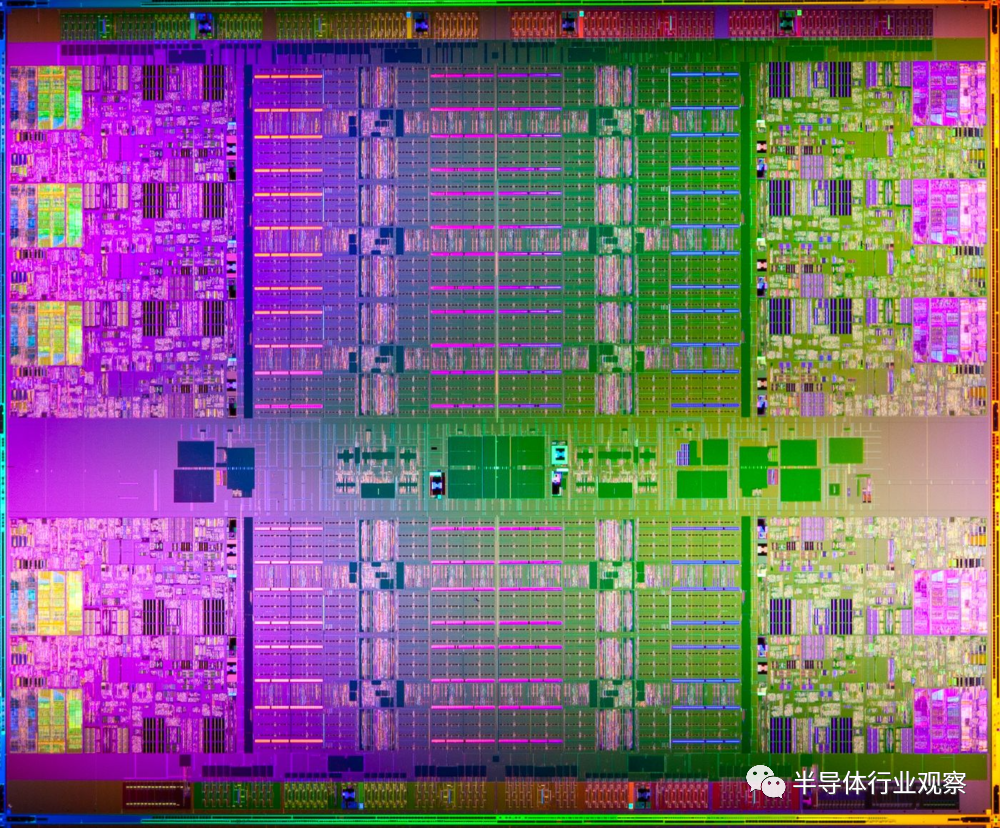

更可怕的要来了:双核Itanium 2「Montecito」,每个核心各自拥有12MB第三阶快取,总量高达24MB,整颗处理器的晶体管总量达17亿2千万历史新高,充分反应至596平方公厘的惊人尺寸。同时期的90纳米制程AMD双核Opteron(Rev F,2MB第三阶快取) 也不过230平方公厘。

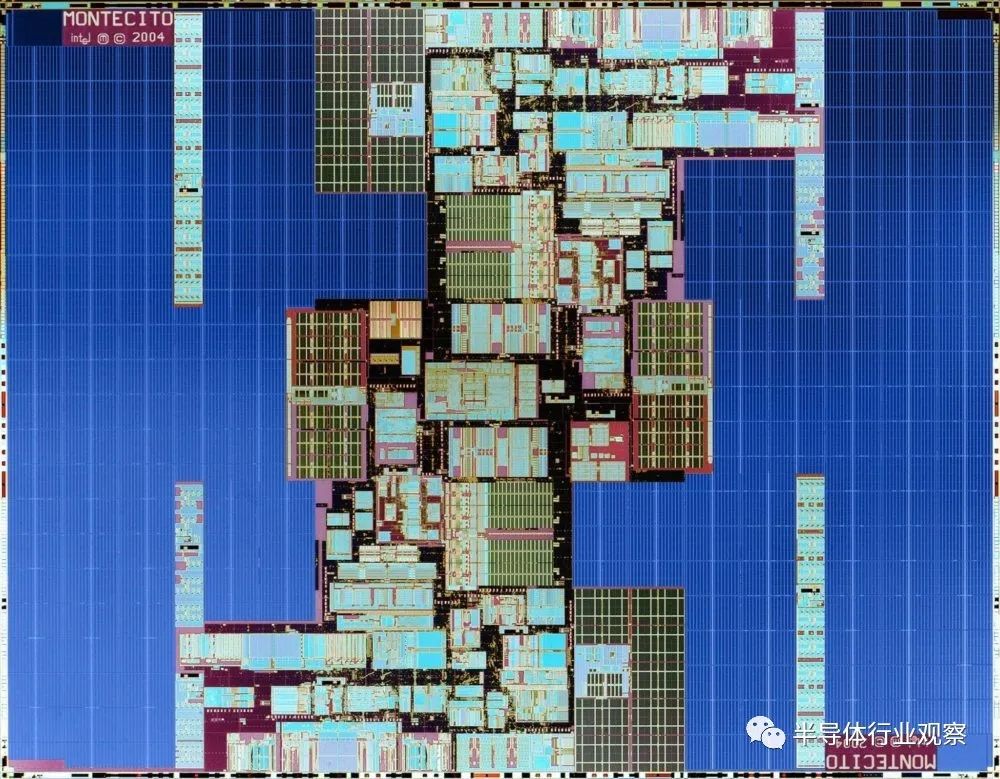

▲ Itanium 2「Montecito」(面积596平方公厘,90纳米制程,24MB第三阶快取记忆体)。

英特尔和HP就冲快取记忆体「赛猪公」冲上瘾了,应由昔日DEC Alpha研发团队操刀的四核心Itanium 9300「Tukwila」,让芯片面积直逼700平方公厘大关。

▲ Itanium 9300「Tukwila」(面积698.75平方公厘,65纳米制程,24MB第三阶快取记忆体)。

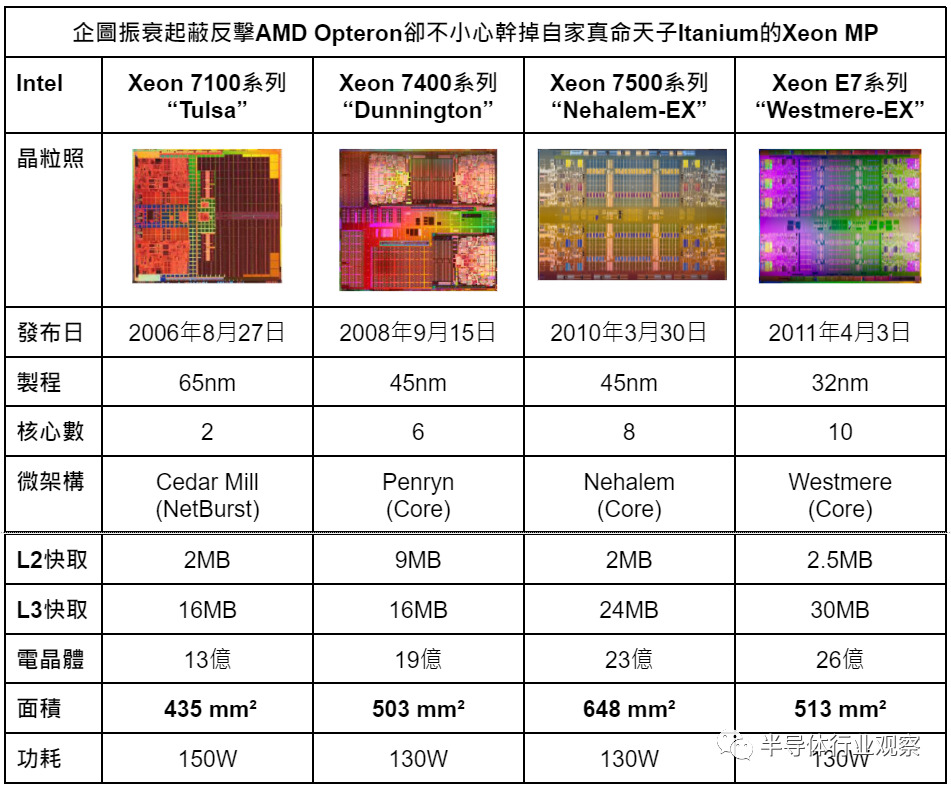

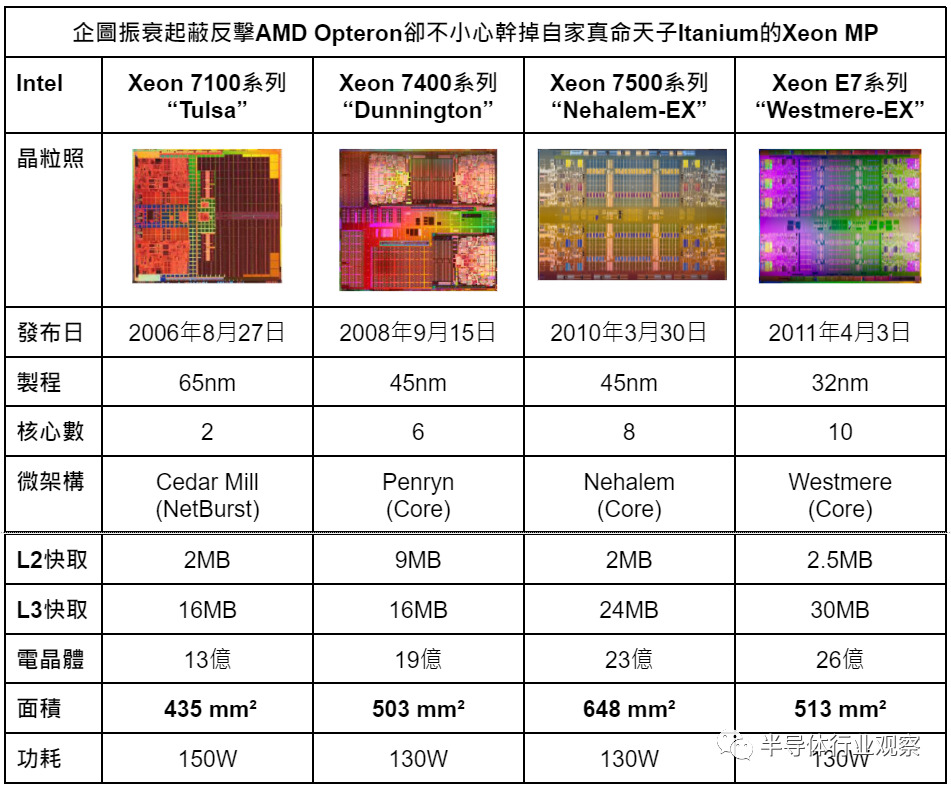

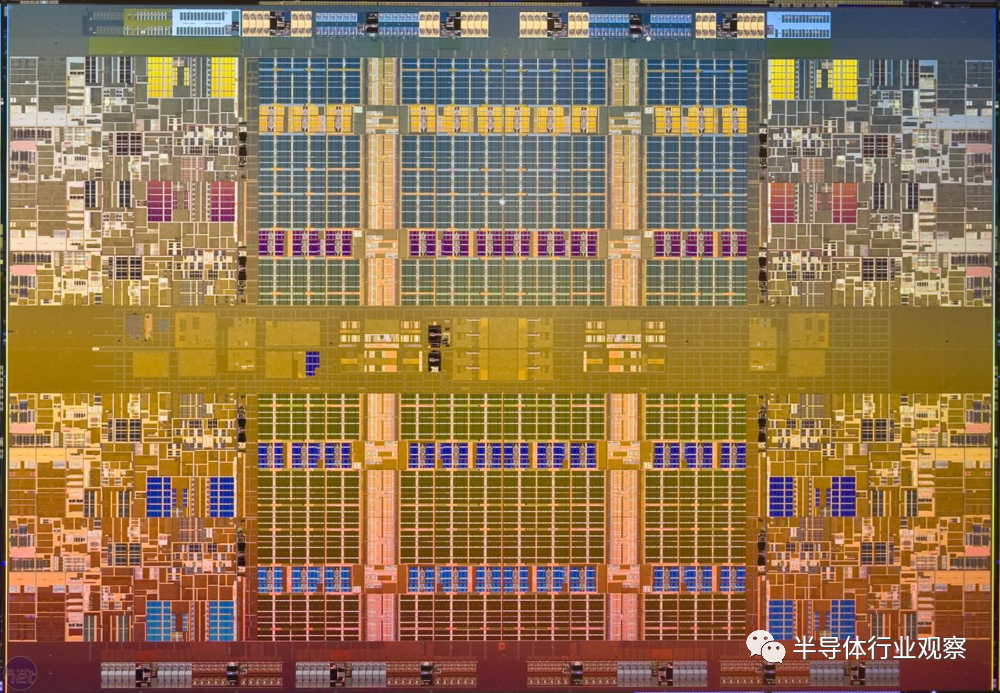

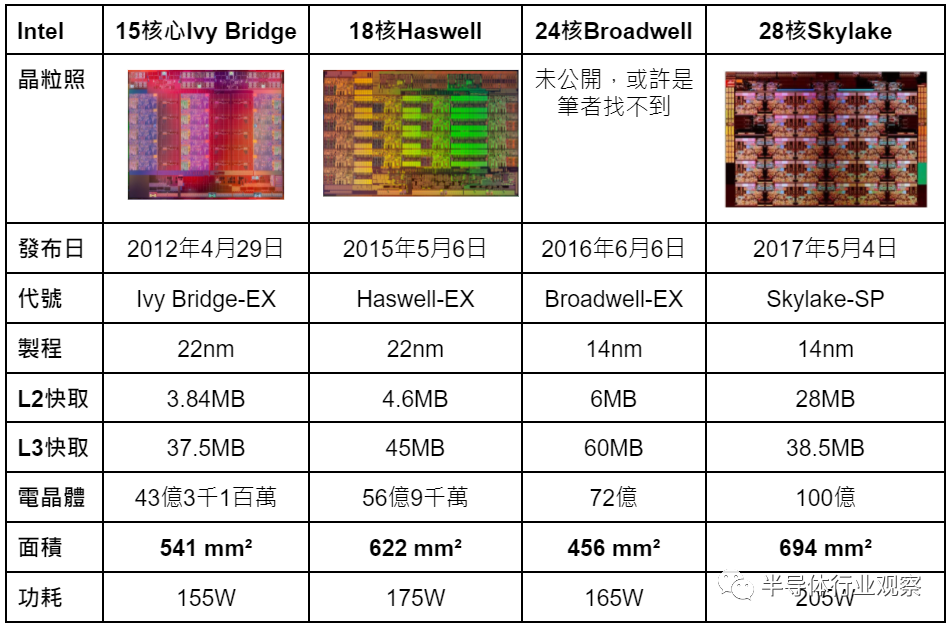

但这颗曾寄予厚望、整合Itanium和Xeon系统平台架构的象征,姗姗来迟至2010年,而「兄弟登山,各自努力」的英特尔x86处理器研发团队,分别在2006年和2008年推出Xeon MP 「Tulsa」(双核,16MB L3)和「Dunnington」(六核,9MB L2,16MB L3),也完成8核心Nehalem-EX Beckton,同样具备24MB第三阶快取,并拥有更多核心、更先进的45纳米制程、同等级的648平方公厘,意味进攻高阶伺服器市场不再是Itanium的专利。

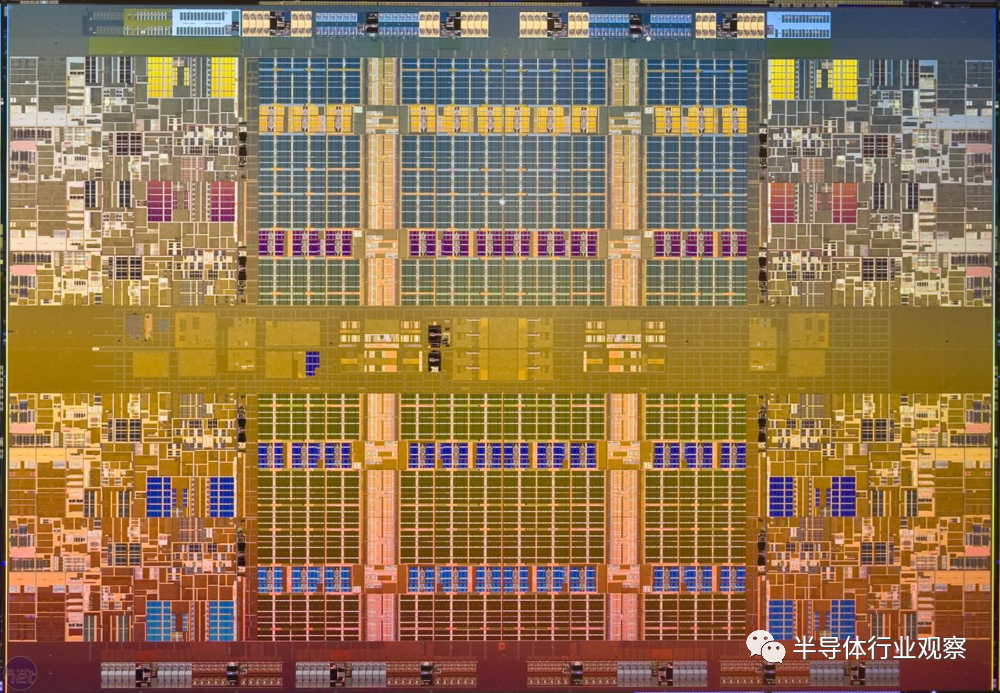

▲ Xeon 6500 / 7500 Nehalem-EX(Beckton,面积648平方公厘,45纳米制程,24MB第三阶快取记忆体)。

微软紧接在2005年「追随」HP终止Itanium工作站专用的Windows作业系统还不打紧,2010年宣布「快速发展的x86伺服器,同样也可做到高阶伺服器的延展性与稳定性,因此停止发展Itanium版本Windows作业系统与相关应用程式」。

这刀极度致命,注定Itanium终究只是「HP御用」的高阶RISC处理器,绝无凭借Windows作业系统的亲民性、逐步延伸到中低阶市场的契机,更不可能激增出货量,顶多使其成为英特尔站稳高阶伺服器市场的精神象征,与优先导入先进技术(像高可靠性与大型化的快取记忆体) 的验证载具。并购Sun的甲骨文2011年「锦上添花」再补一刀,搞到跟HP对簿公堂,让Itanium生态圈陷入无可挽救的绝境。

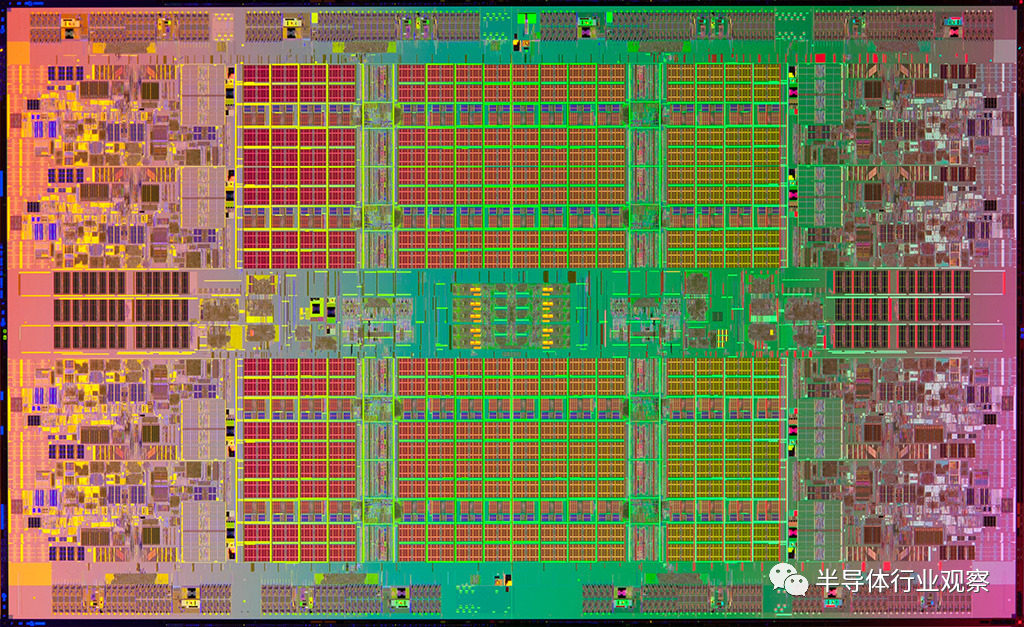

所以2012年,由DEC Alpha团队负责、集历代技术大成的8核心Itanium 9500「Poulson」,就成为英特尔「钦定64位元真命天子」的绝响,2017年的Itanium 9700「Kittson」仅换汤不换药、连制程都不升级的小改版(晶粒照片也如同一个模子刻出来,看不出明显差别),存在目的仅为了维持现有高阶伺服器客户的保证供货期。

▲ Itanium 9500「Poulson」(面积544平方公厘,32纳米制程,32MB第三阶快取记忆体)。

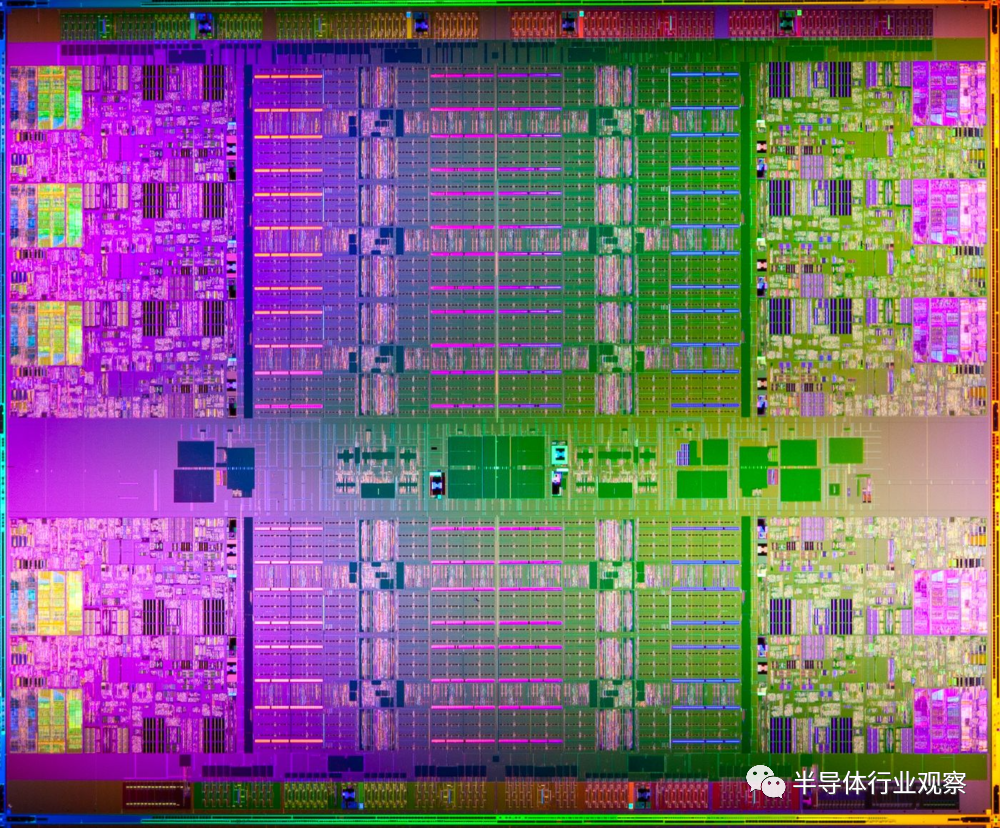

当英特尔x86处理器的钟摆(Tick Tock)巨轮顺畅运转时,辗压的不只AMD与苟延残喘的RISC诸神,更包含自家Itanium。2011年4月Xeon E7-x8xx系列「Westmere-EX」,带来10核心与30MB第三阶快取,替这场劳民伤财的「内战」划下悲惨的休止符。

▲ Xeon E7-x8xx「Westmere-EX」(面积513平方公厘,32纳米制程,30MB第三阶快取记忆体)。

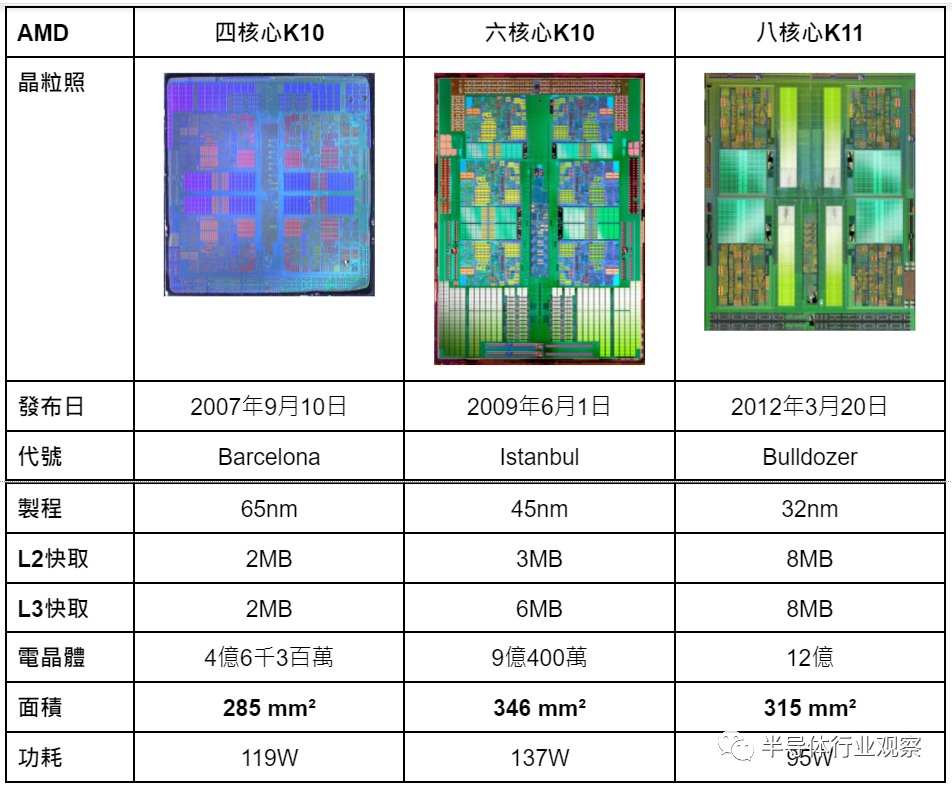

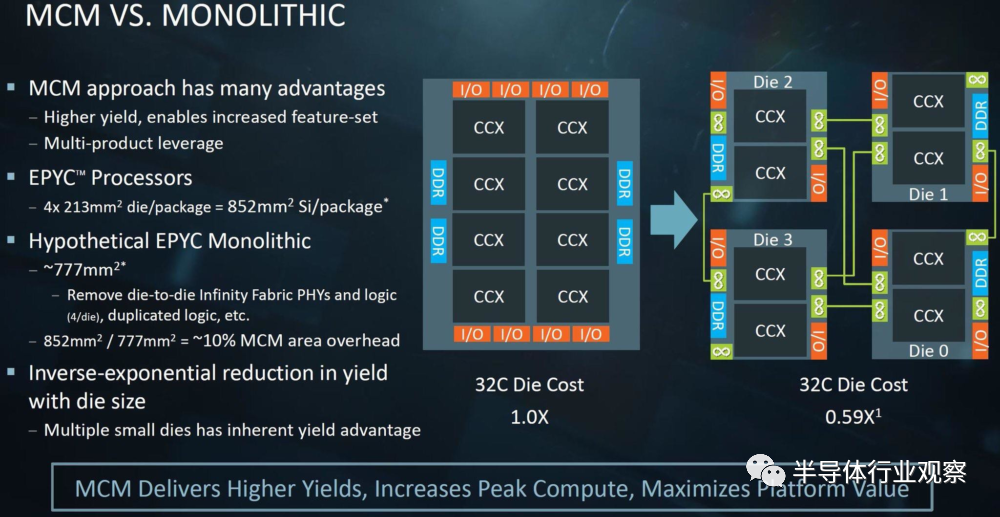

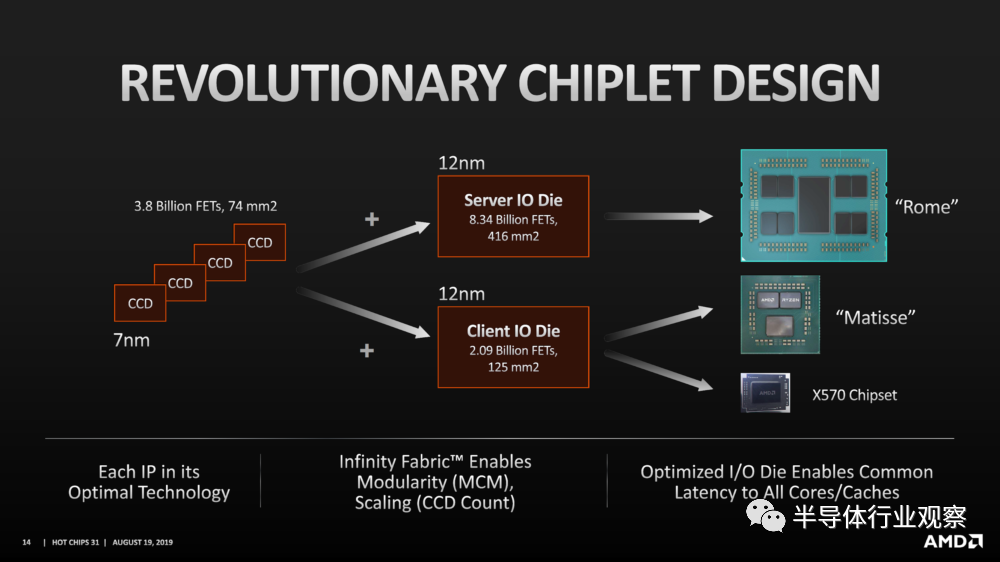

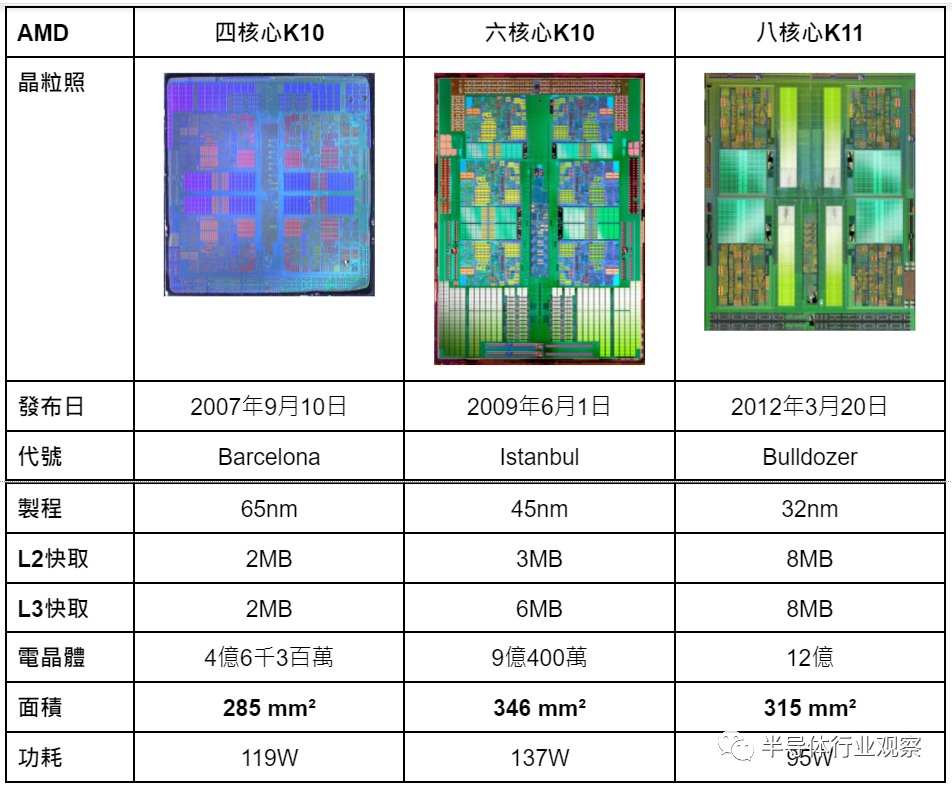

看到这里,想必各位会好奇这时候的AMD到底在干么。事实上,可能基于研发资源有限,伺服器、桌机和笔电须共用晶粒的关系,AMD从来没有动过「把芯片搞大」的脑筋。自从Zen时代来临,大玩Chiplet「包水饺」的AMD就更没有这样做的动机和理由了。

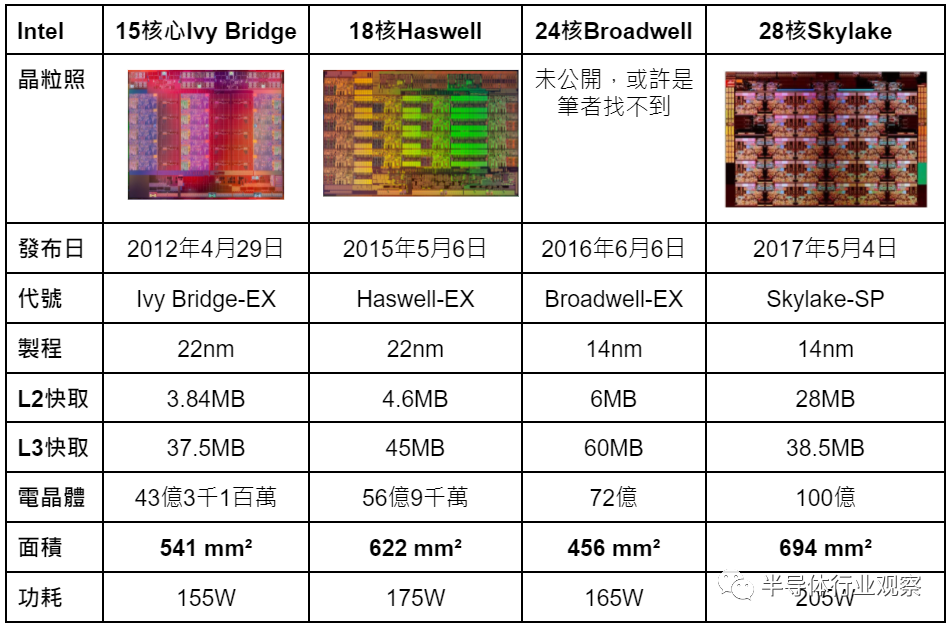

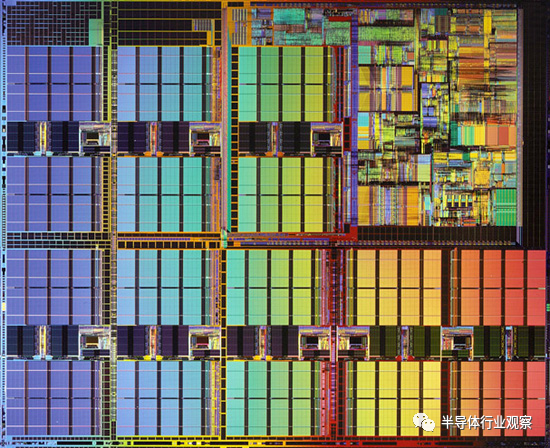

以下同场加映「钟摆期」(2011~2017年),发挥绝对制程优势,彻底压垮AMD的英特尔x86巨兽。

后来我们也都知道,物极必反,英特尔大芯片策略被AMD多芯片Chiplet反将一军,搞到英特尔也得东施效颦类似路线。前阵子英特尔执行长Pat Gelsinger直言「英特尔十年来的错误政策导致今日结果,并指出问题不会一夕之间解决」,笔者满好奇是否包含钟摆时代的巨兽就是了。

「RISC诸神」也没闲着,听说还有「CISC精灵」?

基于商业层面考量,设定将「一统RISC伺服器江湖」的Itanium「不得不」消灭Alpha、PA-RISC与MIPS,且因一连串阴错阳差,连自己都消灭了,让英特尔重回集中全力研发x86处理器老路。但IBM、Sun与Fujitsu可不吃英特尔那套(好吧,Fujitsu一度劈腿做出Prime Quest),继续打造自家高效能处理器,并在「增肥」方面功力不遑多让。

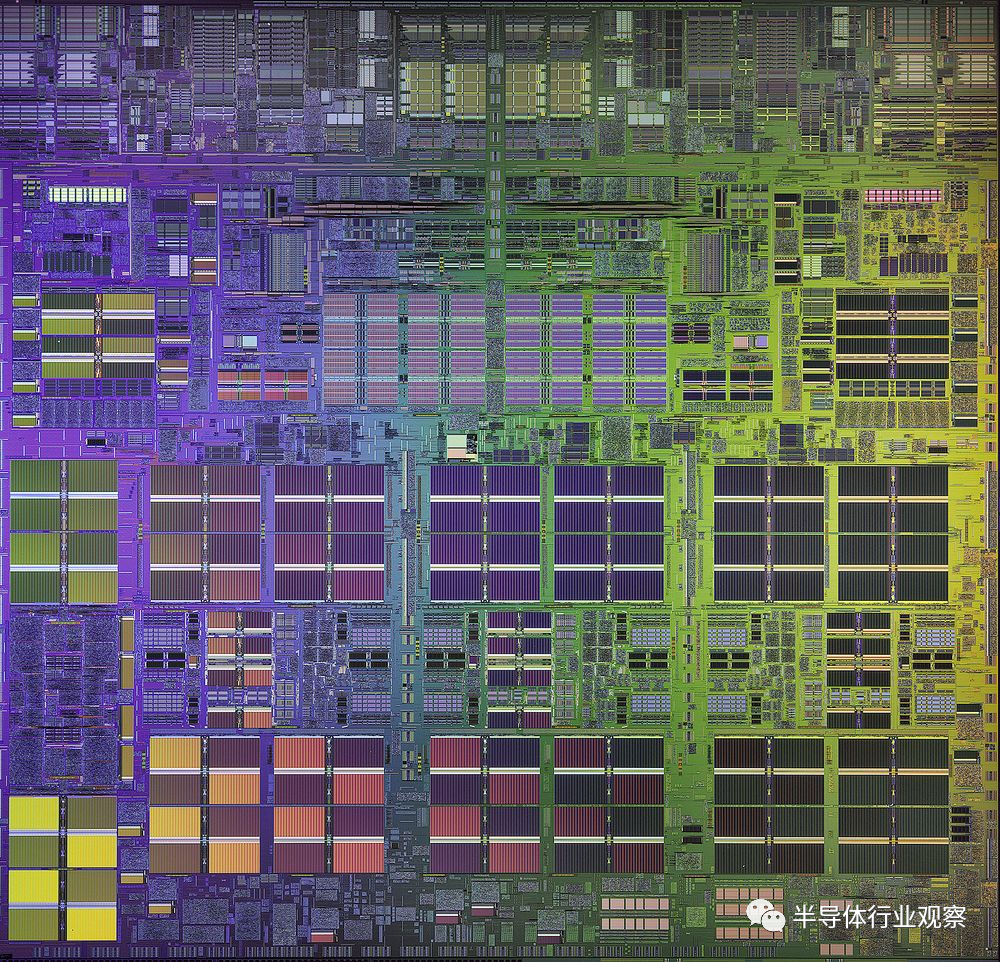

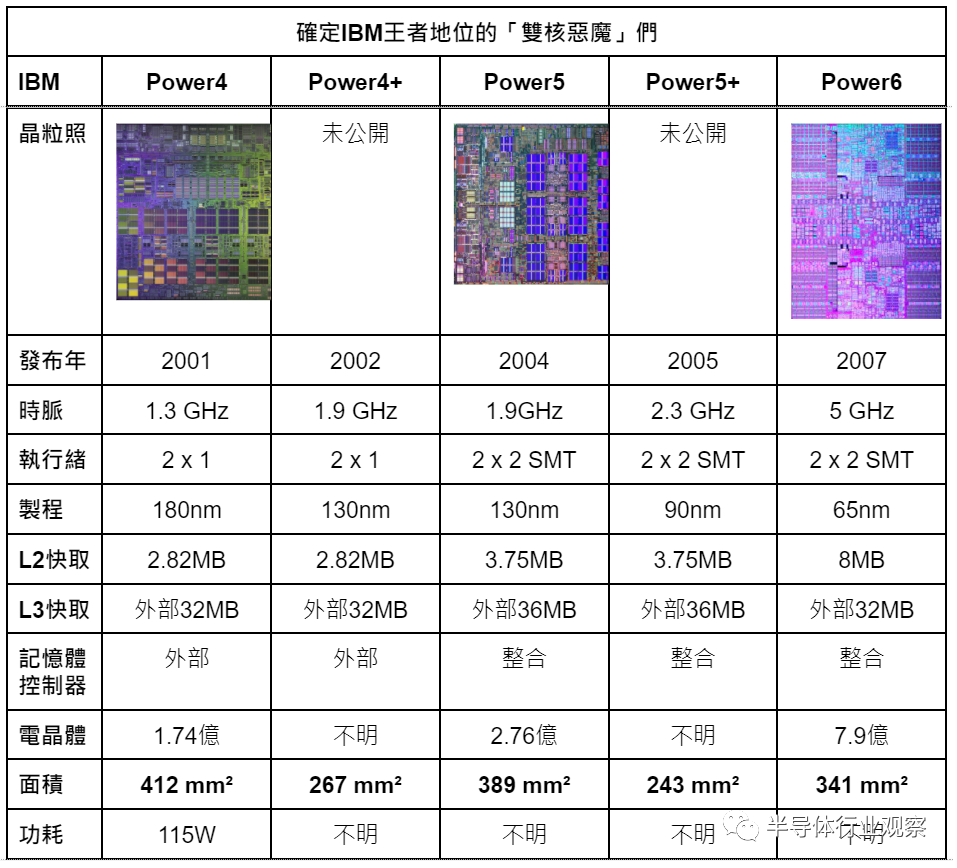

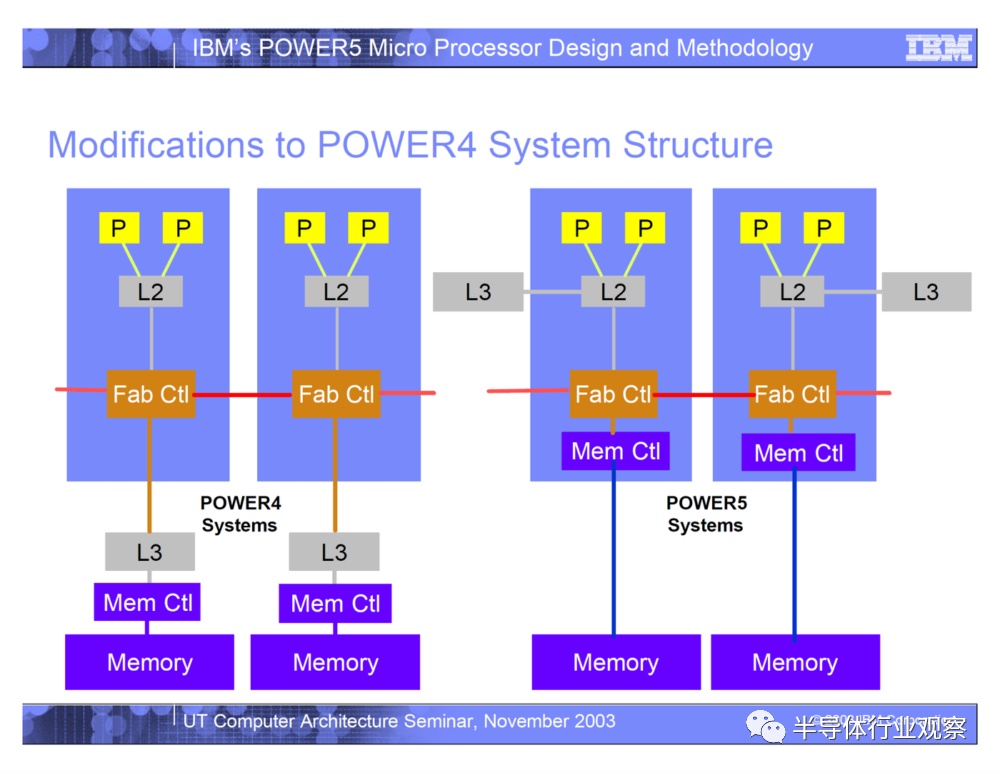

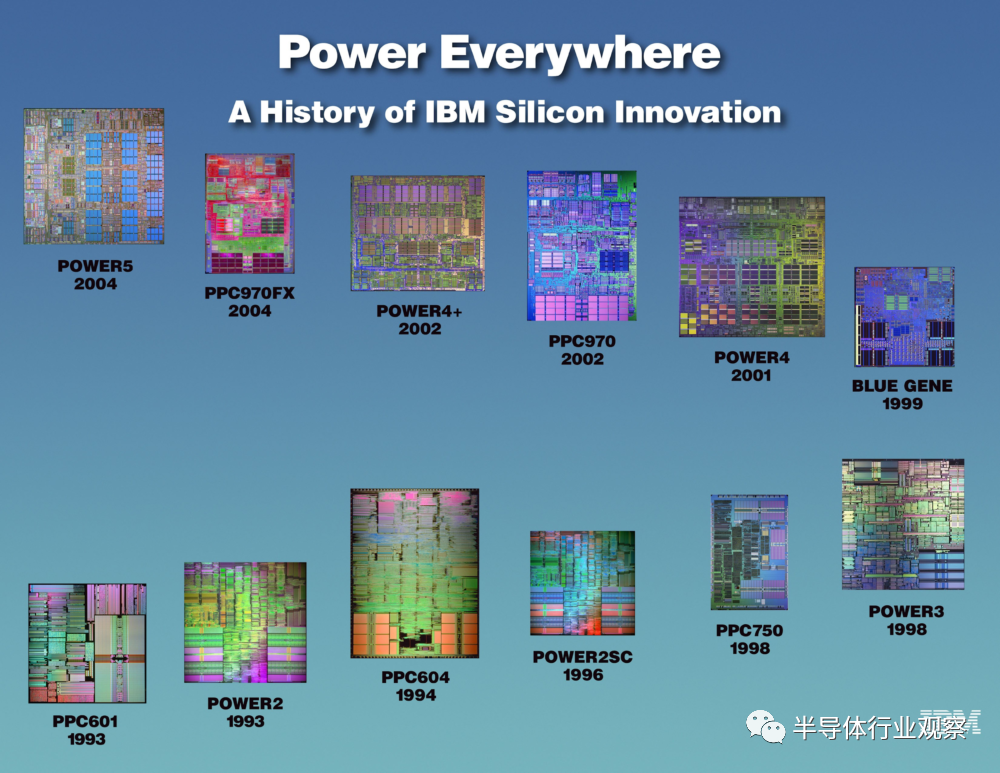

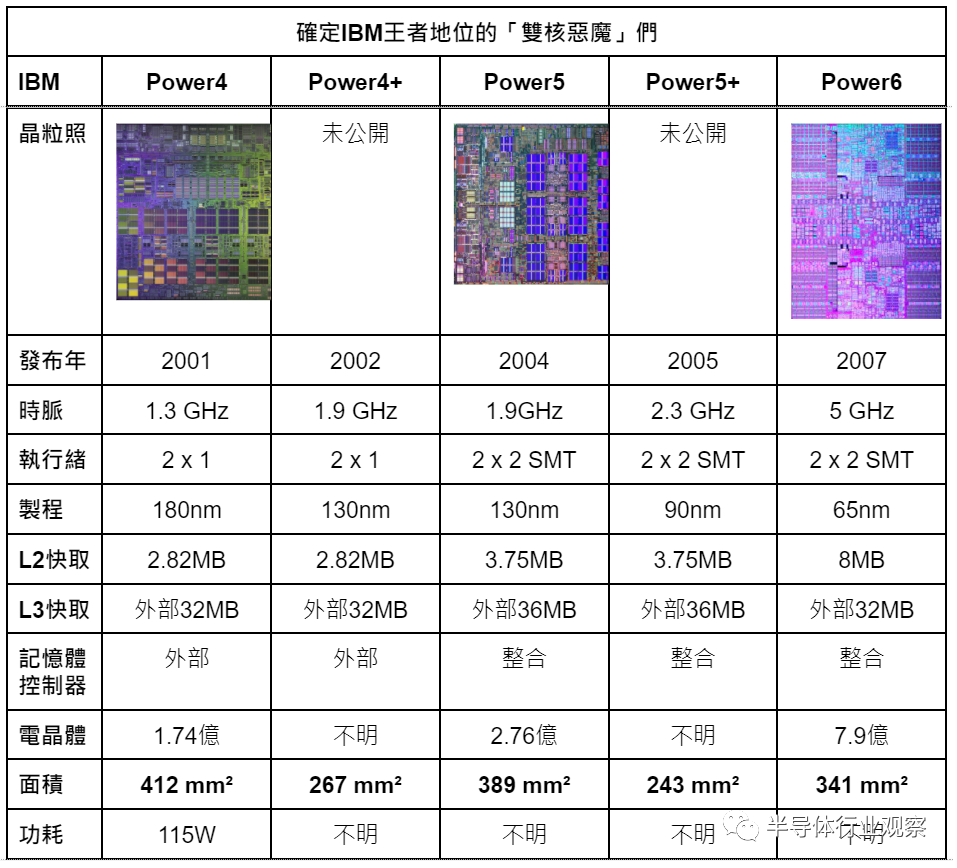

检视这些「残党」21世纪的丰功伟业前,我们绝不能错过「蓝色巨人」IBM那颗在计算机工业史上极具盛名的「首颗原生双核心伺服器处理器」Power4,开挂「SMT(同时多执行绪)与整合型记忆体控制器」的后继者Power5,以及直冲5GHz时钟大关的Power6。

1999年底披露、2001年上市的Power4(代号Regatta),不仅相容IBM所有商用RISC指令集(RS/6000、AS/400、PowerPC),也有大量个人电脑无缘一亲芳泽的尖端技术,说这不是被英特尔逼出来的绝对骗人。

Regatta字面原意为「两艘并行的船只」,实际却包含多个意涵,除了代表IBM在Unix伺服器市场的两大竞争对手Sun和HP,意指Power4双核心。另外,IBM将四颗Power4芯片和四颗32MB快取记忆体封装成一颗多芯片封装模组(MCM),就可实现8处理器核心和多达128MB的第三阶快取。

姑且不论半导体制程发展,AMD一向跟IBM走得很近早就不是新闻(包含Lisa Su,AMD高层满满一票老IBM人),笔者当时就常开玩笑说为何AMD总是跟着IBM屁股走,时过境迁,似乎印证笔者的玩笑话似乎所言不虚。

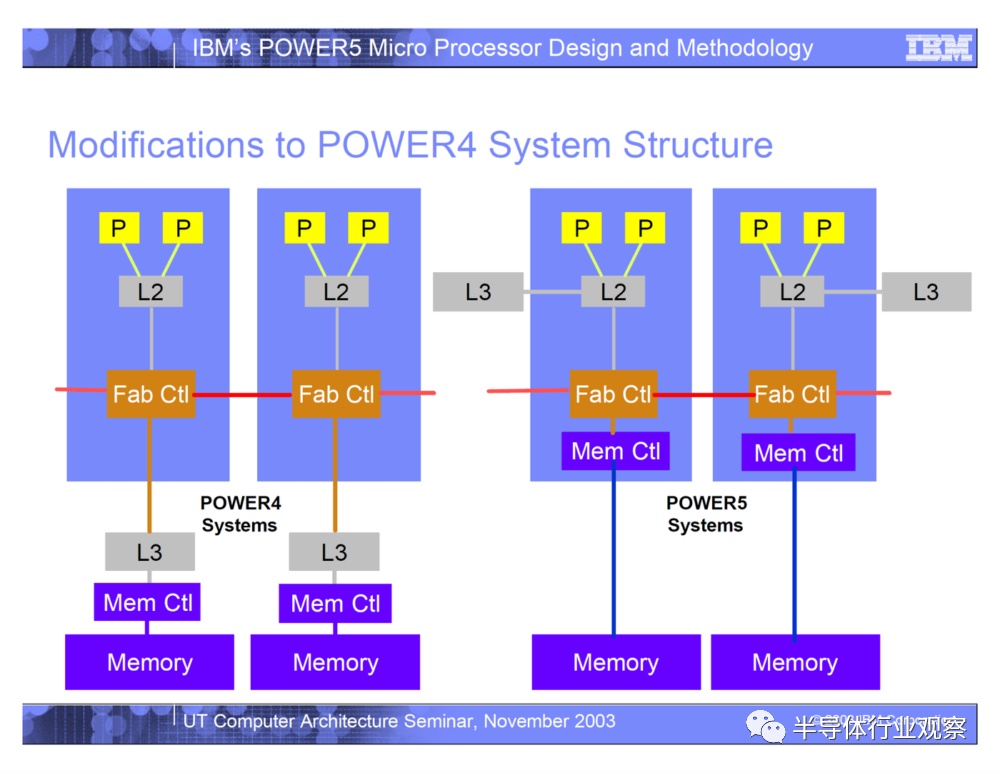

▲ IBM Power4「Regatta」(面积412平方公厘,180纳米制程,2.82MB第二阶快取记忆体)。

接着就是告诉全世界「SMT(同时多执行绪) 结合整合式记忆体控制器究竟有多可怕」的IBM Power5「Squadron」(战斗部队)。让IBM在2004年夏天高阶伺服器市场上演前无古人后无来者的「效能大屠杀」。Power6更是让IBM「逆风而行」展开追求超高时钟的追逐战。

-

TPC-C:16颗Power5的p5-570,足以抗衡「64颗」英特尔Itanium 2的HP Integrity SuperDome。

-

SAP SD-2 Tier:8颗Power5胜过「32颗」Itanium 2和「36颗」Sun UltraSPARC IV。

-

SPEC CPU 2000:Power5一举创下浮点项目的历史新高,单核心效能更是英特尔Itanium 2的「两倍」。

-

更扯的还在后面:2004年11月p5-595(32颗Power5),创下TPC-C世界纪录,效能相当于「二、三、四名总和」,和同级产品相比,不是人家两倍三倍,就是四倍五倍,甚至快要六倍。

简而言之,就是「一个核心打对方两个还有剩」概念。刚从DEC Alpha继承CPU效能王冠的IBM Power,就是这么厉害。所以也请各位读者原谅笔者对苹果M1的表现竟如此无感,论这种横扫千军的「王者气质」,现在的苹果还差远了。

▲ IBM Power5「Squadron」(面积389平方公厘,130纳米制程,3.75MB第二阶快取记忆体)。

因此IBM Power也成为RISC诸神中,唯一能跟x86双雄激战到最后一刻的那位,即使论纯粹的理论运算效能,IBM也渐渐无力抗衡x86双雄的压倒性核心数量优势,仅能仰仗极完整的软硬件解决方案、高不可攀的高阶功能与众多老客户对蓝色巨人的长期信赖。

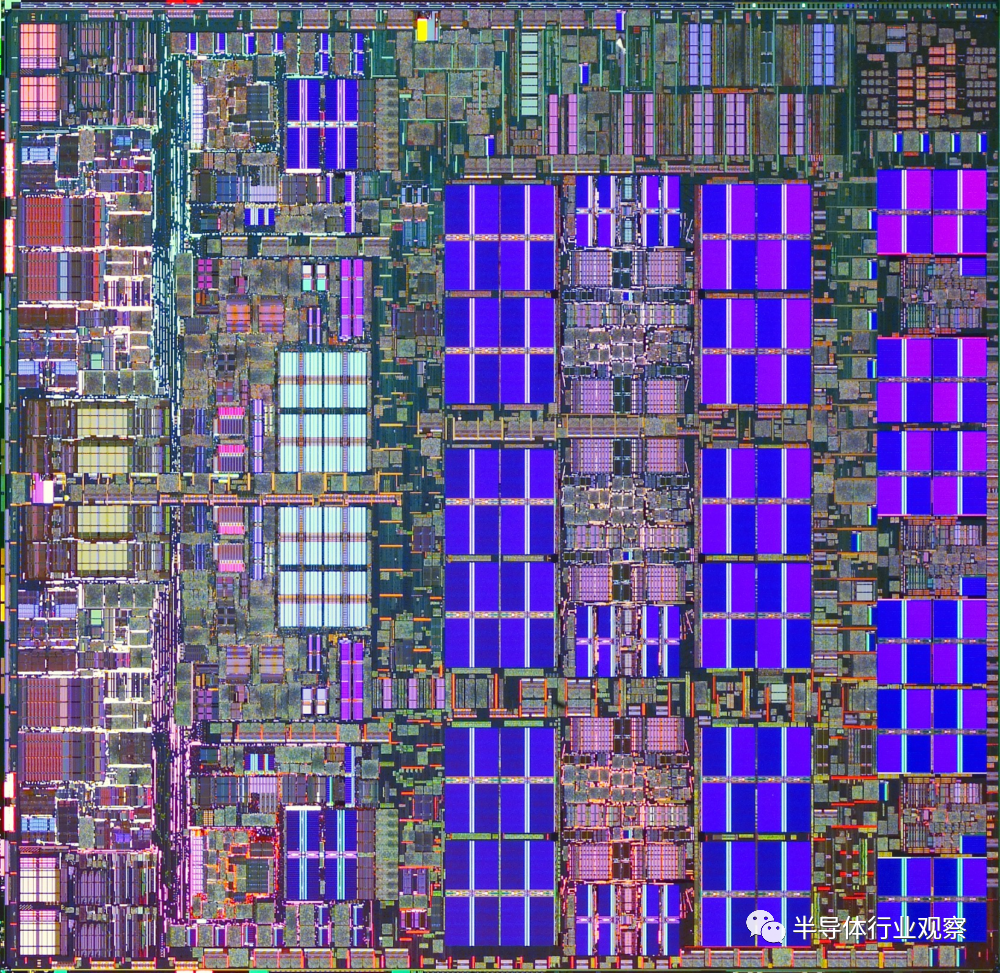

这就不得不提IBM的某项独门绝技:和处理器核心「送做堆」的超高容量eDRAM(嵌入式DRAM),这也是IBM自从Power7之后的「晶粒增肥器」。一般来说,我们都知道一个SRAM储存位元需要6个晶体管(也有4个晶体管的特殊设计),而DRAM只要一个,后者更容易实做出更高容量(缺点是存取延迟)。但天底下没有白吃的午餐,把逻辑制程的处理器核心和DRAM做在一起,无论电路设计和制程工序,都带来更麻烦的艰巨挑战。

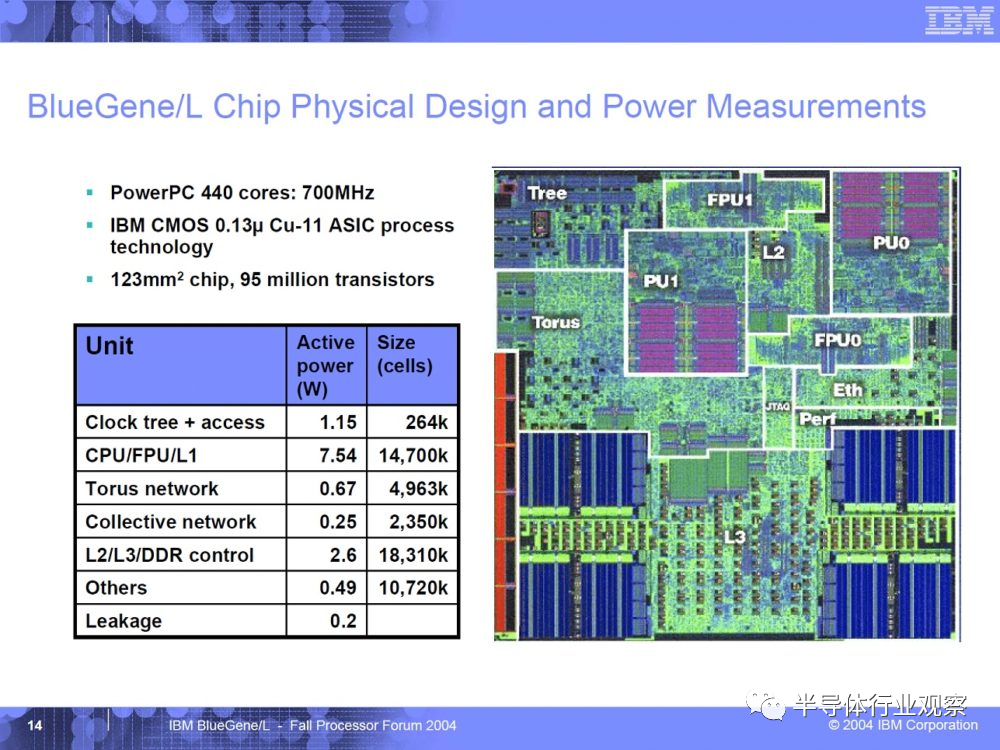

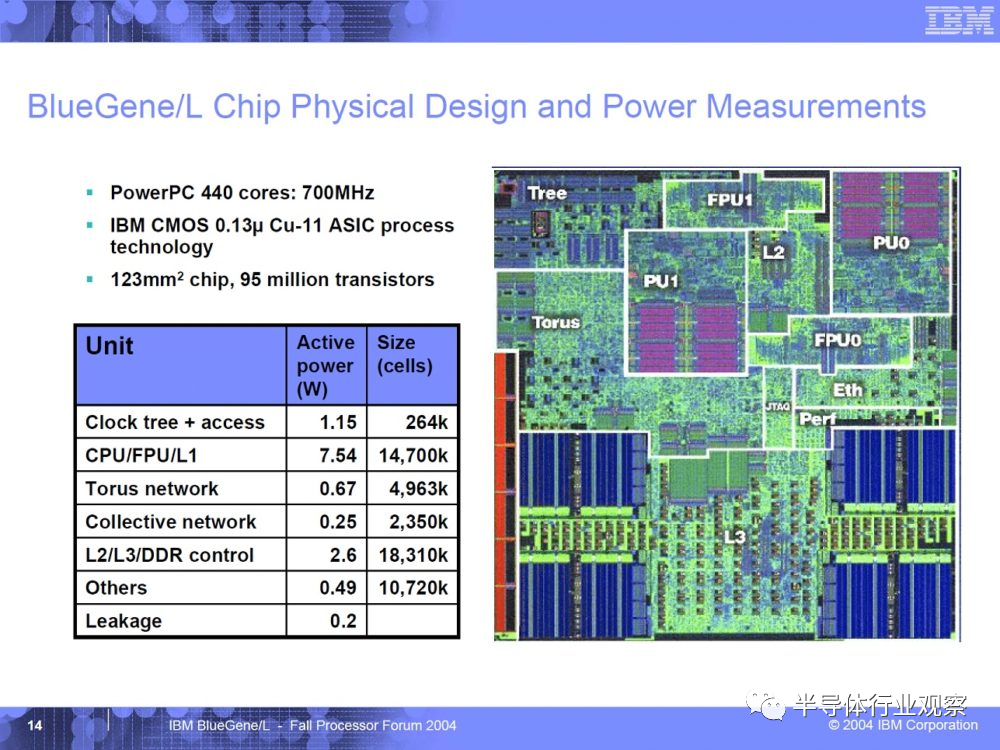

这就刚好是IBM的特长,不限于高阶伺服器的Power,从2004年的世界最快超级电脑IBM BlueGene / L采用的特化版双核PowerPC 440,就内建4MB的eDRAM为第三阶快取记忆体。家用游戏机领域,亦不缺eDRAM的身影,Sony PlayStation 2的绘图核心Graphics Synthesizer(GS),塞入4MB eDRAM。PlayStation Portable(PSP)用了4MB,微软Xbox 360用了10MB。任天堂Wii U则高达32MB。以上全数出自IBM的杰作。

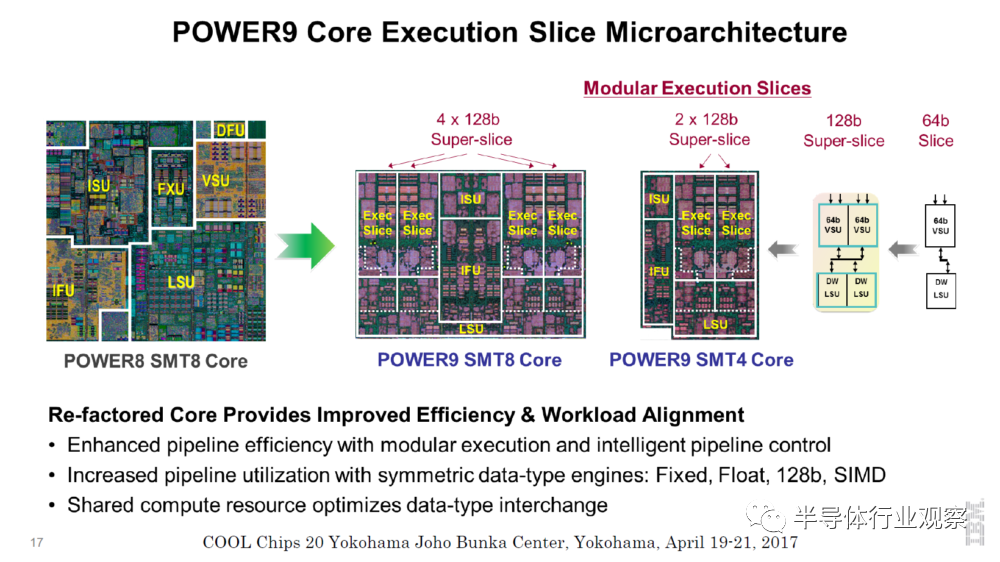

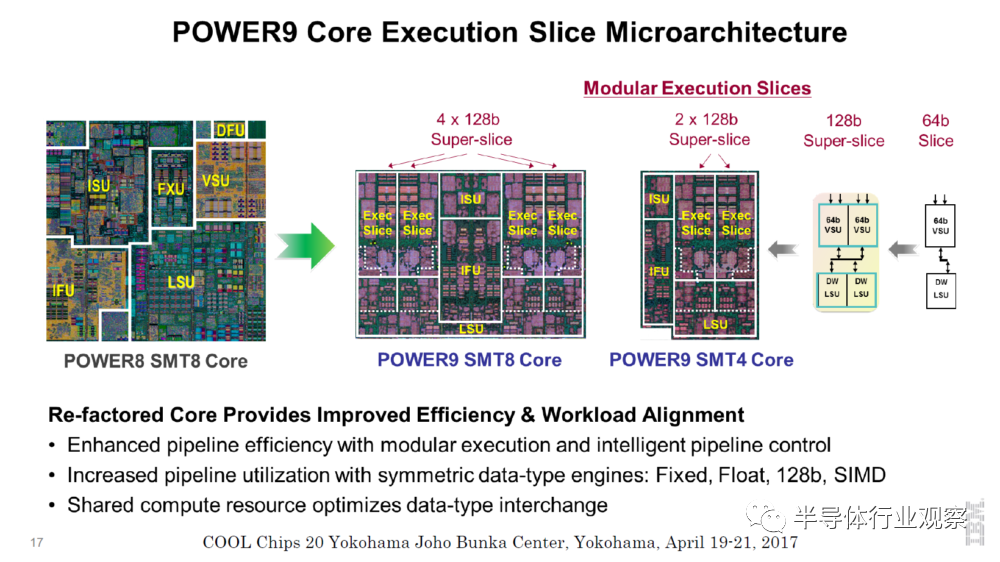

在此也谈谈IBM从Power9开始的另一项特技:两个处理器核心(SMT4)可组成一个大核(SMT8),视不同应用情境,推出不同核心总数的产品。

讲了这么多,也差不多该好好端详IBM Power家族的「相扑力士」。

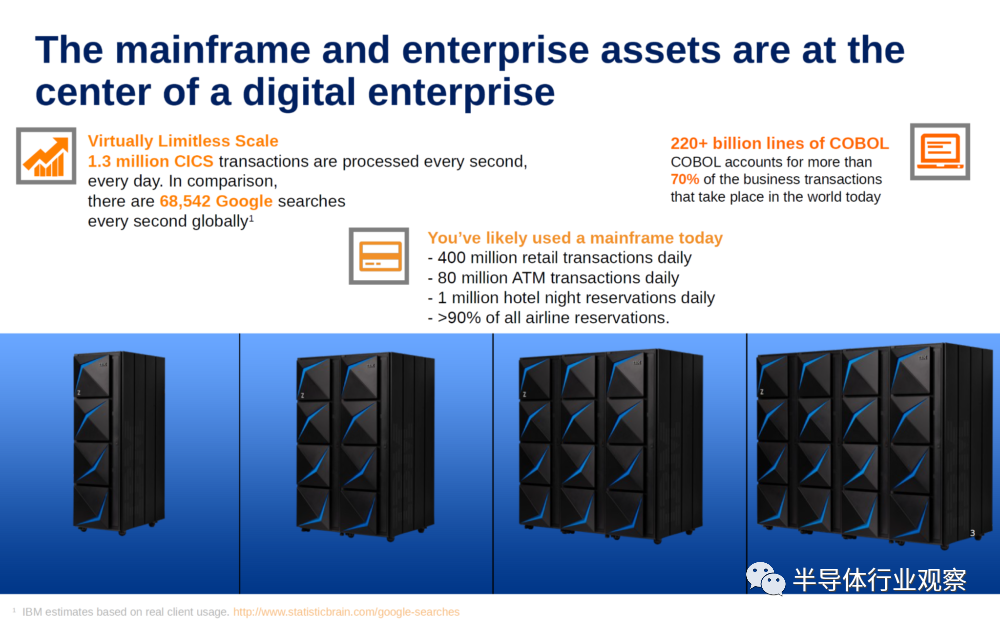

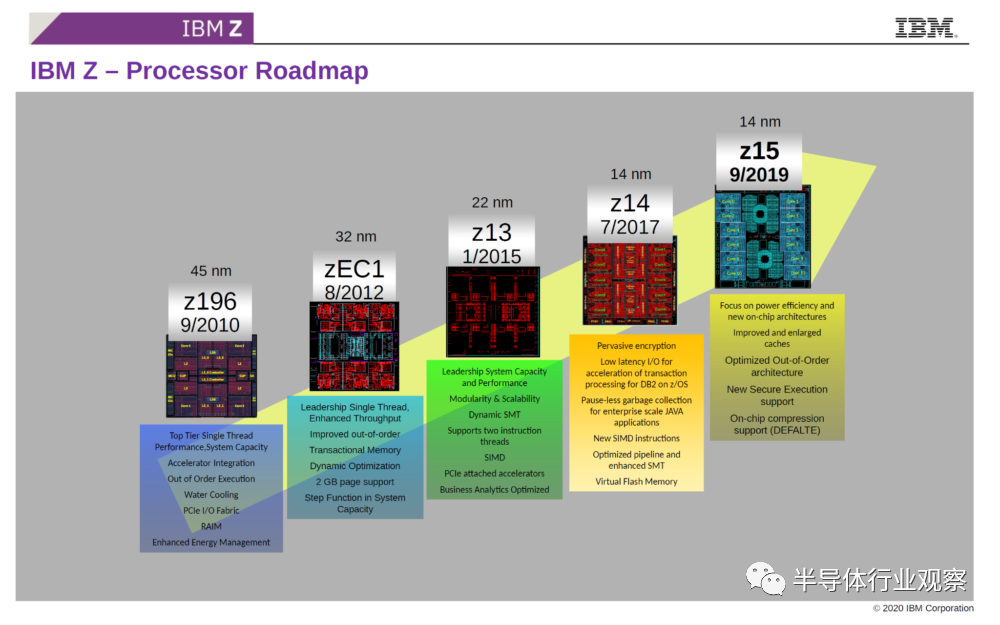

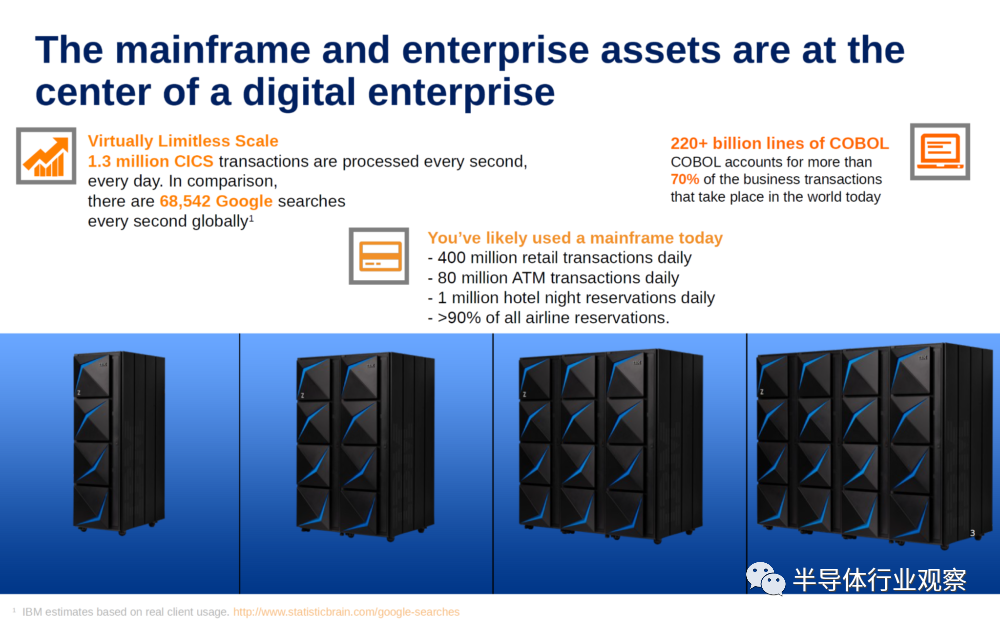

但IBM高阶伺服器处理器并不只有RISC的Power,还有历史更悠久、如计算机工业历史缩影的CISC大型主机(Mainframe),源自1964年「人类历史上最大型商业产品开发计画S/360」的Z系列处理器,只是没有Power如此风光。

对IBM来说,这些「始祖精灵」后代对公司营收的重要性,还远高于「看起来比较先进」的RISC先驱者,更罔论IBM有太多尖端科技,尤其涉及高可靠性和虚拟化的关键环节,还几乎千篇一律,清一色从Z系列「下放」到Power。

所以趁这个机会,瞧瞧数十年来支撑无数金融保险业永不停机服务的心脏。这些年试图将核心帐务系统迁出IBM大型主机「拥抱开放系统」的银行IT升级案,好像也没听过几个有好下场。

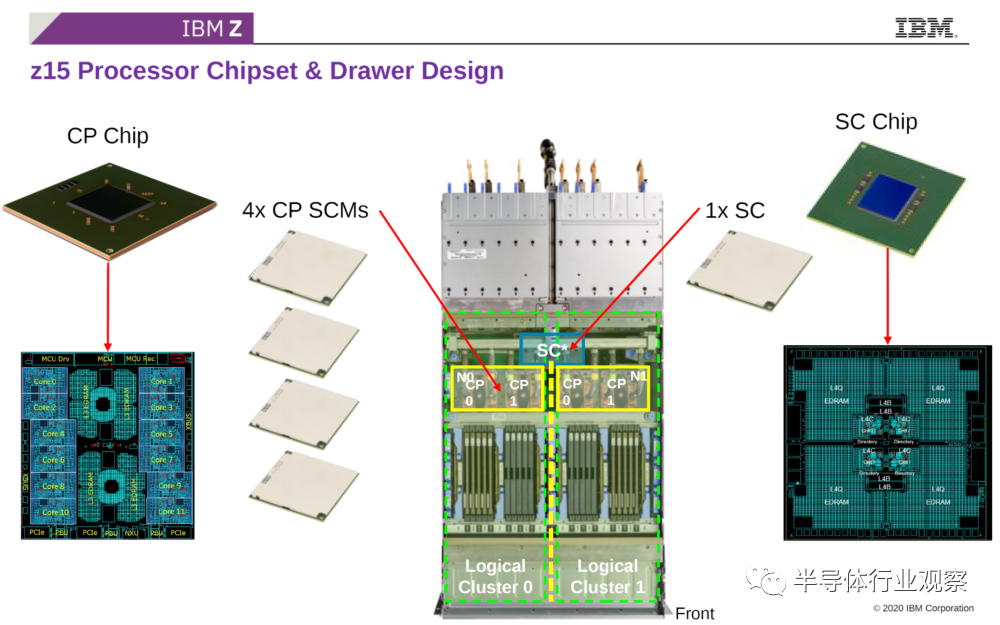

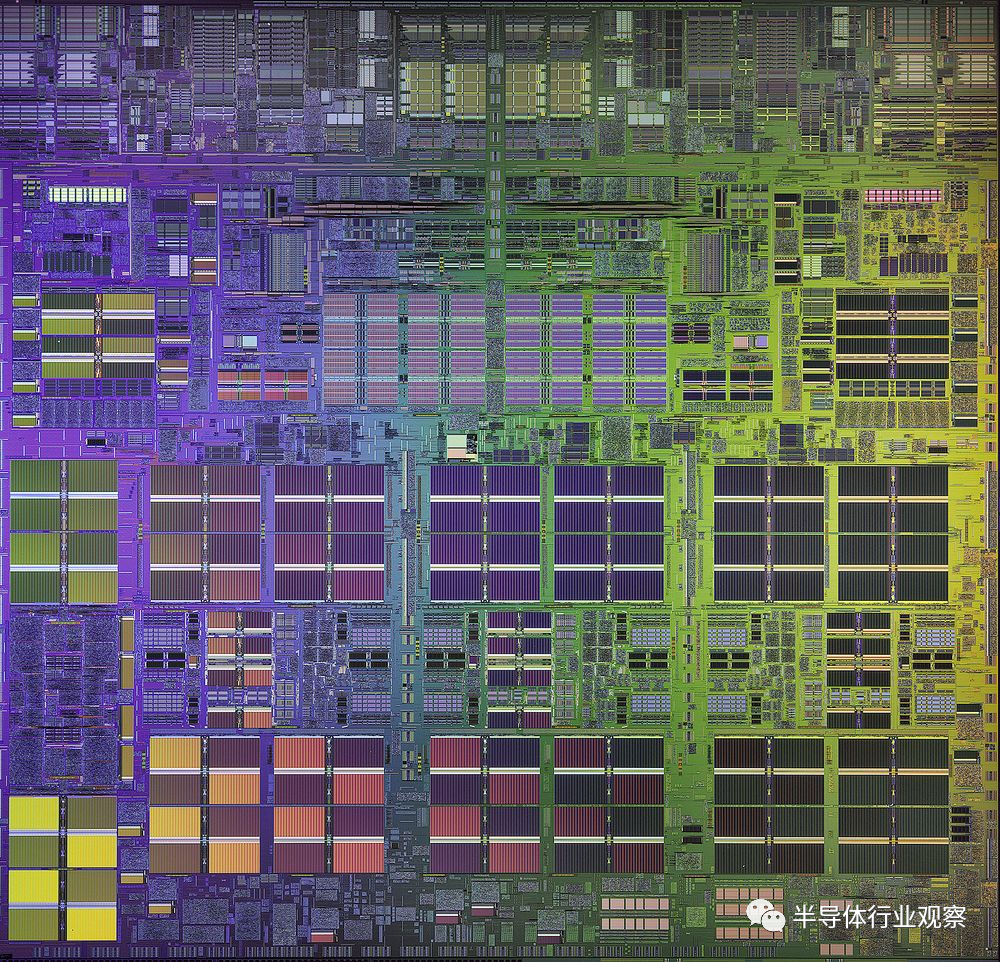

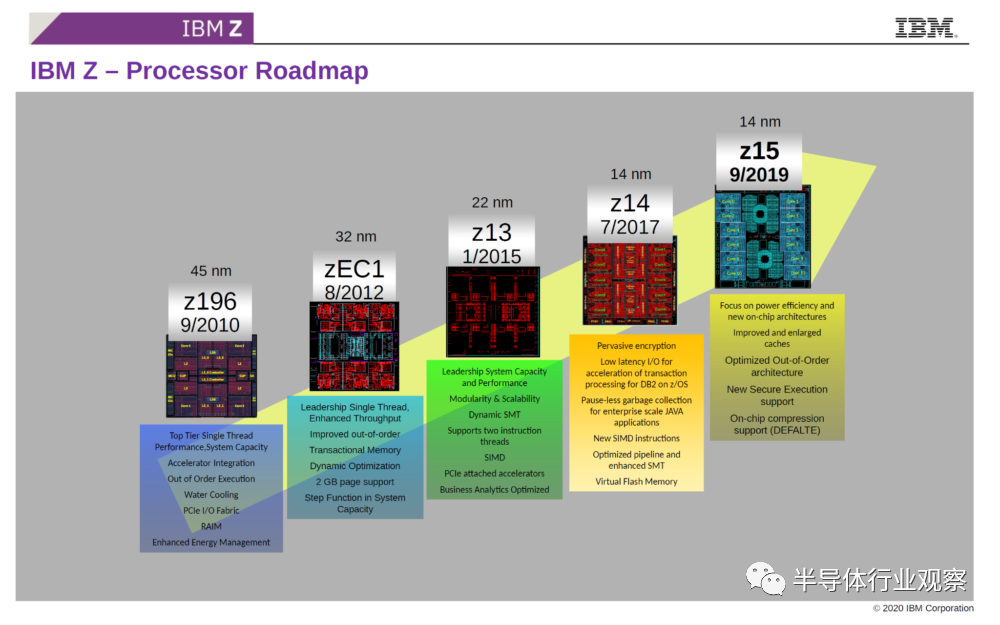

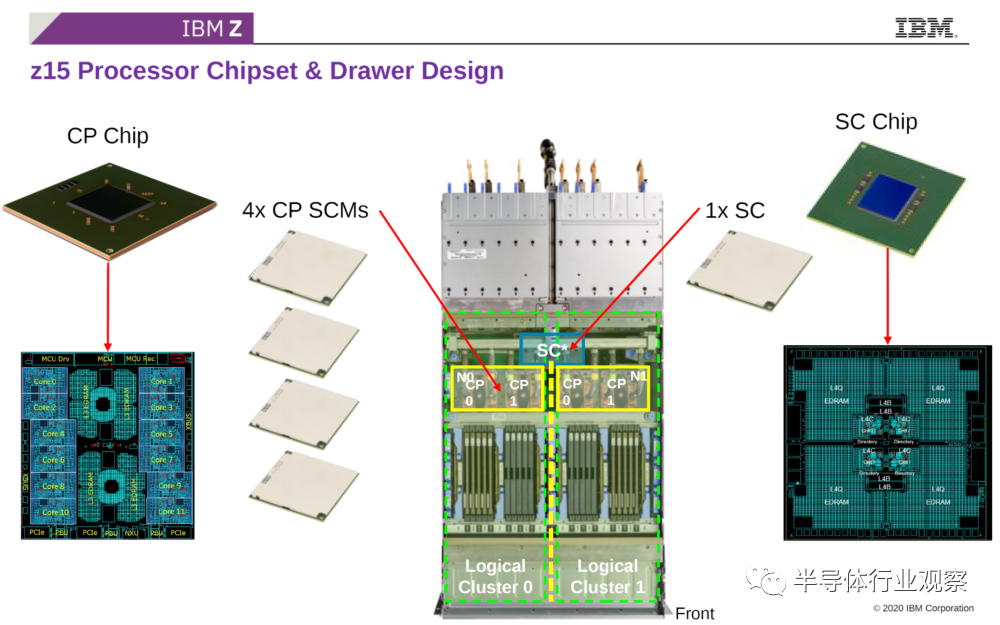

让我们将目光转向IBM最新型的z15。系统由两种晶粒面积同为696平方公厘的巨无霸主芯片构成:12核中央处理器(CP,Central Processor)和嵌入960MB eDRAM的系统控制器(SC,System Controller),一个z15机箱包含四个CP和一个SC,总计有超过「2.4GB」的海量快取记忆体容量。

换言之,由五个z15机箱组成的最大系统组态,包含240个处理器核心和12GB eDRAM,另外还有40TB主记忆体、60个PCIe Gen4 x16、192张I/O扩充卡与384个传输通道的扩充能力。以上种种夸张的规格,都是维持每个月公司薪资转帐日时,银行核心帐务系统能正常稳定运作的硬件根基。

从z15夸张到极点、将eDRAM挥洒到淋漓尽致的快取记忆体阶层,就不难想见System Z大型主机在IBM如同「皇冠上的宝石」之地位。

都写到这步了,也请各位勉为其难陪笔者回头看看近年z系列中央处理器。虽然z14和z15的中央处理器拥有相近制程和相同晶粒面积,但IBM却借使用eDRAM实作第二阶快取记忆体,挤出更多晶体管空间,容纳多出的两个核心与倍增的第三阶快取记忆体。

说到大型主机,除了本家IBM,现在市场还有日本Fujitsu的GS(Global Server)21系列,但指令集相容性仅IBM ESA/390(31位元),并不包括64位元的z架构,所以跳过不谈。

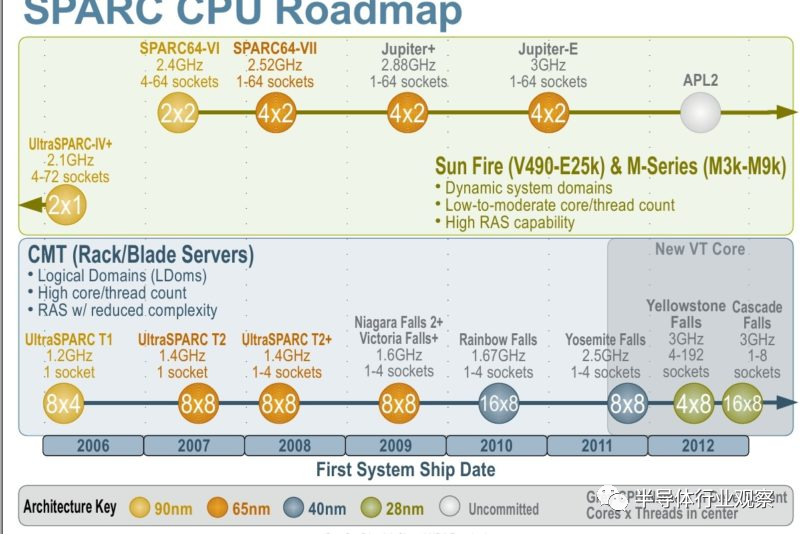

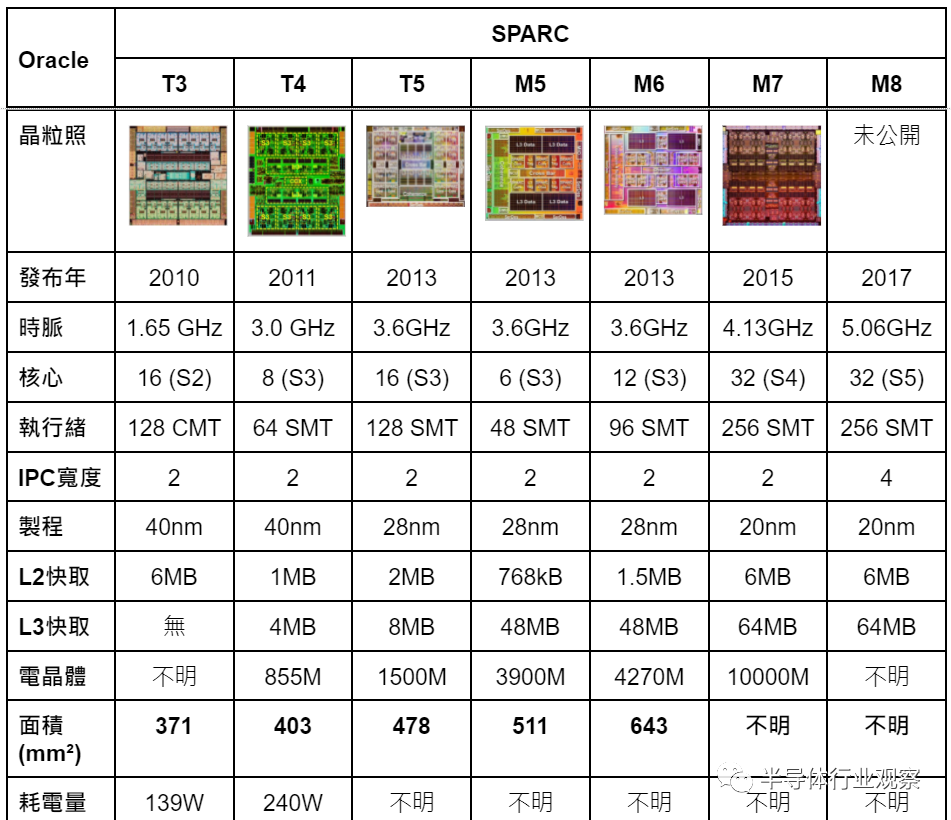

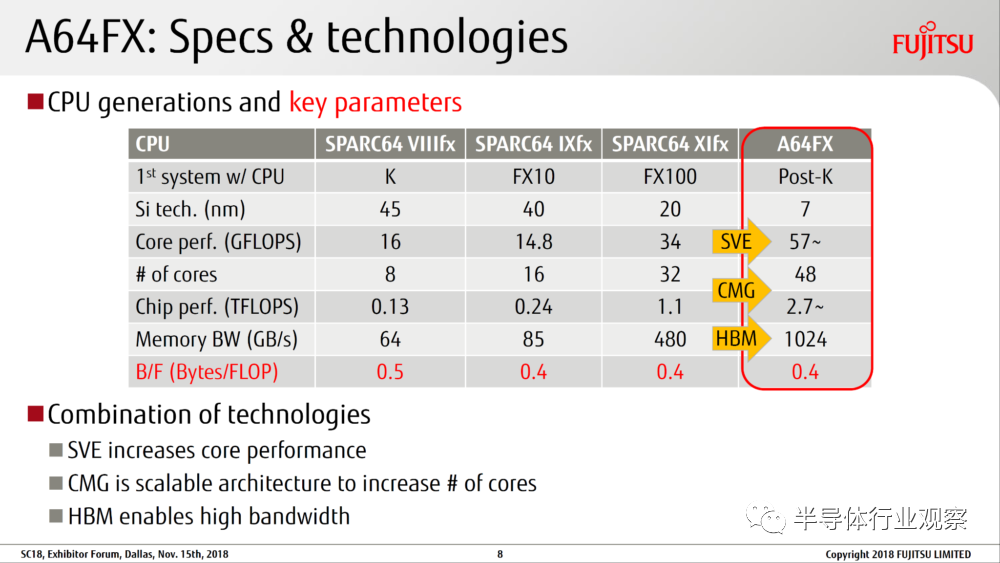

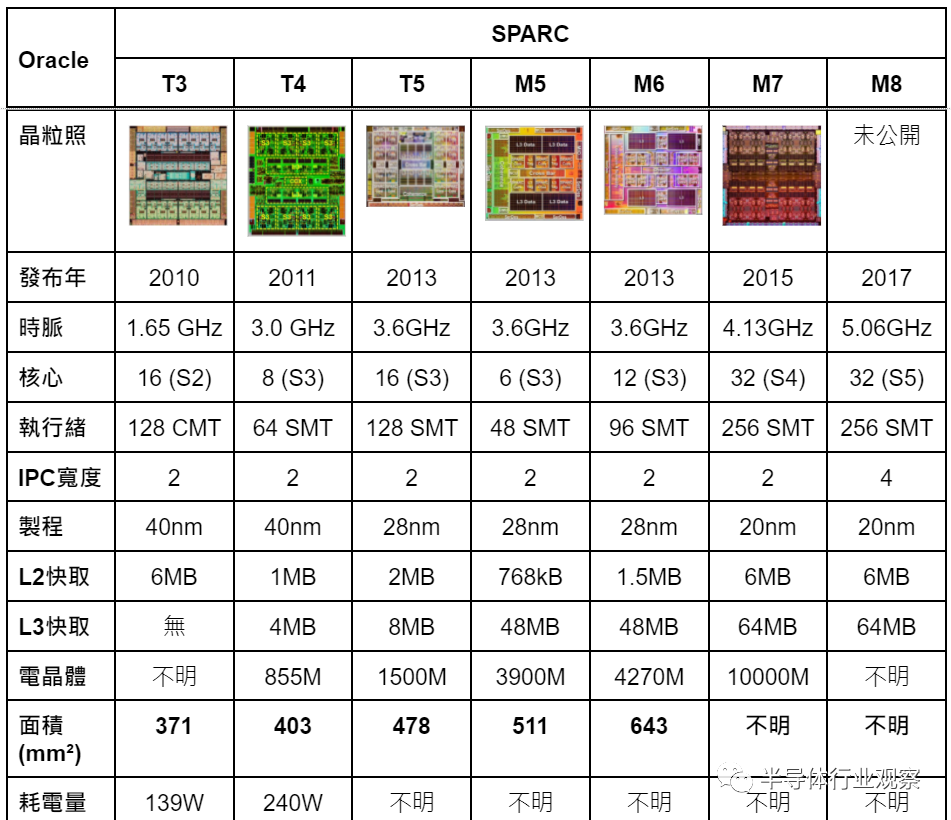

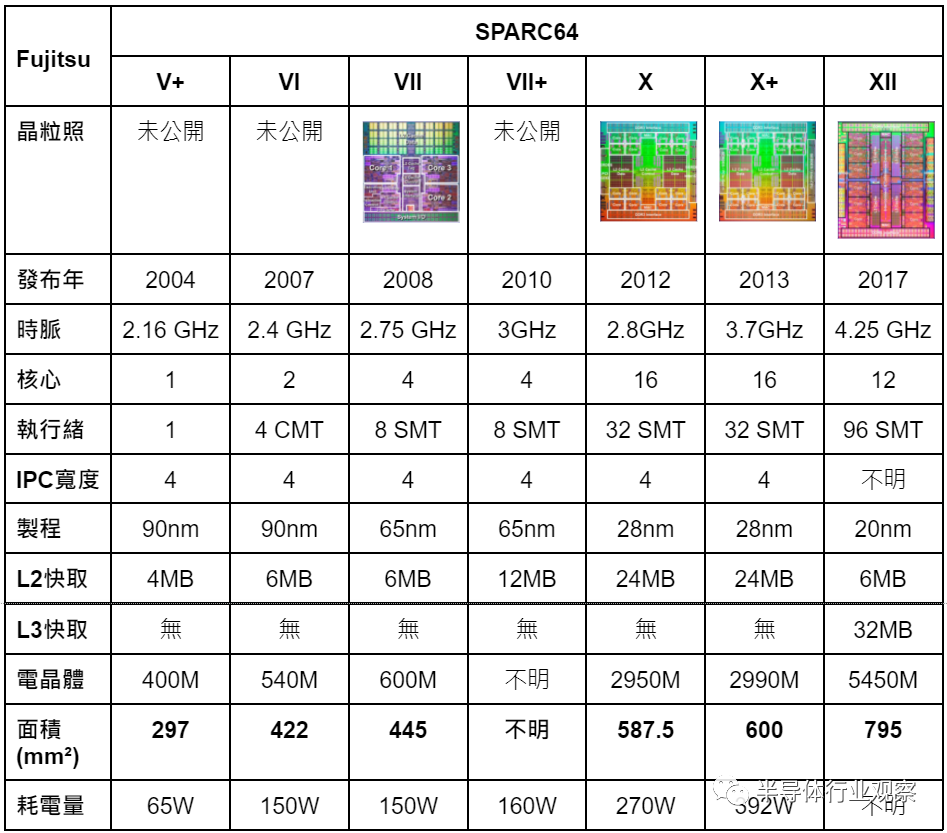

论打造巨无霸芯片,RISC诸神另一个苟延残喘……呃,硕果仅存的SPARC阵营,Fujitsu和并购Sun的甲骨文,和IBM相比可谓不遑多让,这次日本人还比美国人更猛。

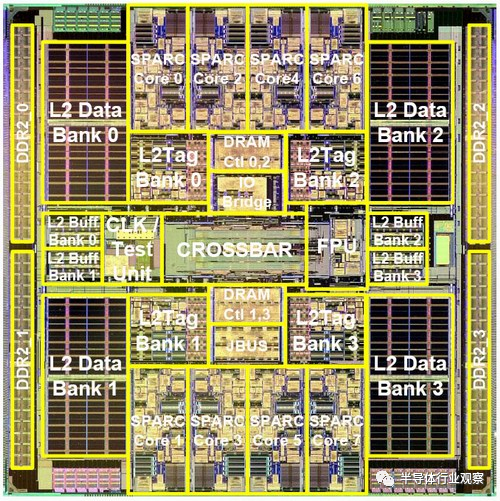

看了这么多美不胜收的晶粒图,当下做出「高阶处理器巨兽化的推手,容量快速膨胀的快取记忆体绝对当之无愧」结论并不太困难。但俗语说的好,条条道路通罗马,单一芯片狂堆多执行绪核心冲整体输出量,也是另一种增胖芯片面积的途径,而SPARC阵营双雄Fujitsu和甲骨文也就误打误撞走上这方向。

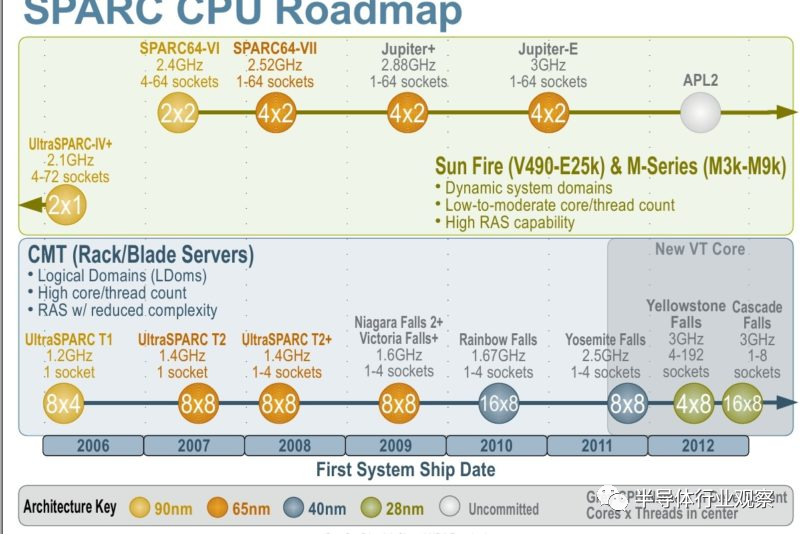

之前笔者须请各位再次复习Sun在2004年倡议的「Throughput Computing」,背后动机说穿了就是「英特尔和AMD像赛亚人借着互殴激增战斗力,老子无力陪你们玩了,干脆在多执行绪另辟蹊径,传统高效能竞技场就留给盟友Fujitsu伤脑筋吧」。关于SPARC处理器的发展历史与脉络,请各位多多参考笔者的旧文。

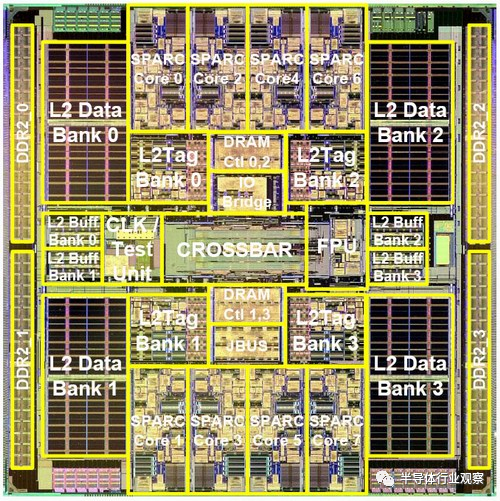

▲ Sun UltraSPARC T1「Niagara」(8核心32执行绪,面积340平方公厘,90纳米制程,3MB第二阶快取记忆体)。

照2004年6月Sun与Fujitsu正式宣布结盟的策略,这两间要「兄弟登山,各自努力」截长补短,一边「网站应用领域开辟多执行绪新蓝海」,另一边继续「坚守把RISC伺服器做得像大型主机可靠」。

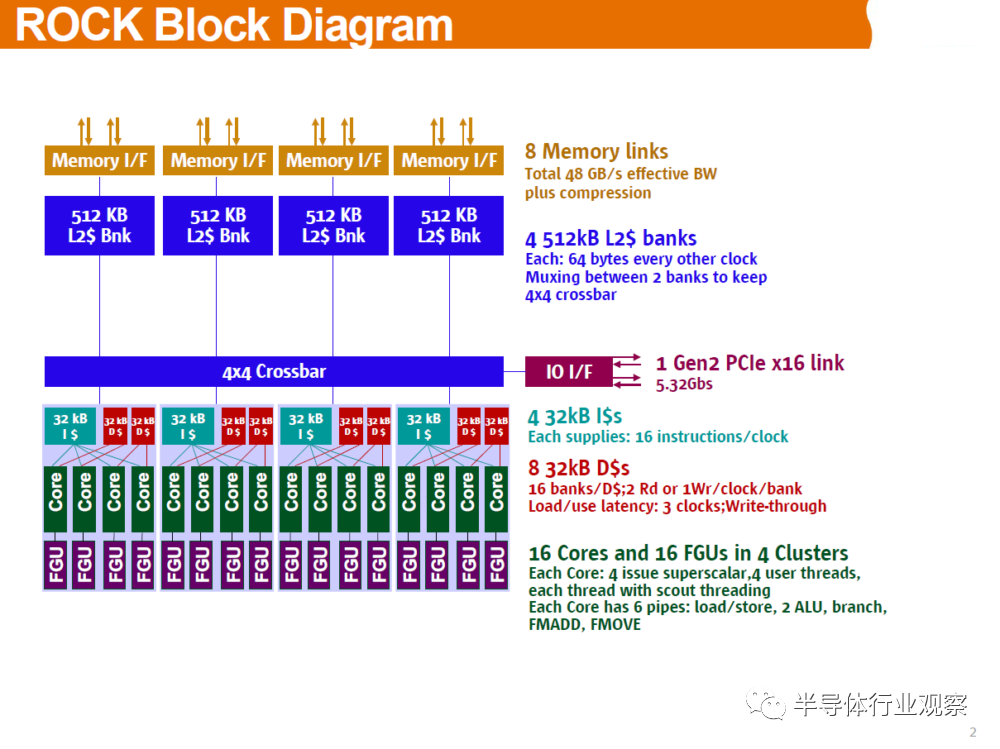

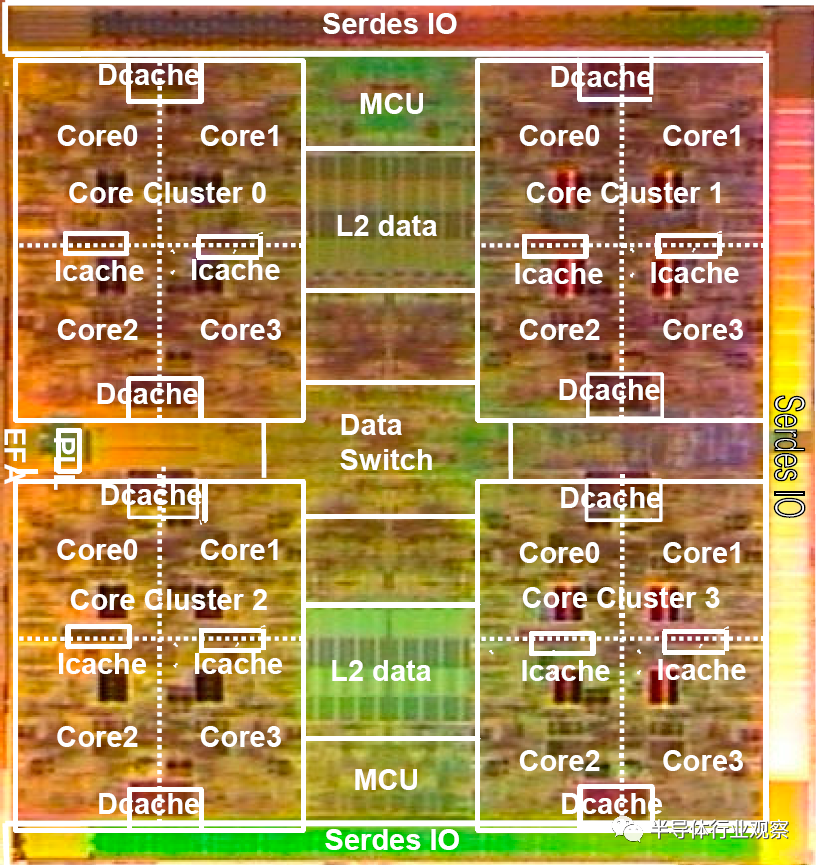

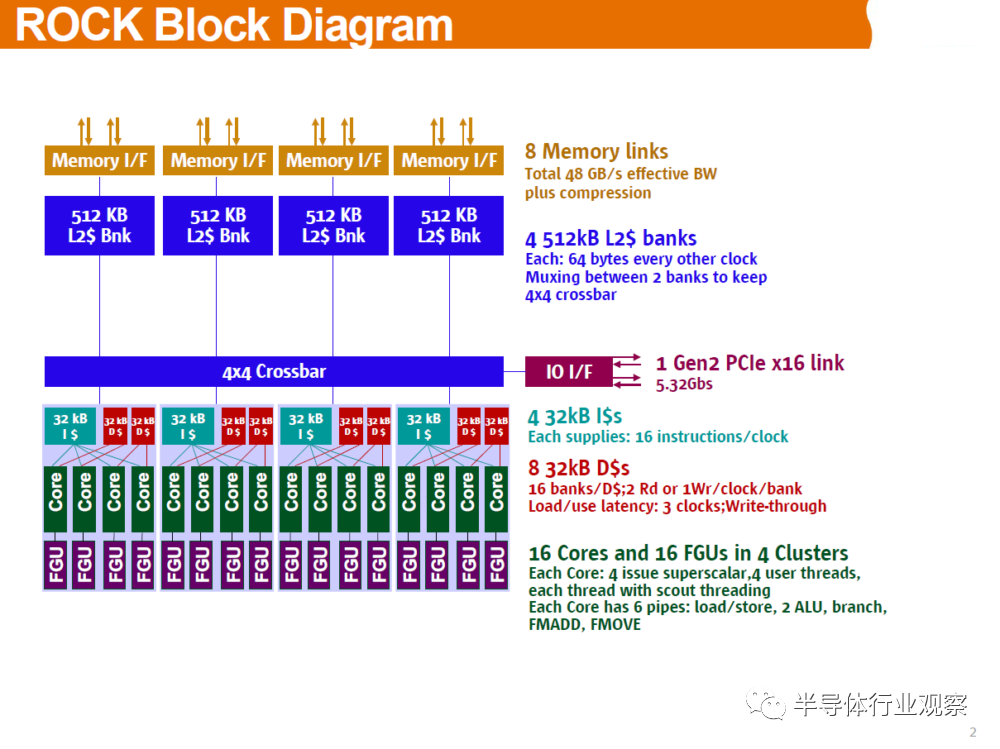

人算不如天算,Sun的UltraSPARC RK「Rock」,极具野心追求面面俱到的诉求,却让未来十几年SPARC处理器两边长得越来越像,唯一差别仅Fujitsu极度重视高效能运算市场,会弄出SPARC64的特化版。

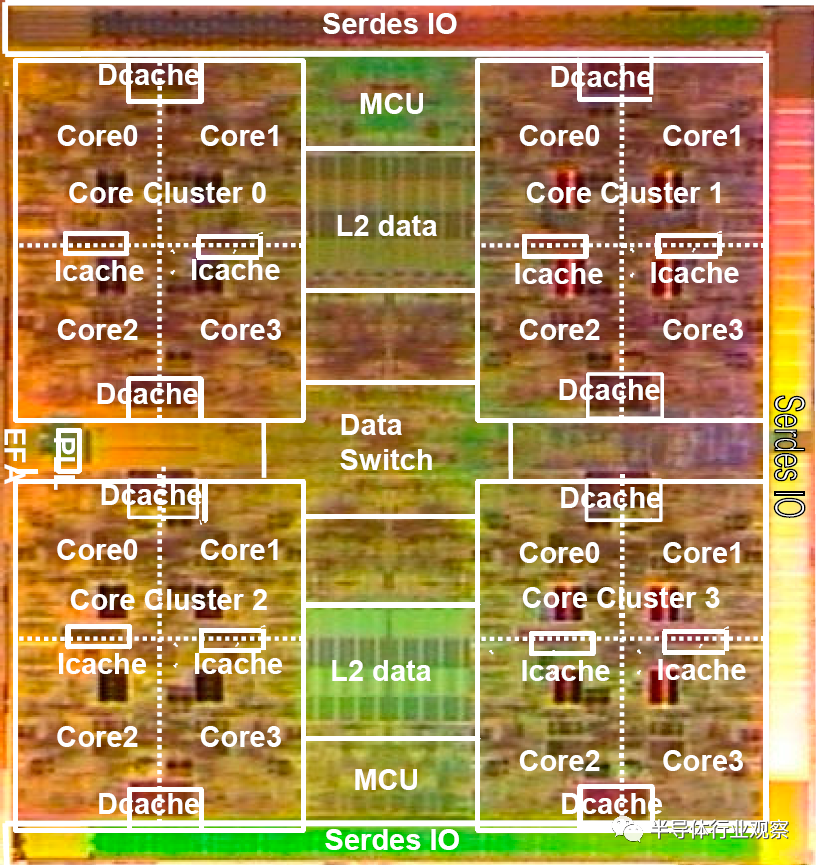

Sun 2005年揭露UltraSPARC RK时,对这颗兼具16个非循序执行(OOOE)且同时多执行绪(SMT)的怪物寄以厚望,虽然很可能因专案失控(还搞出2.0版)或250W高功耗,导致2010年被腰斩,但共享快取记忆体的核心丛集(Core Cluster)概念,确立后继Oracle SPARC处理器的「核心堆堆乐」。

▲ Sun UltraSPARC RK「Rock」(16核心32执行绪,面积396平方公厘,65纳米制程,2MB第二阶快取记忆体)。

到头来,SPARC M系列出现,也意味甲骨文想做Mission Critical的生意,正面跟盟友Fujitsu打对台。甲骨文2017年两次大裁员,砍光Solaris作业系统和SPARC处理器研发团队,直接宣判「Sun本家」SPARC处理器死刑,注定日后只剩Fujitsu孤独的走下去,也许看不到未来了也说不定。

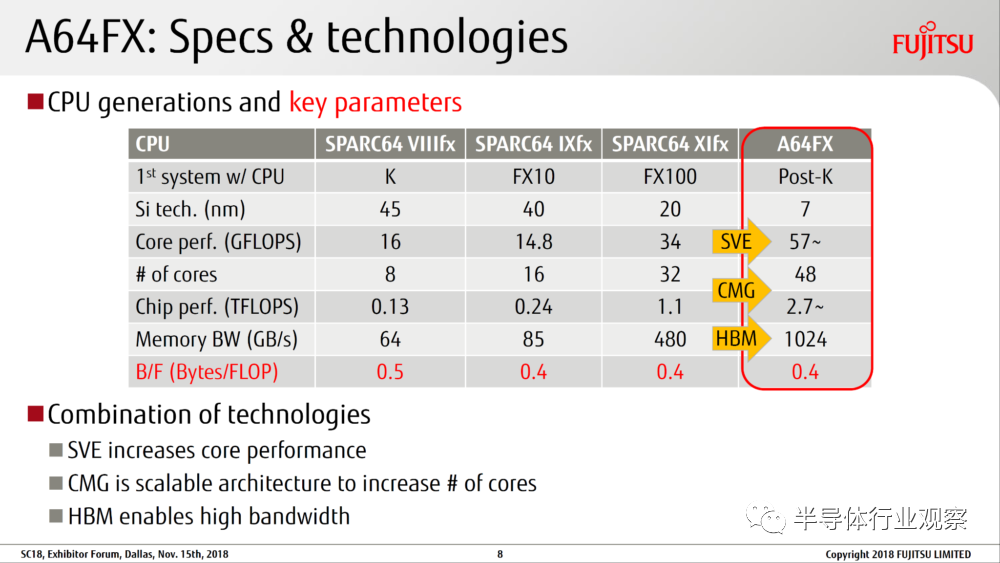

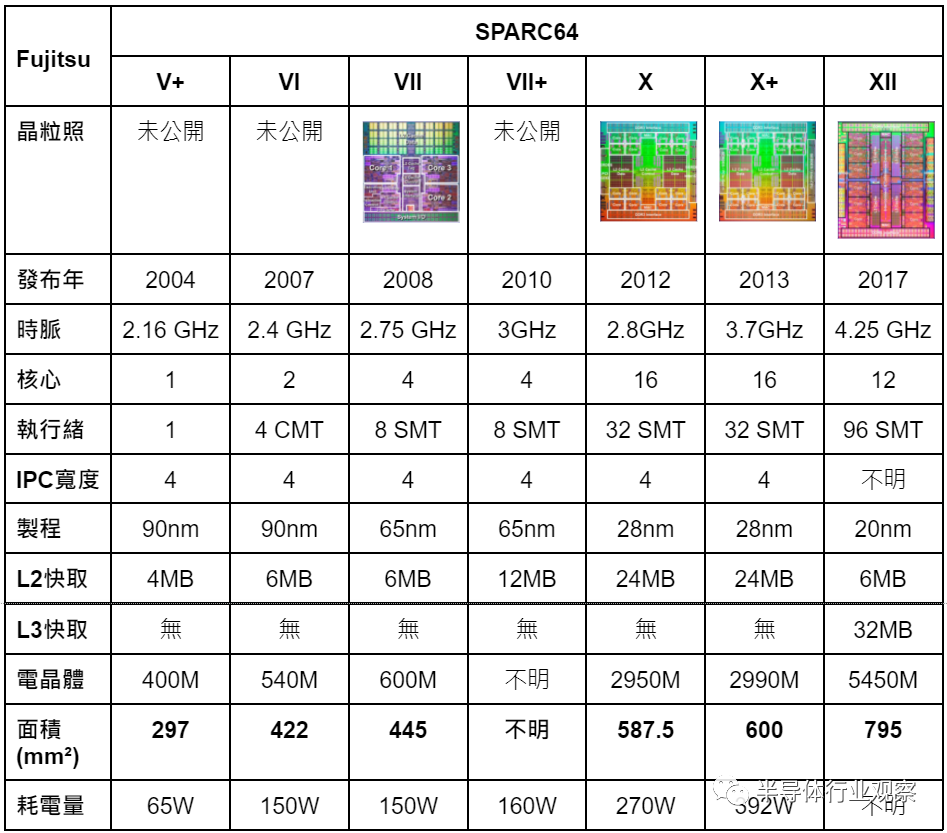

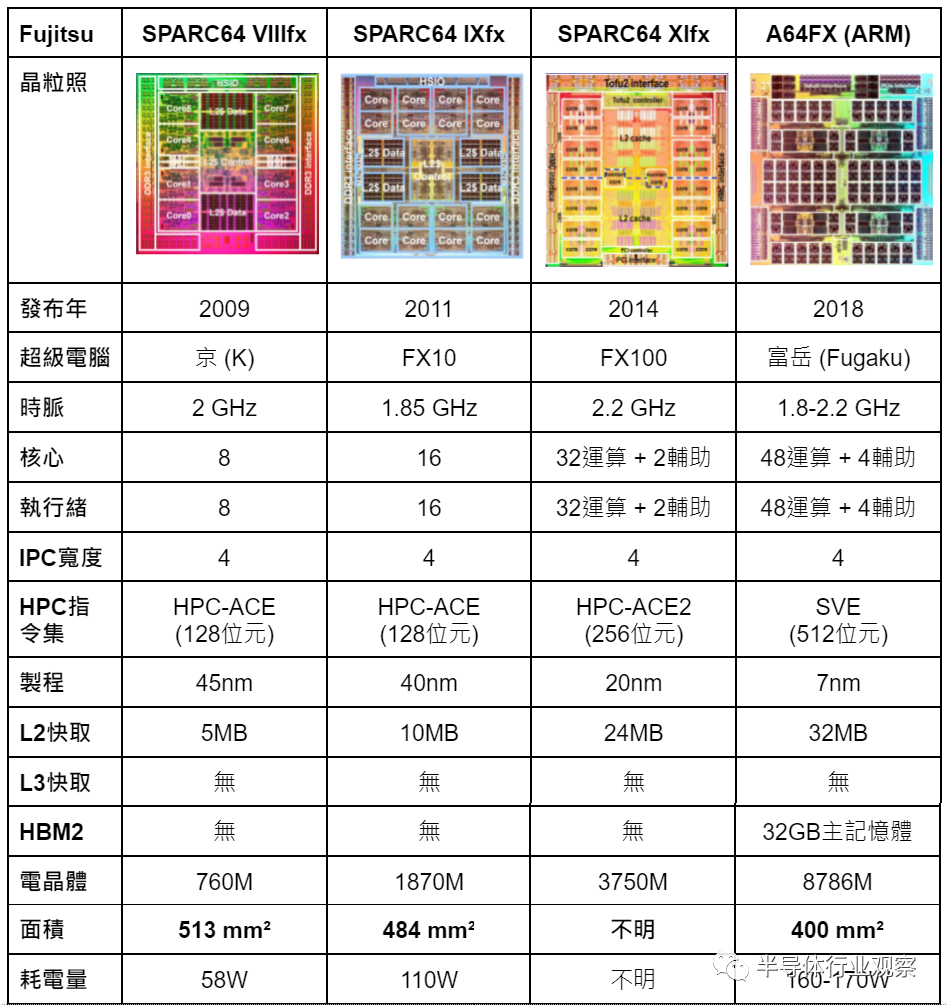

笔者花了不少时间整理Fujitsu SPARC64家族,这些年来「小步快跑」规格演进,看完后也只能感慨「结果大家都长得越来越像,当初说好的彼此互补呢」?

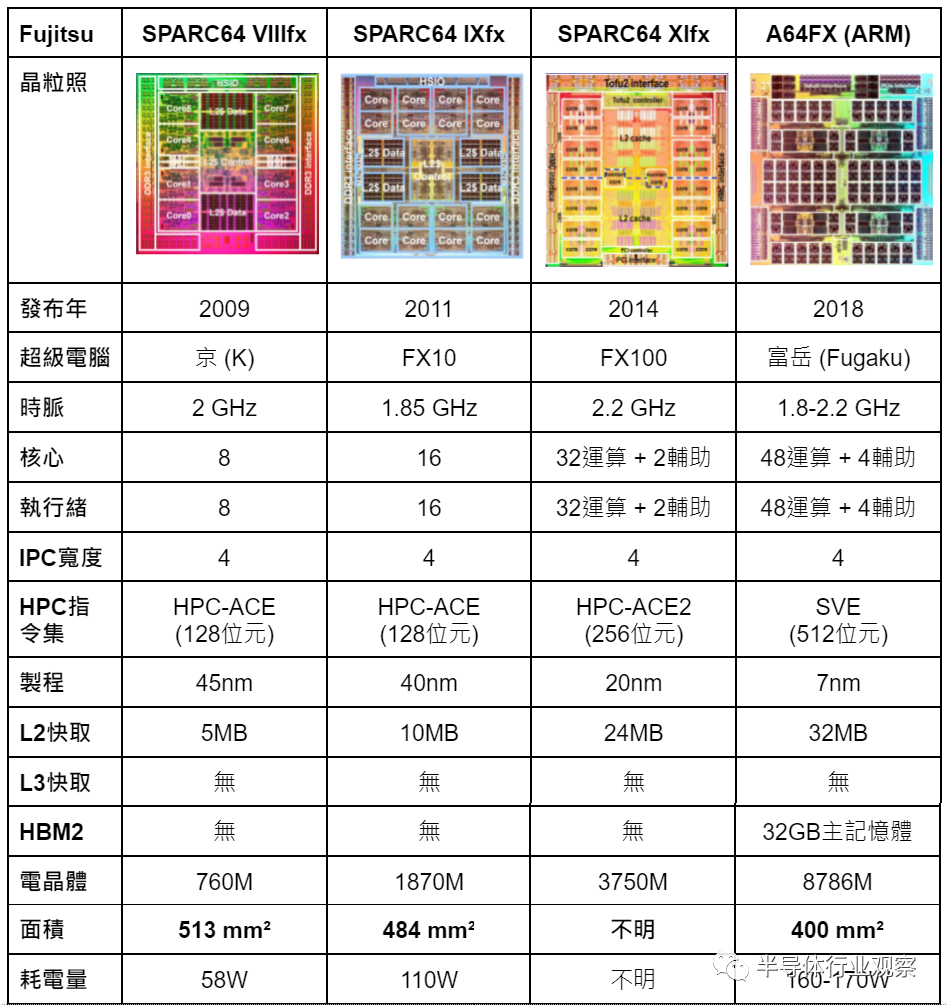

这些年来,先后靠着「京」(K)与「富岳」(Fugaku)称霸Top500的Fujitsu非常重视超级电脑市场,SPARC64自然也有针对高效能运算的特化版。从两者的差异性,各位或多或少也会感受到不同应用需求,是如何反应至这些处理器的规格。

Chiplet与先进封装技术会中止恐龙化CPU吗?

诸君,这些让人眼花撩乱的规格,一路看下来,看到头昏眼花了吗?没关系,就让我们回到本文起点:苹果M1 Max,再稍微分心到施展Chiplet策略四处攻城掠地的AMD,让大脑稍微冷却。

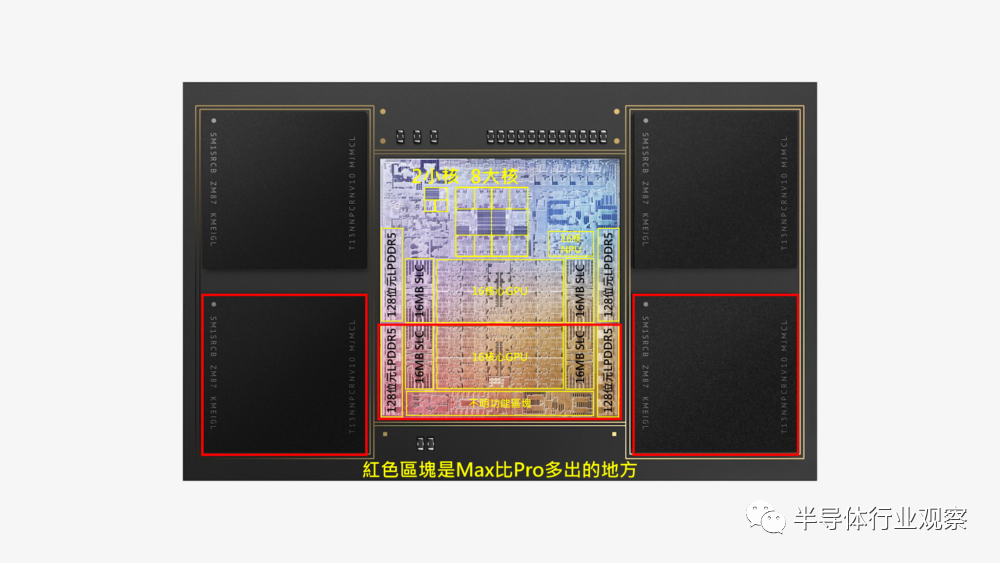

最近坊间小道消息又传出,苹果下一代iMac Pro可能采用怪物级芯片「M1 Max Duo」,由两个M1 Max组成,内建20核心CPU及最多64核心GPU,记忆体高达128GB,性能为目前芯片两倍。还有传闻指出,Mac Pro将推出采用四倍设计的「M1 Max Quadro」,意思就是包两颗不够,你可以包四颗。乍看之下似乎很像「多馅水饺」,也许M1 Max最底部那块神秘的「不明功能区块」,就是预留为连接多颗晶粒的超高速汇流排,要不然笔者左思右想,想破脑袋,也想不出其他更合理的解释了。

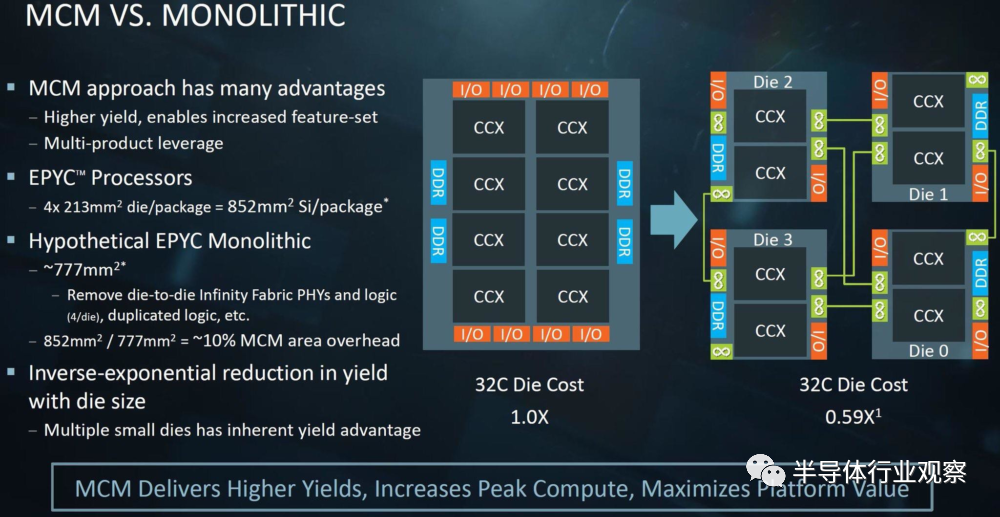

就现在业界风向看,除非像IBM和Fujitsu几乎完全不在乎成本和产能的玩法(反正羊毛就出在羊身上),看在先进制程产能大爆满的份上,Chiplet小芯片结合各式各样先进封装技术,几年内不太可能退流行,英特尔已确定将共襄盛举,一再创造恐龙级GPU体型纪录的Nvidia随之跟进也不是太让人意外的发展。过去十几年动辄500~600平方公厘或更大颗的单一晶粒CPU,以后恐怕只会越来越罕见。

但行文至此,笔者不得不感慨,英特尔21世纪初期让伺服器处理器走向大型化快取路线,并激增核心数,不断催生「天元突破」的晶粒面积。当时英特尔高层接受媒体访问时(记得还是CNET)直言「大型化芯片有助消化过剩产能,有益无害」。现在英特尔人回顾这段话,绝对笑不出来,因为时下靠核心数和快取记忆体容量活活压死他们的就是AMD,还是采取「先讲求不伤身体,再讲求效果」的方法,令人不胜唏嘘。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2885内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie