Apple M1 Ultra 芯片互连背后的技术

来源:内容由半导体行业观察(ID:icbank) 编译自 tomshardware ,谢谢

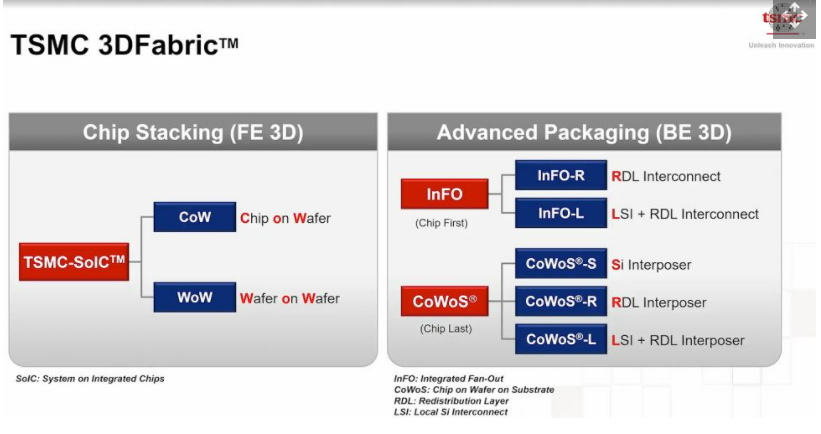

幸运的是,非官方消息来源没有苹果那么神秘,并且能够挖掘出有关苹果 UltraFusion 处理器间互连的更多细节,该处理器提供 2.5 TB/s 的带宽。 有媒体报道称,Apple 的 M1 Ultra 处理器使用TSMC的CoWoS-S(带有硅中介层的芯片上晶圆基板)基于2.5D中介层的封装工艺来构建M1 Ultra。AMD、Nvidia和富士通等公司使用类似的技术来构建用于数据中心和高性能计算 (HPC) 的高性能处理器。

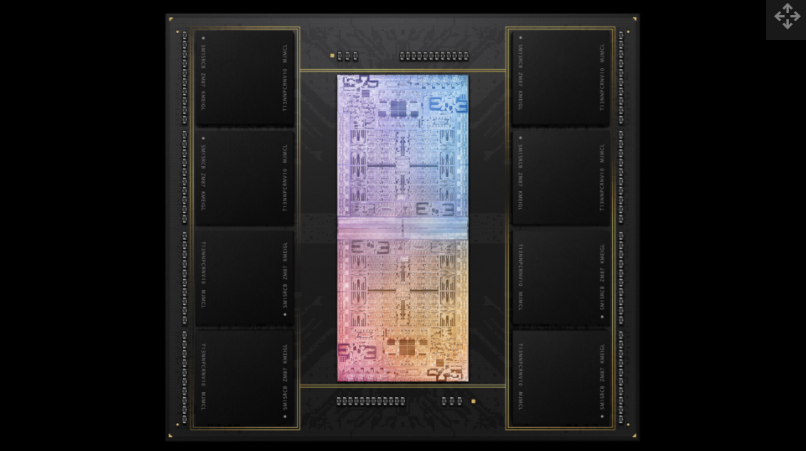

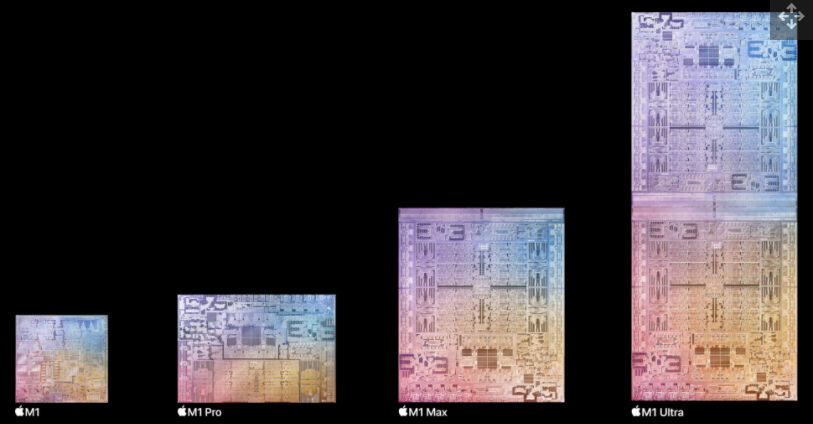

Apple 的 M1 Ultra 无疑是一个强大的设计。每个M1 Max SoC 的裸片尺寸为432mm²,因此M1Ultra使用的中介层必须超过860mm²。这是相当大的,但并非闻所未闻。AMD 和 Nvidia 使用更大的中介层,其计算 GPU 具有高带宽内存。

请记住,Apple 展示了带有大型 I/O 焊盘的 M1 Max die shot,类似于旨在连接到中间芯片的本地互连,因此许多人认为Apple 使用了 InFO_LSI 也就不足为奇了。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2977内容,欢迎关注。

推荐阅读

★

苹果发布1140亿晶体管M1 Ultra:12年自研34颗处理器

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 当我拿出 4 卡 GPU 测试 Ansys 流体仿真,阁下该如何应对?

- 2 英飞凌2024汽车创新峰会:揭秘全球汽车芯片No.1供应商的创新与布局

- 3 收购GaN Systems后,英飞凌氮化镓迎来新突破

- 4 ADI携4大产品线亮相上海慕展,引领智能边缘行业新升级

- 5 迈来芯亮相上海慕展,解析技术创新布局与中国本土化战略