Apple 的 M1 Ultra,究竟用的InFO还是 CoWoS?

供稿人:TechInsights 名誉研究员 Dick James

3 月 8 日,Apple 举行了“Peek Performance”活动,介绍了全新的 Mac Studio,其中包括 M1 Ultra 处理器及其独特的(迄今为止)包装。事件发生后,我们在博客中推测,Apple 使用了台积电的 InFO_LSI(或 CoWoS-L)硅桥,这是其 3D-Fabric 技术的一部分。

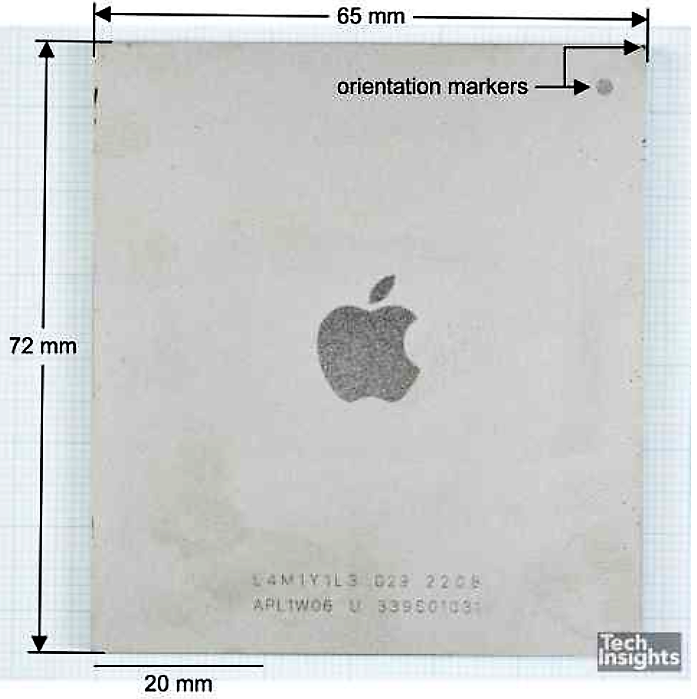

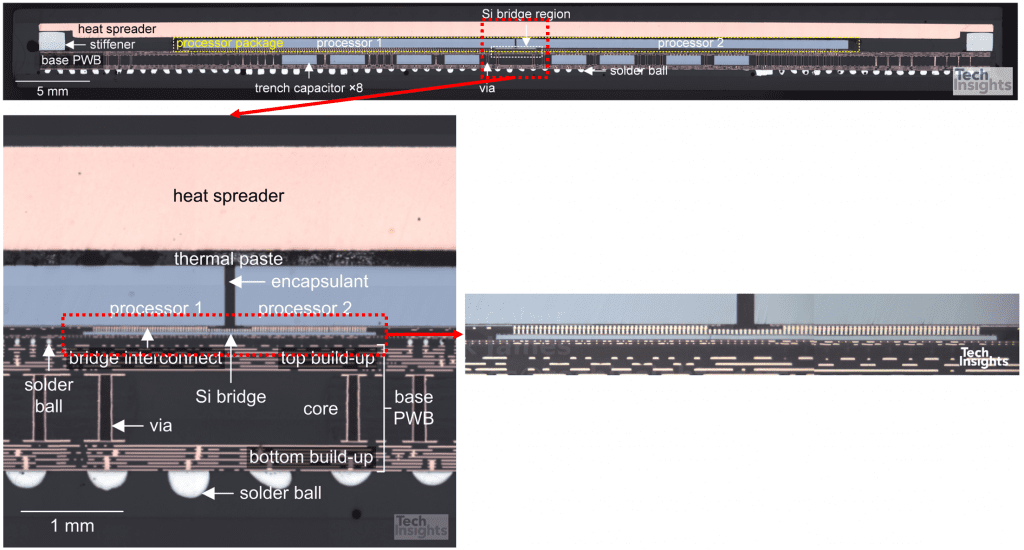

最近,TechInsights 发布了他们的Advanced Packaging Quick Look 报告,确认使用了硅桥而不是完整的中介层。正如预期的那样,封装很大,为 65 x 72 毫米:

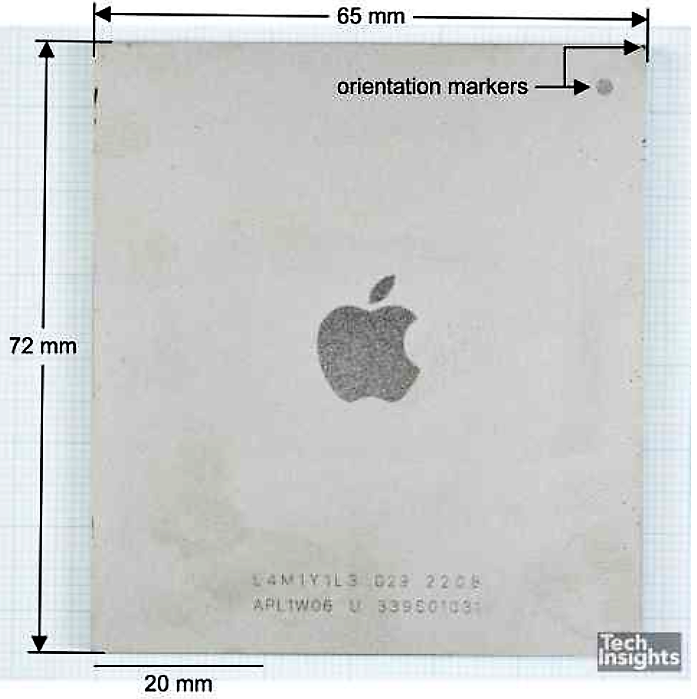

而且,如果我们取下盖子,它与 Apple 的描述相符:

在 Apple 活动中,Johny Srouji(Apple 硬件技术高级副总裁)表示:“M1 Ultra 是 Apple 芯片的又一个游戏规则改变者,它将再次震撼 PC 行业。通过将两个 M1 Max 芯片与我们的 UltraFusion 封装架构相连接,我们能够将 Apple 芯片扩展到前所未有的新高度。” 他接着说:“UltraFusion 架构使用的硅中介层,其连接密度是任何可用技术的两倍”。

当时我们认为完整的中介层裸片不太可能,因为即使裸片边缘接触裸片边缘,台积电 CoWoS 样式的中介层也至少为 840 mm 2。那是很多硅,(即费用),所以现在我们有了英特尔的 EMIB等桥接技术,这似乎更有可能。

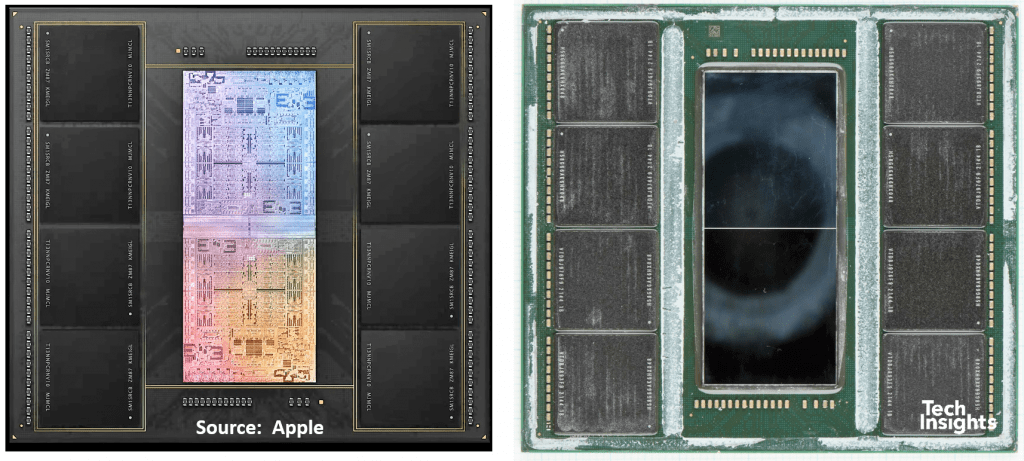

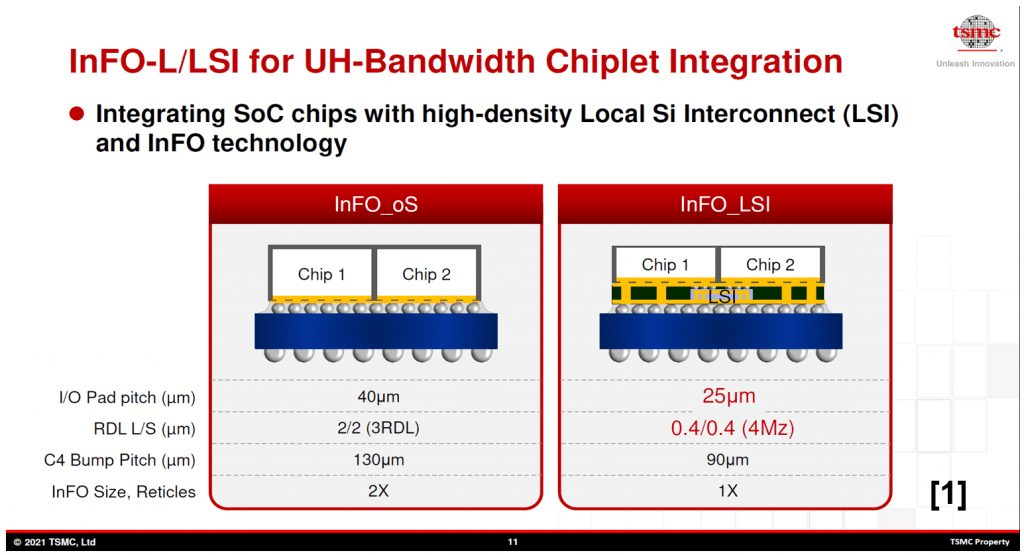

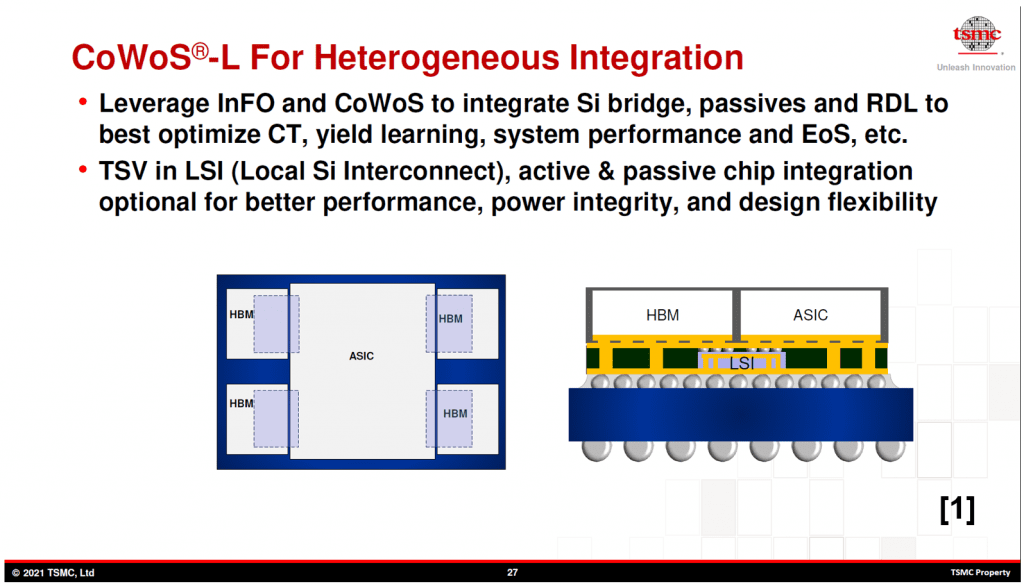

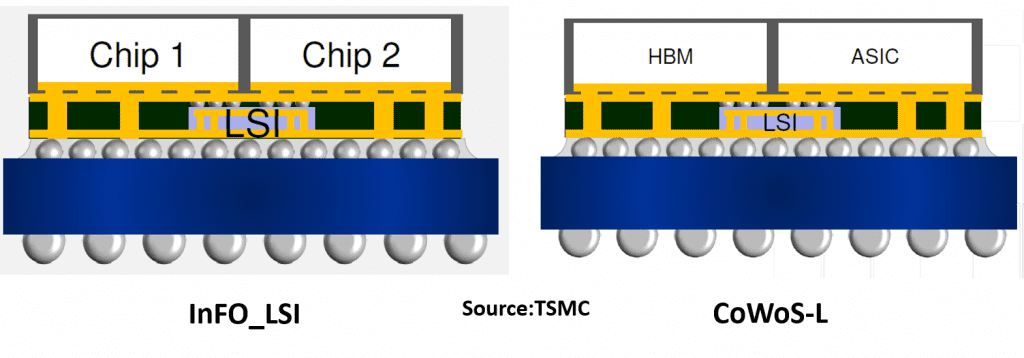

台积电宣布了两个版本的硅桥技术,InFO_LSI 和 CoWoS-L。

在我看来,它们看起来一样:

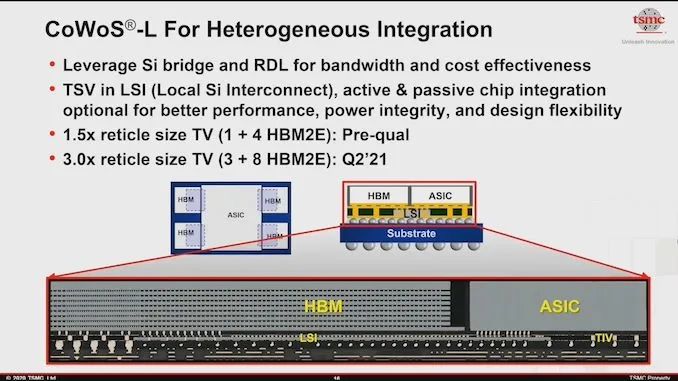

在这些示意图中,看起来桥芯片嵌入在有机基板的核心中。但如果我们看看一年前在 2020 年技术研讨会上展示的内容,我们会看到一些不同的东西:

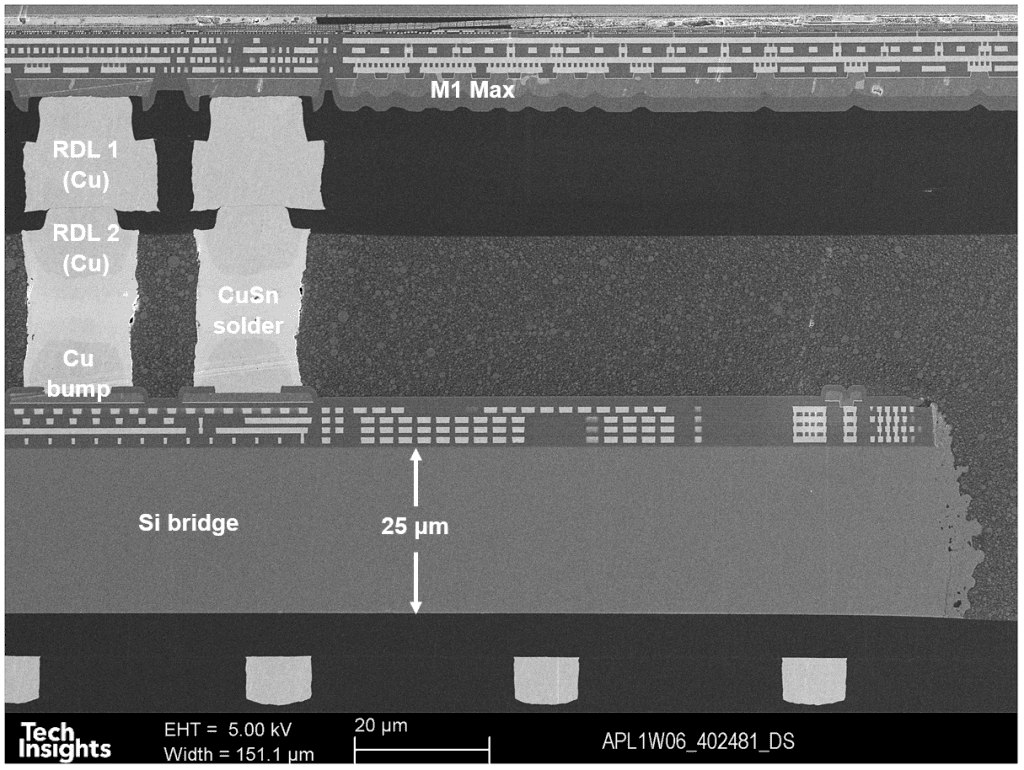

在 SEM 图像中,看起来 LSI 桥芯片位于基板中的堆积层之上,尽管上面的示意图显示它嵌入在核心中。

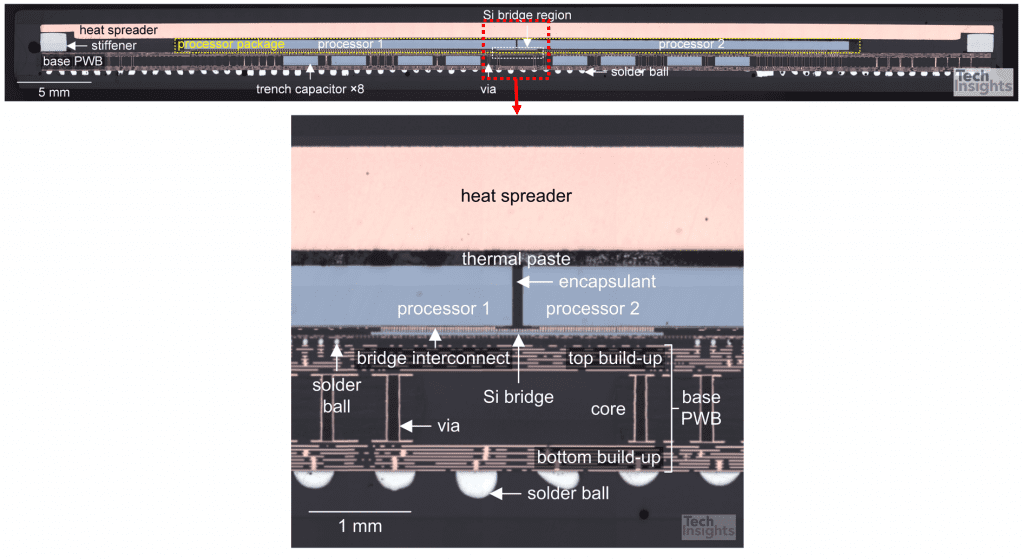

M1 Ultra 看起来很相似,但没有涉及 HBM:

内核中嵌入了裸片,但它们是沟槽电容器裸片。基板本身相当复杂,每侧有九个堆积层,由激光通孔连接,大通孔钻穿核心。

桥接芯片为 18.8 x 2.88 毫米,略短于 M1Max 芯片的 19.05 毫米宽度。

如之前的博客所述,凸块焊盘间距为 25 x 35 μm,芯片上可能总共有 57,000 个焊盘,尽管 Apple 只提到了 10,000 个 I/O(20,000 个焊盘)。

该芯片的厚度约为 25 μm,有五个金属层,并通过焊料 微凸块和两个再分布层 (RDL) 连接到处理器。

我不确定我们是否可以将此应用程序称为 InFO_LSI 或 CoWoS-L,但无论哪种方式,它都是第一个使用台积电硅桥技术的量产产品——苹果创新封装的另一个例子!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3109内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 当我拿出 4 卡 GPU 测试 Ansys 流体仿真,阁下该如何应对?

- 2 英飞凌2024汽车创新峰会:揭秘全球汽车芯片No.1供应商的创新与布局

- 3 收购GaN Systems后,英飞凌氮化镓迎来新突破

- 4 ADI携4大产品线亮相上海慕展,引领智能边缘行业新升级

- 5 迈来芯亮相上海慕展,解析技术创新布局与中国本土化战略