IMEC:SoC发展的另一个新方向

IMEC举办了新闻发布会及其未来峰会,来探讨未来消费和工业产品的技术发展。该峰会讨论了许多与健康相关的发展,包括神经科学、健康传感器以及固态电池,以支持下一代物联网设备。他们还积极与ASML公司合作,开发更高吞吐量的EUV技术,以实现精细半导体器件的设计。在这里,我们将集中讨论可能影响未来内存和存储技术的发展。

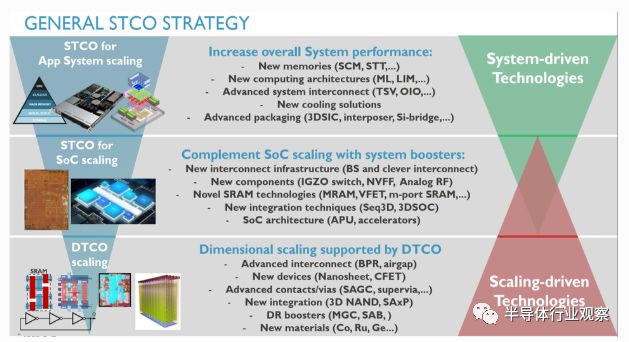

我们最近写过关于异构芯片设计(包括3D结构)的发展。来自IMEC的Julien Ryckaert谈到了逻辑缩放,他所讨论的原理将影响未来的固态存储器。其中,系统技术协同优化(STCO)的概念被视为是可以实现更高密度SoC设计的重要方法。

(IEMC对系统技术协同优化(STCO)的看法 来自IMEC演示文稿的图片)

STCO使用了混合半导体技术,并超越了今天的FinFET。它采用了所谓的"nanosheets"和"forksheets"的新技术,能够使功能器件的最小特征宽度小于5nm。下图显示了系统级的缩放工作,以及它如何与设备级别的缩放进行交互,以创建新类型的内存、互连和逻辑。

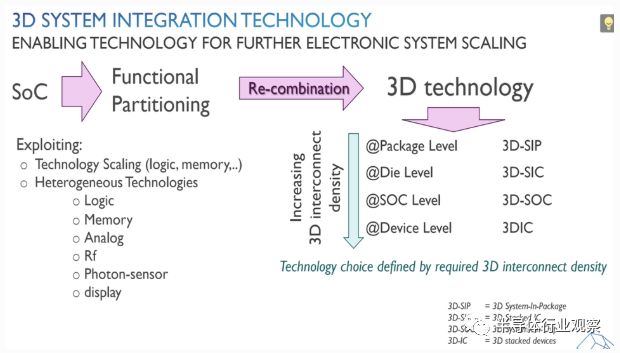

下图给出了不同层次的3D半导体设计视图,这是IMEC研究员、3D项目主管Eric Beyne提供的。SOC可以分解成功能分区,这些部件可以在不同的封装级别中组合成3D结构。

(imec对3D系统集成的看法 来自IMEC演示文稿的图片)

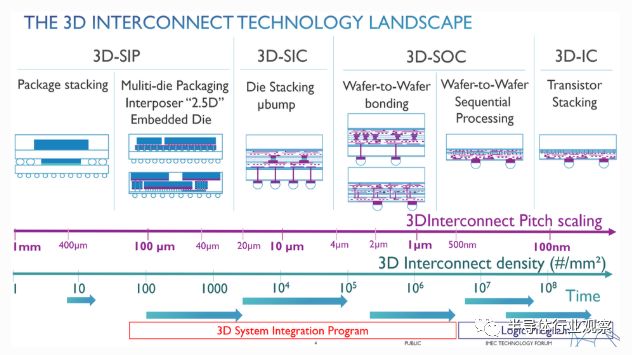

在下图中,我们看到了对互连间距和密度的要求,以实现这些不同的3D结构。所有这些方面的工作都在进行,从左到右,3D集成变得越来越困难。

(3D半导体集成技术 来自IMEC演示文稿的图片)

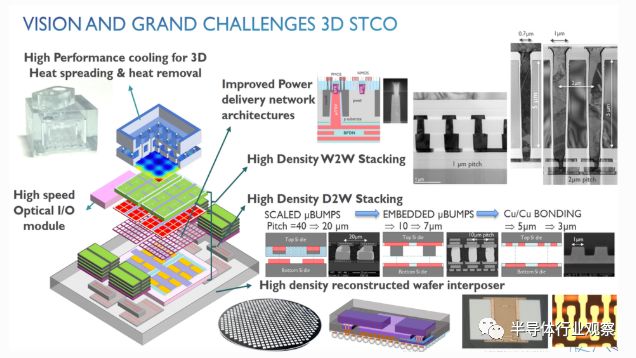

晶圆与晶圆键合以及将一些处理移至晶圆背面进行,是实现更高密度集成的一种途径。正在进行工作是为了将1微米以及更小的间距成为可能。在这样的器件密度下,也会推动散热技术的发展。2D多核处理器芯片将逐渐被3D功能分区所取代,其最终目标是实现3D系统集成。下图显示了高集成度下的一些挑战。

(3D STCO的挑战 来自IMEC演示文稿的图片)

IMEC详细介绍了半导体器件和系统设计的未来发展方向。新的扩展方法将影响SoC器件的设计以及未来的固态存储器和存储。

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 MediaTek举办天玑开发者大会MDDC2024,携手产业伙伴共创生成式AI新生态

- 2 蓝牙技术联盟发布《2024年蓝牙市场最新资讯》

- 3 英飞凌推出用于Arduino的XENSIV传感器扩展板, 搭载英飞凌和Sensirion的智能家居应用传感器

- 4 一文看懂封装基板