英特尔在研究哪些“超”前沿新技术?

2023-12-15

22:18:51

来源: 杜芹

点击

在英特尔内部有这样一个组织,他们致力于前沿技术的研发,应变硅、Hi-K金属栅极、FinFET等技术均是出自他们之手。他们就是——英特尔组件研究团队,是英特尔技术开发(Technology Development, TD)部门内的一个研究组织。在摩尔定律即将走到极限的时刻,这个组织又在进行哪些研究?

作为IEDM的“常客”,英特尔近日在IEDM上展示了一些新技术突破。

背面供电:超越PowerVia

英特尔是较早进行背面供电技术的芯片公司之一。

说到背面供电技术出现的契机,就不得不谈及芯片互连的瓶颈。随着摩尔定律推动晶体管密度的不断增加,传统的芯片设计面临了严重的互连瓶颈。在有限的空间内,为了满足日益增长的性能需求,传统的面向上(front-side)供电和信号传输设计开始显得不足。

为了优化芯片的性能,尤其是减少电阻和电容的影响,需要一种新的设计方法。背面供电技术提供了一种有效的解决方案,能够分离供电和信号传输路径,从而减少这两者之间的互相干扰。

英特尔的PowerVia背面供电技术有效地解决了上述挑战。通过在晶体管的背面实现供电,PowerVia技术使得晶体管的两侧均能实现互连,并通过垂直连接实现两层互连间的通信。这种设计允许将背面互连专用于供电,使用大截面、低电阻的导线,而将前面的互连主要用于信号传输。这样,每个互连层可以针对其主要功能进行优化,无需在供电和信号传输之间做出妥协。

将供电线路从芯片的前部转移到背部,不仅提升了芯片的性能,而且为前部互连释放了空间,减少了工艺复杂性和成本。这种分离导线的方法提供了显著的性能提升,并有助于进一步的微型化发展。英特尔的PowerVia技术将于明年生产准备就绪。

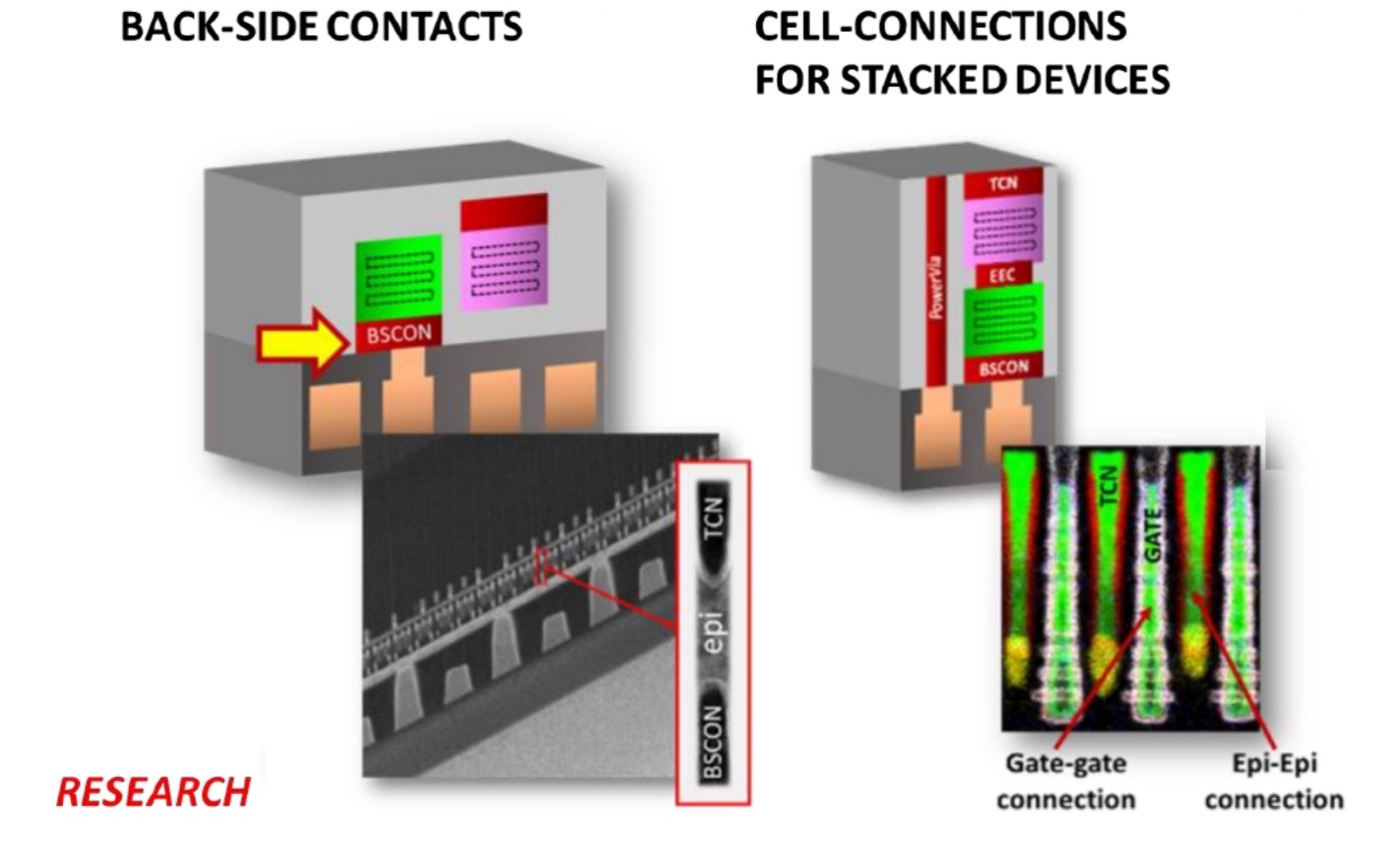

而现在,英特尔组件研究团队已经开始着手研究超越PowerVia的未来技术。如下图所示,英特尔引入了一项创新技术——背面触点。这项技术的引入标志着英特尔在单层器件设计上的一次重大突破,允许单个晶体管层从上、下或同时从两侧进行连接。

背面触点的主要作用是通过背面的大截面导线直接向晶体管供电,从而绕过传统的电路路径,显著提高了供电效率。这种设计的直接好处包括减少了单元内的金属使用量,降低了电容和寄生电容效应,从而提高了开关速度并减少了功耗。此外,由于无需为PowerVia预留额外空间,能够在相同的芯片面积内实现更紧密的组件布局,进而增加了晶体管密度。

值得一提的是,该背面触点技术可以与 PowerVia一起部署,也可以单独部署。通过透射电子显微镜(TEM)图像分析,可以观察到英特尔已经有能力制造出对称的背面触点。背面触点从顶部和底部看起来非常相似,而英特尔将在 IEDM 2023上展示的电性能表现表明,这种背面触点不仅在几何形状上非常相似,而且在电性能表现上也非常相似。

背面触点技术与PowerVia渴望在堆叠技术上发挥关键作用。晶体管堆叠技术是微电子行业的一项重要创新,它致力于在单位面积上增加晶体管数量。这种技术通过在PMOS晶体管上叠加NMOS晶体管,创造出新的拓扑结构,以实现更高的芯片性能和密度。晶体管堆叠的一个核心挑战是如何同时为堆叠层的顶部和底部晶体管提供电力和信号。而这两种技术共同为晶体管堆叠提供了高效的能源和信号分配。

在当下的芯片设计中,散热成为芯片工作者的一大难题。英特尔已经证明,PowerVia技术在同等功率密度下,其热性能和响应与传统的非背面供电设计基本一致。此外,研究表明,使用背面触点技术不会对热性能造成负面影响,这一发现对于确保芯片在高性能操作下的稳定性至关重要。

总之,通过创新的互连解决方案,英特尔正推动晶体管技术向更高的性能和密度迈进。

3D堆叠架构:超越RibbonFET

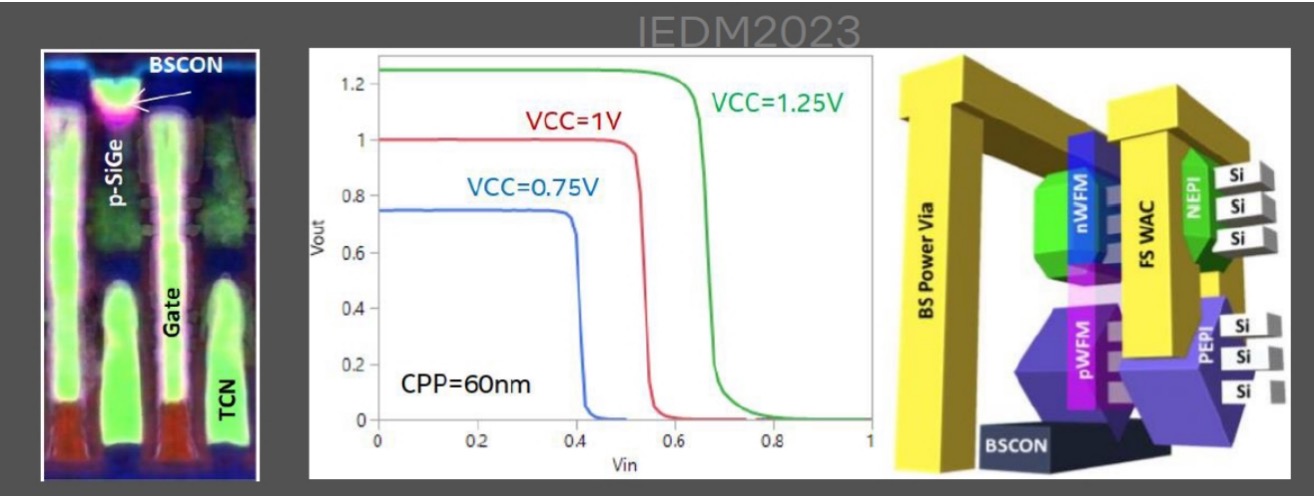

CFET或3D晶体管堆叠被认为是下一代晶体管缩放的主流架构。在3D堆叠结构领域,我们都知道,英特尔提出了RibbonFET技术,在2023的IEDM上,英特尔组件研究团队展示了其在晶体管尺寸缩减架构方面的最新进展,超越了RibbonFET技术。

为了推动晶体管的尺寸缩减,英特尔在2023年成功地将单片式NMOS和PMOS结合在一起,并通过PowerVia和直接背面设备接触,展示了在单个鳍片和多晶硅层上的紧凑型反相器设计,并在多晶硅层实现了60纳米的接触间距。这表明,通过这些技术,英特尔正在推动晶体管技术向更小尺寸的发展,同时保持高性能和集成度。

上图右侧描述了英特尔构建的结构类型

这些成果标志着英特尔在晶体管技术方面取得了显著的进步,特别是在提高集成电路的密度和减小晶体管尺寸方面。通过这种创新的3D堆叠技术,英特尔在推动电子器件向更高性能和更小尺寸发展的道路上迈出了坚实的一步。

材料创新:超越硅边界

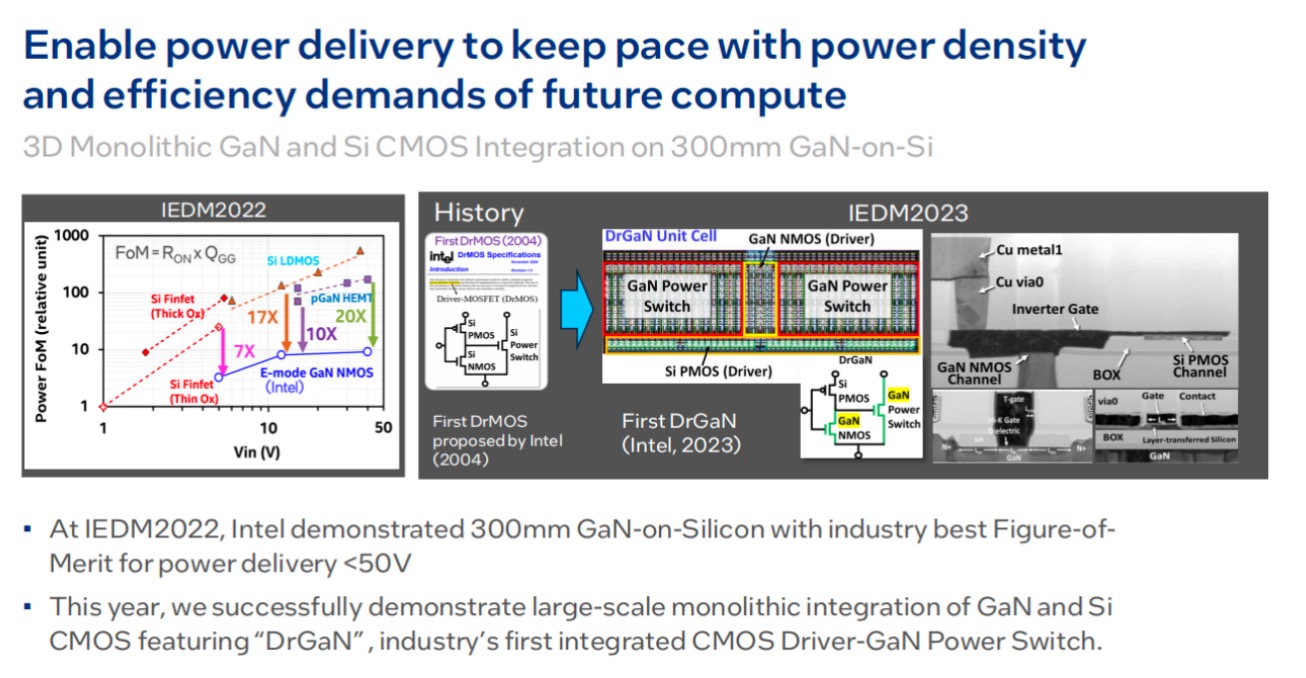

随着科技发展,对于更高的功率密度和能源效率提出了新的要求,特别是在5G和电源领域。在去年的IEDM 2022上,不仅为300毫米硅基氮化镓晶圆的制造开辟了新路径,而且在功率传输效率上取得了历史性的突破,实现了比行业标准高出20倍的增益,并刷新了高性能供电的记录。

今年,英特尔再次推进界限,展示了一种大规模的3D单片工艺,这项工艺巧妙地将氮化镓和硅CMOS技术融合在一起,采用了称为“层转移”的技术在300毫米硅晶圆上完成。这项技术,被称为“DrGaN”,标志着CMOS驱动器与氮化镓功率器件集成的新时代。

早在2004年,英特尔首次提出了DrMOS概念,即将CMOS驱动器与硅功率器件集成。这个当时的先锋想法,如今已经成为个人电脑和数据中心供电的行业标准,并在市场中广泛传播。这种集成技术通过减少寄生参数,提供了更高的功率密度解决方案,从而使硅晶体管能够提供更高效的供电解决方案。

氮化镓功率器件是近年来才兴起的新型半导体材料,由于其卓越的电气性能,迅速成为行业的焦点。直到去年,英特尔才发布具有20倍优势的氮化镓功率器件。更为突出的是,英特尔实现了将氮化镓和硅CMOS技术在同一晶圆上进行3D单片集成的里程碑。

英特尔坚信,通过DrGaN集成,未来计算的功率密度和效率需求将得到满足。这一信念基于氮化镓晶体管固有的优势,能够在不牺牲性能的前提下,提供更高的功率密度和更优的能效。从DrMOS到DrGaN,英特尔展示了其在行业中的领导地位和对技术进步的深刻理解。

结语

在摩尔定律挑战的边缘,英特尔组件研究团队再次展现了其对半导体行业不懈追求的承诺。他们所追求的,不仅是解决当前的技术挑战,而是提前预见并主导下一代计算的未来。英特尔的这一系列创新不仅仅是技术的飞跃,更代表了一种无畏探索未知、永不满足的精神,一种将理论变为可触碰实践的勇气,以及对半导体未来美好愿景的坚定信念。

附:英特尔在2023 IEDM发布的前沿技术论文包括:

【1】 《通过背面供电和3D堆叠实现面向未来制程节点的技术创新》(Process Innovations for Future Technology Nodes with Back Side Power Delivery and 3D Device Stacking)

【2】 《60 纳米栅极间距堆叠式 CMOS 逆变器的实现,结合PowerVia和直接背面触点技术》(Demonstration of a Stacked CMOS Inverter at 60nm Gate Pitch with Power Via and Direct Backside Device Contacts)

【3】 《DrGaN:采用E模式GaN MOSHEMT和三维单片硅 PMOS的300mm硅基GaN功率开关集成CMOS驱动器技术》(DrGaN : an Integrated CMOS Driver GaN Power Switch Technology on 300mm GaN on Silicon with E mode GaN MOSHEMT and 3D Monolithic Si PMOS)

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英特尔重磅发布OPS 2.0,智能教育时代加速到来

- 2 MediaTek天玑汽车平台推动汽车产业加速迈入AI时代,3nm旗舰座舱平台亮相

- 3 广东场效应半导体,二十多年坚持做一件事

- 4 国内首颗,精准纠错!德明利TWSC2985系列:支持4K LDPC技术的存储芯片