分析机构:台积电们或在三年后赶超英特尔!

来源:内容来自钜亨网,谢谢。

科技业分析公司Linley Group 在最新的微处理器报告(Microprocessor Report) 中指出,英特尔长期以来领先的芯片制造技术优势「正在消失」,而在开发新制程也处于落后阶段,台积电、三星和格芯有可能在2021 年时超越英特尔。

Linley Group的首席分析师Linley Gwennap写道,英特尔在「10纳米制程」技术发展一再延误,在下一代芯片制程进度上落后给全球最大晶圆代工厂台积电、半导体龙头三星电子( 005930-KR )与第二大晶圆代工厂格芯半导体。

这三家厂商为英特尔竞争对手提供芯片,如高通以及苹果,所以这不仅仅市场技术战争,也是销售战争,将影响到英特尔的芯片销售,冲击该公司营收。

Gwennap 在报告中仔细分析各家厂商生产的芯片电路「密度」,以及谨慎分析其他工艺技术指标,他的结论为,虽然各种技术之间的命名存在着差异,但竞争对手确实正在缩小与英特尔之间的差距。

举例来说,Gwennap 指出,台积电、三星与格芯的7 纳米制程,与英特尔的10 纳米制程技术,在实质上非常的接近,结论是「这三家属于领先群的晶圆代工厂,替Intel 的主要竞争对手代工,将与x86 巨头站在同一水平」(注:x86 泛指一系列由英特尔开发处理器的架构。)

而Gwennap 认为,这三大竞争者,都有可能在2021 年时超越英特尔,率先迈入下一代芯片制程,但超越英特尔代表着,这些挑战者将比英特尔先面临下一代的光刻技术,半导体制程越先进,光刻设备便需要更复杂精密,将须承担制造过程中产生的风险。

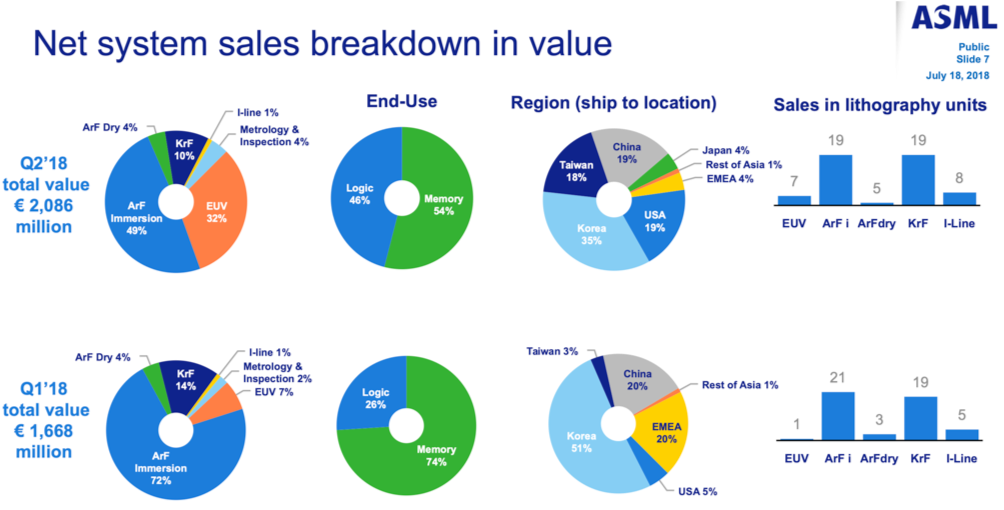

光刻(lithography) 是制作半导体线路的关键制程,决定线路的精密度,而光刻设备决定晶圆的工艺能力,ASML 目前为全球最大的半导体光刻机设备及服务提供商。

在制造工艺往7nm推进的过程中,围绕着Intel、TSMC、Samsung和GlobalFoundries(GF)四大晶圆厂的工艺进展讨论进入了一个新的阶段。无论是相关设计者、参与者,甚至旁观者,都对全球制造能力最强的四大公司的发展保持高度关注。作为晶圆厂的长期观察家,本文作者Scotten Jones对他们的工艺进展做了新的分享:

首先,我们来看一下,这几大晶圆厂目前能提供的最新工艺是什么。 虽然这些数据中有些是2001年的,(但重点是最新工艺)具体来说:

-

格芯(可提供完整的14nm和7nm工艺参数),我们预测了5nm的工艺。12nm和7+nm的工艺(已经)发布,我们对它们进行了预测。

-

英特尔:可提供14nm和10nm的工艺参数),我们预测了7nm。

-

三星:可提供14nm、10nm和7nm的工艺参数),(并且)发布了11nm、 8nm、6nm、5nm和 4nm工艺,这是我们也预测到了的。

-

台积电:可提供16nm、10nm和7nm的工工艺参数,台积电发布了12nm、7+nm、5nm和 3nm的工艺,我们也预测到了它们。

标准单元

逻辑设计由标准单元构成。 标准单元的高度是金属层2的厚度(metal 2 pitch (M2P))与(金属布线的数目)的乘积。 过去我们讨论过(金属层的厚度和布线数目),但(布线数目)是在金属层2中测量的,所以金属层的厚度也应该在金属层2测量。

一个单元的宽度与金属层互联节点大小有关,一些CPP取决于单元类型和是否使用双扩散(double diffusion break)或单扩散(single diffusion break)技术。

图2展示了标准单元的尺寸。

图2. 逻辑标准单元

金属层2高度(M2P)

我们比较逻辑工艺需要看的第一个度量值是M2P。(图三展示了4个掌握先进工艺技术的公司——格芯、英特尔、三星和台积电的工艺参数M2P)。实心标记是实际公布的值,空心标记是我们估计值。

图3. 金属层2高度

轨道高度

之前我们尝试定义标准单元时,我们基于ASML的工作使用CPP x MMP来实现。这个工作忽略了金属布线间距,随着公司将减小布线间距作为尺寸缩减的一部分(imec将它称为设计技术),布线间距变得越来越重要。

图4. 布线间距宽度

随着布线间距宽度的减小,每个器件的fin数目减少,所以布线间距的缩小(称为DTCO技术)也作为尺寸缩小技术的一部分。除非有其它方面的提升,否则减少每个器件的鳍会减小驱动电流,降低器件性能。

单元高度

结合实际的M2P和(布线间距)(并且)估计了的M2P和(布线间距),单元高度(M2P x Tracks)就可以计算了。图5展示了感兴趣的四个公司不同时间的轨道高度。

图5 轨道高度

单元宽度

单元宽度是CPP的倍数。它的倍数取决于单元类型(在接下来的两部分和Double Diffusion Break(DDB)和Single Diffusion Break(SDB)中会详细介绍)。DDB在单元的边缘需要假栅(dummy gate),(图6展示了简单单元3xCPP的SDB和2xCPP)。(显然,这存在一个非常重要的,可以缩小面积的潜在因素),尽管我们马上会看到使用标准单元会缩小更多面积,。即使这样也应该考虑得到一个相对好的单元尺寸。

图6. 单元宽度

CPP

为了计算单元宽度,我们需要了解CPP。图8中展示了我们感兴趣的四个公司不同时间的CPP。

图8. Contacted Poly Pitch

通过比较图8(CPP)和图3(M2P)可以发现,M2P比CPP缩小的更多。CPP受工艺制造设备的限制。在这儿可以看我对CPP限制的解释——LithoVision 。

常见逻辑单元

图9展示了两输入的NAND单元,它是最常见的逻辑单元之一。一个DDB两输入的NAND单元宽度为4x CPP,SDB两输入的NAND单元宽度为3x CPP。

图9. 两输入的逻辑单元

图10展示了另一个最常见的逻辑单元——扫描触发器。DDB的扫描触发器宽度是20x CPP,SDB的扫描触发器宽度为19x CPP。对于简单的逻辑单元来说,SDB缩减得更多。

,

图10. 扫描触发器

结合图8的CPP宽度,先进逻辑的生产商DDB和SDB的使用,图9和图10(展示了)了随时间变化的二输入的NAND单元宽度(图11)和图12中不同时间的扫描触发器单元宽度。

图11. 二输入NAND单元宽度

图12. 扫描触发器单元宽度

逻辑工艺密度

英特尔通过对二输入的NAND单元60%的加权和扫描触发器单元40%的加权,计算晶体管密度,由此提出了一个逻辑工艺密度的指标。权重取决于传统逻辑设计单元的普及程度。一个二输入的NAND单元有四个晶体管,一个扫描触发器单元有36个晶体管。通过公司了解二输入的NAND单元和扫描触发器单元的单元高度和宽度,我们可以描述晶体管密度。图14展示了四个公司不同时间每平方毫米数以百万计晶体管的晶体管密度。

图14. 晶体管密度

标准节点

(在这里我们可以停下来)基于晶体管密度比较这些公司,但业界还经常讨论节点。图15基于实际的节点-晶体管密度关系曲线描述了工艺参数。

图15. 基于晶体管密度的标准节点

根据图15我们可以描述这四个公司不同时间的标准节点。在一年内一个公司有不同工艺的情况下,我们绘制了密度工艺图像。

图16. 标准节点趋势

标准节点中加入DDB和SDB的讨论使英特尔的10nm工艺比第一代7nm工艺稍密集,但7nm+工艺将在2019超过英特尔的10nm工艺。在可预见的将来我们希望台积电和三星保持它们对英特尔的领先,格芯可能也会保持领先,但我们很难预测格芯的长期计划。

今天是《半导体行业观察》为您分享的第1561期内容,欢迎关注。

R

eading

推荐阅读(点击文章标题,直接阅读)

关注微信公众号 半导体行业观察 ,后台回复关键词获取更多内容

回复 兆易创新 ,看与兆易创新公司相关的文章

回复 摩尔定律 ,看更多与摩尔定律相关的文章

回复 材料 ,看更多与半导体材料相关的文章

回复 面板 ,看更多面板行业的文章

回复 晶体管 ,看更多与晶体管相关的文章

回复 晶圆 ,看晶圆制造相关文章

回复 士兰微 ,看更多与士兰微公司相关的文章

回复 展会 ,看《2017最新半导体展会会议日历》

回复 投稿 ,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

点击阅读原文了解摩尔精英

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英特尔重磅发布OPS 2.0,智能教育时代加速到来

- 2 破除AI落地难题!英特尔全新软硬件平台,助力企业AI创新

- 3 晶圆厂中的“超纯水”,你真的了解吗?

- 4 三方联合,上海国际汽车电子与半导体应用展览会将于明年4月在上海举办