ISSCC 2019论文解析:功率放大器篇

ISSCC2019论文解析目录:

1、Session 6 Ultra-High-Speed Wireline

2、Session 4 Power Amplifiers

今天来看ISSCC 2019的第四个session: 功率放大器(Power Amplifiers)。

(此文有2800字)

▼

功率放大器是每年ISSCC必有的一个传统Session,今年也不例外。

今年这个session一共有9篇论文,与上一篇文章提到的高速接口不同, 这9篇论文全部来自于学术界 。至少有两个原因:第一, 功率放大器的设计不需要16nm或7nm FinFET这样的先进工艺,不管是射频还是毫米波频段,65nm或40nm的CMOS工艺足够了 ,而且先进工艺的电源电压降低,功率放大器的性能反而受到影响。第二,学术界不必过多关注可靠性,可以得到更好的性能指标。 可靠性和最优性能指标是一个trade-off 。

学术界的朋友可以好好看看这个session,说不定能找到一些启发。

既然说到工艺,这里还要插入一句,为 了把整个系统集成在同一颗芯片之上,迟早会有采用FinFET工艺设计功率放大器的需求的 。那现在这些功率放大器技术,有哪些可以沿用到FinFET工艺?有哪些变得不那么有效?FinFET工艺的功率放大器又会哪些独特的挑战?这或许可以成为一个研究方向。

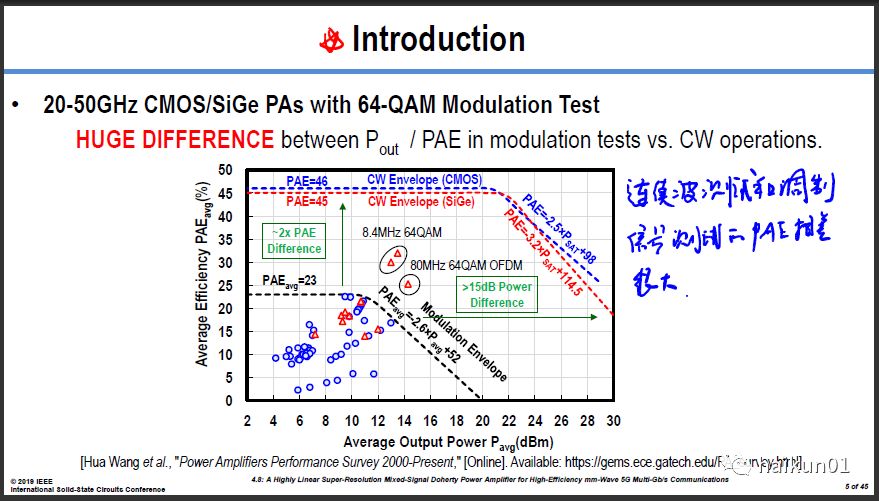

言归正传。从内容来看, 今年功率放大器的最大关注点是回退效率(power back-off efficiency) ,有一半的论文在针对这一点做提高。其他几篇论文关注点是功率合成、太赫兹、超宽带等等。

在具体看每篇论文之前,我这次先介绍一下功率放大器的回退效率的背景知识,方便大家理解这些论文在解决什么技术难点。

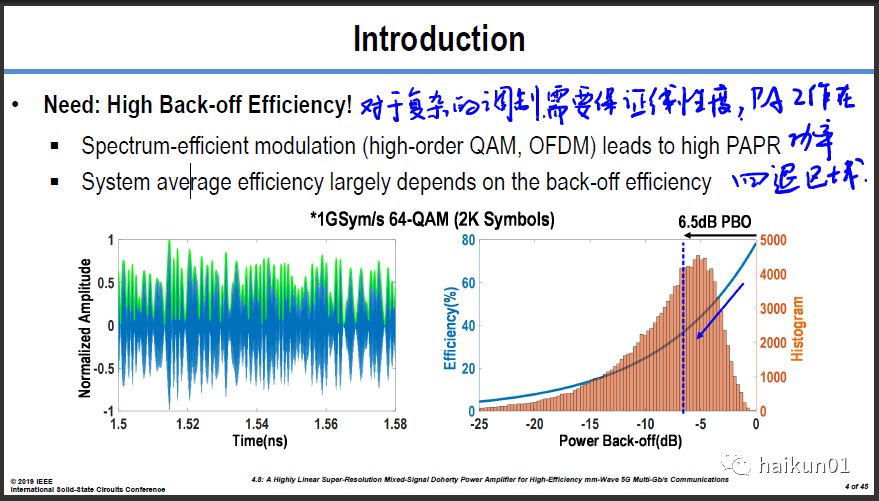

为什么要关注回退效率呢?

现在的通信系统为了充分利用频谱资源,都会采用很复杂的调制方式,如64QAM等等,信息同时蕴含在调制信号的相位和包络幅度之中。这对功率放大器的线性度提出了要求,设想我传递给功率放大器一个有四个电平的包络信号,假如功率放大器是完全非线性,发射出来的包络幅度全变成一样,那其中包含的信息就不可能找回来了。 因此功率放大器必须工作在饱和输出功率回退若干dB的地方,以避免非线性造成信号失真 。

下面这两页PPT很好的说明了这个背景。

那怎样才能提高功率放大器的回退效率呢?

想象一个简单的A类功率放大器,当输出功率减小时,由于偏置点不变,晶体管的直流电流不变,电源电压不变,因此消耗的功率不变。输出功率减小,消耗功率不变,因此效率会急剧下降。从这里我们可以看到 改善回退效率的本质因素:当输出功率减小时,同步减小功率放大器消耗的直流功率。

不就是减小直流功耗嘛,听起来很容易的样子。我先说一个很naive的想法:在功率回退时,我们同步降低电源电压,可以吗?

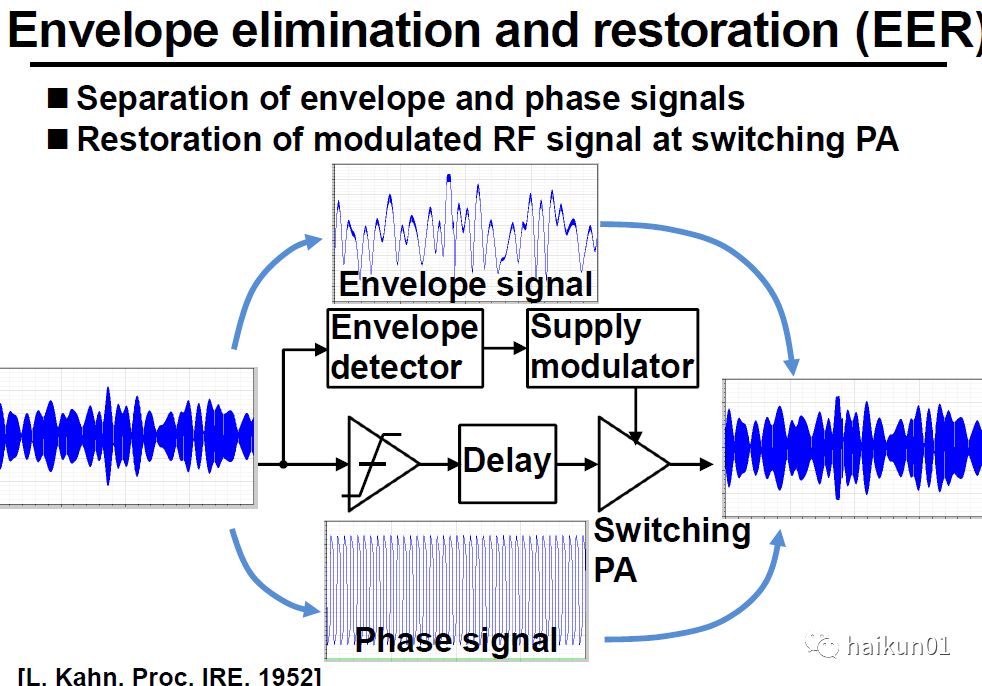

可以,很多人就是这样做的,所谓的Envelope Tracking技术就是这个从这个概念出发的。往年的ISSCC有不少采用这个技术的论文,但今年没有。简单的说, Envelope Tracking技术先从调制信号中提取出包络的幅度信息,然后用这个幅度信息去控制功率放大器的电源电压,使得输出功率小时电源电压降低,从而提高回退效率。

听起来很美好,但这个技术有一个本质的缺陷和两个不好克服的技术难点。

本质的缺陷是速度 。我们在设计功率放大器时,一般都希望有一个稳定的电源电压,需要滤波电容进行滤波,即使不额外加滤波电容,功率放大器电源端的寄生电容本来就已经非常大了。这恰好与Envelope Tracking的技术相违背,一个要求电源电压稳定,一个要求电源电压能快速变化。因此, Envelope Tracking技术没法支持快速变化的包络,调制信号的带宽受到限制,论文里能够实现的码率一般在几十兆 。在具体实现上的两个技术难点分别是“ 怎么控制 ”——包络环路与相位环路的匹配,以及“ 怎么调 ”——高效率的电源调制器(power modulator),我们好不容易把功率放大器的直流功耗降低,可不想这些节省的功耗被消耗在电源整流器上。

总的来说,在芯片设计里,电源电压是一个特别难调的量,尤其是需要实时调的时候。 电流大,无法容忍开关的插入电阻,电容大,没法快速变化。

既然电源电压不好调。那我提第二个naive的想法: 在功率回退时,我们同步降低(等效)偏置电压是否可以 ?

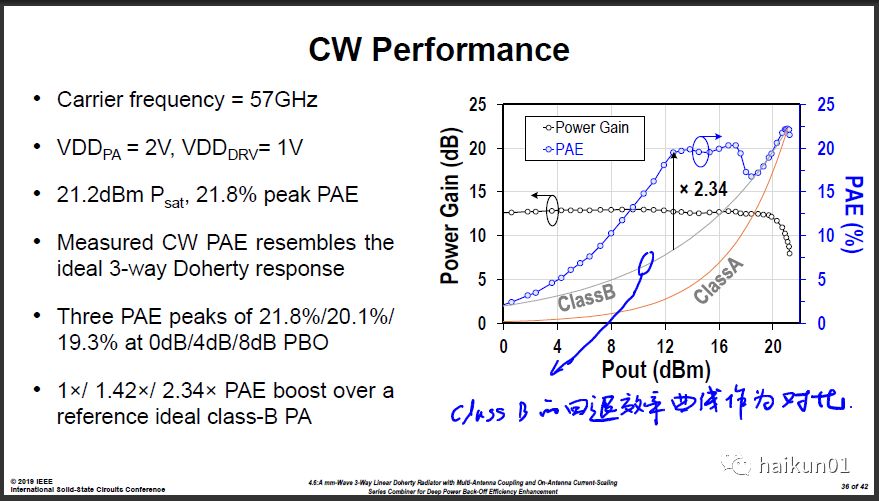

当然可以。B类的功率放大器不就是这个概念嘛。B类功率放大器偏置在晶体管的阈值电压,当输入功率减小时,等效的直流偏置点下降,晶体管消耗的直流电流下降。这的确在某种程度上提高了晶体管的功率回退效率。但是还不够。很容易理解, 功率放大器的输出功率随着输入电压幅度呈平方关系下降,而直流电流呈线性关系下降,输出功率下降更快,因此回退效率还是不够高 。现在大家一般把B类放大器的回退效率曲线作为对比,号称在回退若干dB时,我的效率比B类功率放大器提高了若干倍。如果你做了一个号称可以增强回退效率的功放,结果还打不过B类,那还是不要拿出来讲了……

偏置电压继续往下调就成了C类功率放大器,属于非线性功率放大器的范畴。这里再插入一句: A类、B类、C类放大器这些概念可能过于简化,但对我们的思维帮助很大。我们说一个实际放大器工作在B类,并不是说它恰好与教科书里定义的B类完全相同,而是说它的工作状态更像、或者更接近B类,采用B类的模型进行分析更准确。

对于单个功率放大器晶体管本身,我们可调的物理量似乎也就电源电压和偏置电压了吧。或与阈值电压也可以调,但Bulk CMOS工艺并没有调阈值电压这个选项,SOI工艺倒是可以。

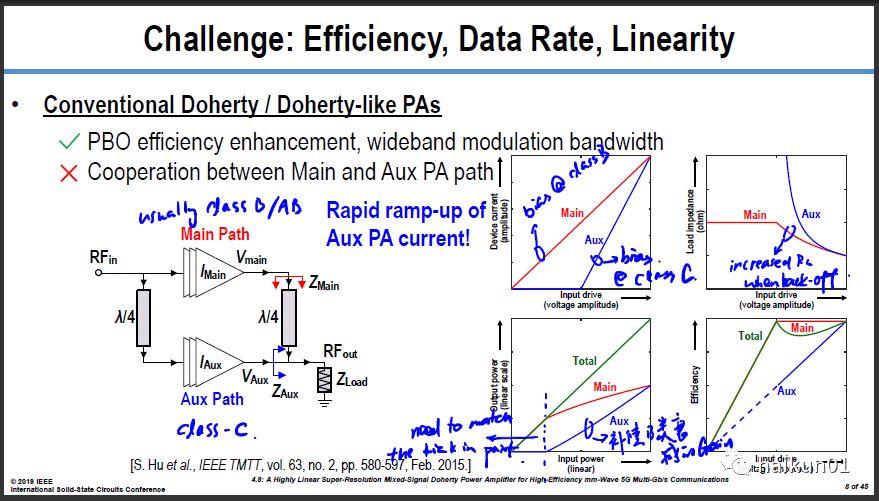

似乎调电源电压和偏置电压都不是那么有效,那么是时候引入第二个辅助功率放大器了。设想我们有两个功率放大器,主放大器偏置在B类或AB类,而辅放大器偏置在C类。这样当输入电压幅度小的时候,C类放大器打不开,只有B类工作,呈现出一个线性功放。 当输入电压幅度变大,B类主放大器的增益开始衰减,这时候恰好C类放大器被打开,补偿B类放大器减小的功率,从而提高了整体的线性度,也就提高了相对于最大输出功率的回退效率。

写到这里,对这一块熟悉的人应该可以看出来,这已经非常接近doherty功率放大器的概念了。但是doherty还要多一个 负载牵引 的概念。doherty功放的经典原理图如下图所示。所谓负载牵引,值得是当辅助功率放大器打开之后,它会往负载中注入一个相关的电流,可以使得主功率放大器看到的等效阻抗减小。为什么可以减小不详细解释了,从阻抗的定义可以推导公式。那为什么要做负载牵引呢? 对于B类功率放大器,负载阻抗是一个很重要的设计参数,当负载阻抗恰好使漏电电压摆幅接近电源电压时,功率放大器达到最高效率。 从这点出发, 如果需要大的输出功率,我们需要小的负载阻抗(V**2/R);当所需的输出功率减小时,最优的负载阻抗应该随之同步变大,使得B类放大器总是处于效率最优状态 。Doherty功放正是在朝这方面努力。

Doherty结构的功放在这几年的ISSCC露脸次数非常多,是功率放大器方向的热门领域 。今年也有数篇,我会解析每篇是在解决Doherty中的什么问题。

除了上面这些,还有两个提高回退效率的技术, digital功率放大器(配合Polar发射机使用)和Out phasing功率放大器 。与Envelope Tracking类似,Digital功率放大器也把调制信号分为相位和幅度两个支路,但幅度支路采用数字的方式控制功率放大器子单元阵列的开关数目,这样避免了去动很难调的电源电压,可实现更大的带宽,在我看来 是个比envelope tracking更具备潜力的技术 。DPA也面对幅度和相位支路匹配的问题,但不需要经过慢速的电源调制模块,应该比envelope tracking更好控制。而Out phasing功率放大器是通过改变两个功率放大器的输出信号矢量角度来改变整体输出功率,类似于矢量合成的概念,其在回退效率上的好处应该也是来源于回退时的阻抗调制。 如果采用隔离型功率合成器,out phasing功率放大器相对于普通B类功率放大器在回退效率上没有优势 。

一不小心背景知识介绍的有点多,但把这些背景知识串起来又对理解论文很有必要。具体的论文解析只能等到下周再写了。

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 破除AI落地难题!英特尔全新软硬件平台,助力企业AI创新

- 2 晶圆厂中的“超纯水”,你真的了解吗?

- 3 三方联合,上海国际汽车电子与半导体应用展览会将于明年4月在上海举办

- 4 突破痛点,矽典微让毫米波感知用的好用得起