来源:内容由半导体行业观察(icbank)编译自「

anandtech

」,作者:Dr. Ian Cutress,谢谢。

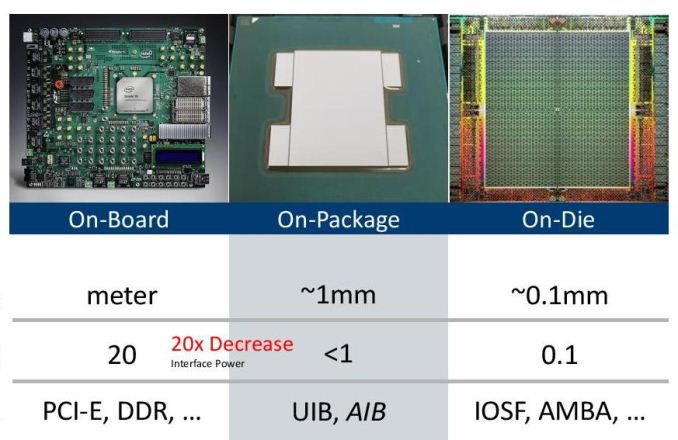

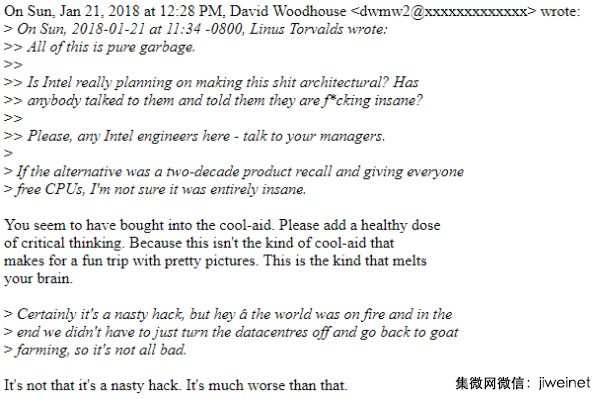

在过去的两年中,无论是在谈论采用新制造技术或新拓扑的芯片上,还是新通信标准或者连接范例芯片的带宽和效率的时候。我一直在说的是,半导体市场在性能方面的下一个战场将是互连。

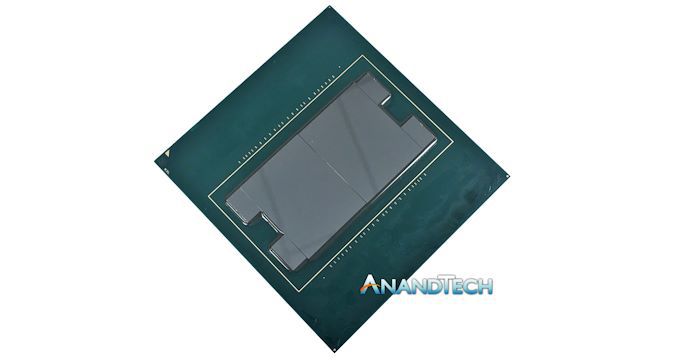

从单片设计过渡到chiplet和堆叠式硅,需要从硅工程师到设计使硅工程师能够胜任其工作的软件的供应商做一个根本性的转变,然而大多数行业尚未准备就绪。但英特尔拥有一个专门负责这些新互连和封装技术的部门。在今年的IEDM会议上,我终于有机会与英特尔相关高管Ramune Nagisetty会面,谈及这方面的内容。

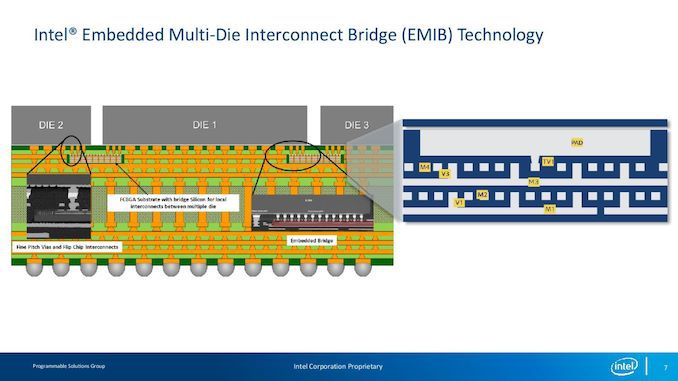

推动这些事情发展的一个前提是标准,因为它允许多个公司在混合搭配的情况下一起工作。Ramune是将多家公司联合起来的忠实拥护者,尤其是与逻辑公司合作的存储器公司,以确保这些标准协同工作,同时也可以通过共同优化芯片和产品来推动行业发展。其中的关键部分是向人们介绍这一概念,同时也要研究三到五年以上的发展方向。chiplet和连接chiplet并不是一个新概念,但是Ramune在这些chiplet如何连接方面处于设计的最前沿 ,无论是通过封装连接或EMIB水平连接还是像Foveros那样垂直堆叠。

问:

您的一位工程师本周提到了第二代3D堆叠Foveros技术。英特尔对该技术的路线图是什么样的?

Ramune Nagisetty:我们的每一项封装技术都有一个路线图,而这一切都与有关。我们在互联方面拥有很大的期望。其中一些技术的主要功能是pitch缩放、芯片间移动时的微凸点缩放和芯片堆叠时的TSV(硅直通)缩放。我们应该在某个时候展示或披露这些路线图,以表明我们在前进的道路上所处的位置。每种技术的节奏可能与正常产品路线图的节奏不同,因此需要考虑这一点。

制定路线图是一件好事,但我不想将我们的产品投放在没有发展前景的封装线图上。我的意思是我们已经看到55微米到45微米,然后最终也将出现具有10微米凸点间距的混合键合,但是这些事情在将来,它们本质上仍是“预路线图”技术研究阶段。真正的技能是在研究阶段确定何时采用其中一种技术,并将其用于寻路和开发。这里的关键是时间,所以今天我谈论了十年前我们在2008年为EMIB申请专利的方法,并于2011年开始撰写论文。但它在2018年开始发货。因此,当您决定使用这些技术时,只有您如何使用它们,才是真正涉及的技能。

问:

是否有可能让这些新封装技术达到一定规模后,然后成为有成本效益和价格敏感的市场

RN:我是这样认为的。我认为这是我们将来创建产品的方式的开始。并不是说我们不会提供某些单片SoC产品,但是将来它将是一个健康的组合。我花时间的地方是在三到五年的时间里开发技术,并且实际上超出了范围,所以我认为这些技术将从根本上改变我们将来实际规划路线图的方式。我认为,从现在开始的五年后,当我们研究产品路线图时,它实际上可能基于封装技术和可用的不同模板,然后将产品组合在一起。因此,它可能与今天的情况大不相同,后者是将所有东西都锁定在一个单片SoC中的方式。但是一旦解锁了这些东西,您将产品组合在一起的方式将会改变。我们正处于风口浪尖。

问:

英特尔在自己的生态系统中起了很大的推动作用,而AMD则一直聚焦在中介层和chiplet的方法。是否存在在某个时间点上你们双方说:“嘿,让我们一起做这件事?”

RN:我真正提倡的是行业规模生态系统的概念,在这里我们可以混合使用由不同的晶圆厂和不同公司生产的chiplet和IP。实际上,我认为这将解锁生态系统中的一大堆创新,然而这些创新如今由于进入成本非常高而受到抑制。即使在设计完整的单片SoC方面,设计方面也很艰巨,然后制造就更加艰巨。如果我们建立了一个混合搭配的生态系统,它可以使规模较小的参与者甚至大学或初创企业都能参与其中。

我认为,当您开发这些明确定义的接口时,例如一个芯片与另一个芯片之间的连接的概念性术语,它将使生态系统在以前固定的边界之外蓬勃发展。今天,我们已经看到很多这样的事情发生了一部分,那里有提供给代工厂的软IP和硬IP,并且我认为这也将在chiplet领域中发生。至少是其中的一部分。我们已经开始做很多工作,并且我确定您对DARPA芯片计划很熟悉。例如,有一家名为Ayar Labs的初创公司正在开发硅光子学的芯片。大学正在开发用于机器学习加速的芯片。因此,所有这些,以及我们在互连和封装技术方面所做的工作,都将这些带到初创公司和大学。

问:

Open Compute Project在今年初成立了一个名为ODSA的新工作组,致力于建立chipet生态系统。他们谈论的一件事是有多大挑战,我们如何知道要共享多少IP,对连接的每一端进行了多少控制以及如何在设计之间保持一致性。关于chiplet间通信和控制的讨论很多。

RN:我知道ODSA,我去过他们的一些会议。在这类生态系统蓬勃发展之前,必须解决许多问题。我认为其中之一实际上可以使用先进的封装技术。在具有控制能力之前讨论控制和事物是非常好的,但是当您能够做到这一点时,定义接口就变得更加容易。

如您所知,ODSA正在研究一种称为“电线束”(Bunch of Wires)或BoW的技术。(。就目前而言,ODSA采取的方法并不是真正基于先进的封装技术,这主要是因为ODSA尚未广泛应用于他们,因此,他们正在努力开发的接口也必须得到标准封装技术和有机基板的支持。

问:

Foveros是否具有标准接口,以便其他公司可以使用其芯片?

RN:还没有。它必须与Intel共同设计。即使在我设想的未来之初,也将与内存公司合作,共同研究如何创建标准化产品,因为它们不希望为每个人都创建定制产品,因为这样做并不划算。对于我们来说,我认为将进行某种行业合作,以弄清楚如何获得某种标准的内存接口定义。

问:

您对正在编写的类似于ITRS的新异构路线图文档有何看法?

RN:我已经读了第一章,这是相当不错的!我的意思是,他们有一章是关于医疗器械的,另一章是关于我不参与的事物的。但是,我认为人们正在努力研究并预测未来的发展是一件好事,我们有英特尔人员为该文件做出了贡献。认识到行业正朝着这个方向发展并很好地帮助了整个行业认识到这是一条走下坡路的事物,就像ITRS路线图帮助行业协调一致一样。

问:

这是这些封装技术的另一个争议,那就是准备用于芯片内和芯片间通信的通信协议。英特尔具有独特的地位,因为它可以立即定义所有这些内容,并且正如英特尔通过其新的Ponte Vecchio设计所披露的那样,我们拥有这种带有Foveros,EMIB的多层产品,并且看起来像其中的插入器也一样。

RN:这仍然是接口的转折点。我们已经在当今的产品(Stratix 10 GX 10M)中演示了我们的AIB接口,该产品使用EMIB和逻辑芯片到逻辑芯片集成。但是,HBM作为接口本质上是行业标准接口的第一个证明点,而对于AIB,我们也有第二个证明点。市场可能会朝着更高性能但不向后兼容的专有接口发展。您可能会看到通过紧密优化产品设计来进行优化,但是我们需要适当的行业标准,每个人都可以参与其中。

在Semicon West,我们提供了有关第二代AIB的一些详细信息,并且在将来有改进整体电源效率的接口的路线图,但是就像您决定要使其成为标准的任何东西一样,它必须具有一定的向后兼容性,否则就没有太大的帮助。关于何时将要向生态系统中释放最有效的接口但失去一些向后兼容性的信息,您必须有某种决策点,或者我们是要备份我们的方法并对开放的接口保持坚定的态度,但是也向后兼容。这要付出一定的代价,而不是始终走在最前沿,然后在支持互操作性的概念方面落伍,我们的方法确实需要一定的纪律。互操作性将成为我们要扎根的根基吗?这是我们自问的问题。

问:

您是否发现想要实施这些封装技术的人们想要最佳性能或最佳电源效率?例如,英特尔当前的Lakefield产品全都与3D堆栈的电源效率有关,即在一个很小的接口中提供足够低的功耗,或者另一个极端是使用EMIB的FPGA在两个FPGA裸片之间获得最高性能。在那一刻,我感觉我们正在看到频谱的两个相对端。

RN:要实现的一件事是,垂直堆叠和水平集成解决了两个不同的问题。当您进行垂直堆叠时,您必须具有非常高的功率效率,因为否则会导致散热受限,从而限制系统性能。但这是一个好的方向。我们已经讲过2.5D集成,然后是Foveros的3D集成,英特尔还公开了全向互连ODI。在IEDM上,它是最有趣的互连技术之一,因为它使您有机会在较小的裸片上拥有较大的裸片,或者可以将悬臂式/叠片式(cantilevered/shingled )裸片组合在一起,这是一种类似NAND闪存的技术。可以为您提供更好的连接。但您必须在设计时牢记这些,借助ODI之类的产品,它可以为您提供更好的连接性,同时还可以通过覆盖或不完全覆盖底部和顶部的die来平衡热约束。总的来说,我认为不同的集成方案可以协同工作,但是因芯片堆叠而产生的散热问题是一个很重要的工作领域。

RN:部分是协同设计。对于具有互操作性chiplet的未来行业规模生态系统而言,散热将是很重要的一部分,而在芯片堆叠上,解决散热问题的通常方式是需要让这些芯片一起计划,以应对两者的电源要求和散热。这些chiplet的协同设计通常意味着,在第一代可互操作的chiplet中,由于顶部,中间和底部芯片之间的协同设计至关重要,因此不会有很多层。使用2.5D设计时,互操作性(interoperability)更加清晰并且更易于处理。因此,在将来,我确实认为互操作性将进入3D堆栈中,而我希望看到的是内存堆栈。

今天,内存是一种来自特定公司的非常专业的技术。为了维持其业务模型,他们必须制定标准。其他每个人都必须遵守这些标准,因为每个人都需要内存。因此,具有逻辑的3D内存堆栈即将出现,在英特尔,我们还将在3D空间中推动互操作性。因此,例如,我们可以使用物理设计和机械接口的通用模板(general template),看到具有交替层作为内存的3D堆叠设计。如果模板是从这种角度设计的,那么我们希望它们在散热允许的前提下可以一起工作,这就是协同设计的目的。

问:

3D堆叠的问题之一是获得足够的组合die以适当地生产(yield appropriatel),尤其是当您超越两个堆叠时(这是英特尔的未来所在)这变得尤其重要,您能否谈谈英特尔堆栈技术中内置的冗余,以及这有何帮助?

RN:所以我们确实内置了冗余。我们大量使用了DFX,DFX代表“ Design for X”(可以设计用于测试,也可以用于成品率设计),我们在每个阶段进行扫描。在堆叠裸片之前,我们还可以使用单独的裸片测试技术,以确保在封装之前将两个有保证的已知良好裸片放在一起。因此,在用于成品率的设计/用于测试的设计与高级测试功能之间,这就是我们在保证已知良好裸片方面的前进方向。没错,这是讨论的重要因素,尤其是不仅是die的成品率,还是组合这些die的过程的成品率。

问:

您看到了这个方向,超越了2到3到4个堆叠的die吗?

RN:是的,我想您可能看过前一天展示的一张幻灯片,其中包含各种可能集成的不同逻辑技术,例如基于氮化镓的功率传输技术等。因此,如果您看一下,您已经可以看到电源,内存,IO和逻辑。因此,根据逻辑,也可以在同一程序包中将其分为主要节点和较旧的节点。

问:

堆叠封装技术需要解决的问题不仅是单片设计,还有产品的可变高度,这对于实际的最终产品集成意味着什么。这些z高度对话多长时间进行一次?

RN:很多。这些层在制造时需要减薄,或者有时必须添加dummy die,以确保最终的热解决方案要求封装上的所有die都处于相同的高度,因此可能会有 shimming 或者dummy die 放置在那里。这些dummy die 没有图案化,它们没有激活,它们在那里只是为了基本帮助散热。这绝对是一个问题,并且是非常重要的一点,因为这通常只是其中一些讨论的事后想法。人们在生产结束时就回过头来,带着他们的散热解决方案进行组装,反馈是这可能是事先考虑的,特别是当您从不同公司购买硅并将它们堆叠在一起时,您会知道并非每个人都具有相同的裸片薄化能力。因此,我们要驱动的部分机械标准还包括z高度方面。

问:

如果使用了dummy die ,我们是否应该期望Intel声明为堆叠设计?我的意思是,我们被告知Lakefield有两个die堆叠在一起,但里面可能还有更多die?

RN:您知道我不会对产品发表任何言论。我的意思是,如果您拥有芯片并具备拆解的设施,这将是显而易见的。我认为人们可能不会谈论它,因为它听起来好像并不处于领先地位,这并不是世界上最令人兴奋的事情。有时,与散热解决方案打交道并不是人们想要关注的世界上最令人兴奋的事情。

DS:在当前的Lakefield产品中,顶部的存储器是PIP类型的设计,并且由于存储器和逻辑die没有直接连接,因此数据必须通过大支柱( pillars)向下传输,并按顺序支持die堆栈到达内核。尽管内存在逻辑芯片旁边,但它正在做一个大循环。设计中有讨论过吗?

RN:就像我之前说的那样,由于这些内存供应商,我们希望让它们全部在标准化的机械和协议接口上协同工作,以便DRAM可以自己成为3D堆栈的一部分,然后我们可以绕开内存条已经部署的方法。您的建议不会在未来几周或2020年发生,但我们绝对需要这些接口,这绝对在我们列表的顶部。对于封装内的堆叠内存,我们只需要进行正确的协作即可。

问:

不仅是内存,我还可以谈谈本次会议提到的其他内容。

问:

当前的3D堆叠式宣布产品,如Lakefield,面积大约在100mm2以下。这是否意味着英特尔最终想要在每个堆叠层的裸片尺寸上拥有多大的积极性?这可能会影响良率和其他因素——堆叠数更高但较小的die会胜过几层大的die吗?

RN:关于芯片变薄和散热问题,还有平面性问题–细节在于魔鬼,特别是当您在封装中放置许多非常小的芯片时,但是在封装和硅界面之间也存在机械稳定性问题。我认为还需要考虑另一个方面,那就是die的长宽比,就像您是否拥有非常长的微小矩形层或更多方形die一样。这些问题也必须根据不会引起平面性问题或翘曲问题的芯片进行事先计划,因为那些问题会转化为散热问题,并且最终导致接触不良。如今,对于最小或最大的裸片尺寸,我们实际上并没有任何规范,但是如果我们要创建一个可互操作的chiplet生态系统,这些都是必须要做的。

问:

本周会议上的一些论文和讨论都涉及“单片3D”或“顺序堆叠”(在一个硅片上构建两层或多层逻辑)。即使在十年的时间尺度上,您是否也看到了这种结果?

RN:Monolithic 3D 是长期发展路线图,我的意思是您看到了我们在关于驱动这类技术的全体讨论中所介绍的内容。我们的演示文稿中列出的技术将推动10年或更长时间的扩展。沿着这些思路,人们说公司很少对10年后的未来有洞察力或可见性,但是要实施这些技术,这就是您必须考虑的。

特别是对于Monolithic 3D ,完全有可能做到。这个问题也将涉及散热问题,所以我想您知道进行裸片堆叠时的关键问题是,我们需要在优化功耗效率的角度来考虑我们的架构。通过在每一层添加额外的晶体管,功能和功能,我们将获得更高的性能。使用Monolithic 3D 设计,如果继续采用专注于性能最终优化的设计方法,我们可能无法获得好处。

因此,有一个非常重要的观念转变,即如果我们实际上将目标放在硅上的功率效率更高的内核上,则整个产品的性能可能会更好,因为通过芯片堆叠,您可以从其他集成的其他方面获得很多性能。过去没有。

因此,从设计和体系结构的角度出发,需要对性能的含义或意义以及我们如何获得它进行真正的重新思考。当您(甚至在英特尔内部)都将性能有时仅针对其单个硅模块的性能而不是集成产品的整体性能作为目标时,您必须非常熟悉这一点。这是利用这些技术需要发生的观念转变。

我们必须考虑的主要问题之一就是紧密耦合的3D堆栈之类的东西,即整个EDA生态系统必须能够处理这些需求和这些类型的设计。甚至用于chiplet堆叠的软件仍然需要发展,Monolithic 3D 工具也需要发展。只要新技术看起来真的很有吸引力,EDA生态系统就必须赶上它。我们正在密切合作,以确保至少我们正在与EDA供应商沟通未来的发展方向,以便使某些开发可以并行进行,

问:

随着Intel在自己的技术和自己的工厂中进行工作,拥有这些内部工具非常有用,但是为了将芯片生态系统推向Intel之外,甚至超越内存供应商,它也需要Intel与EDA供应商联系,以实现这一目标。实际分享这些知识。共同开发是“免费的”,对吗?

RN:我们今天正在这样做,而且我们看到内部心态发生了巨大变化,以分享我们为实现这一生态系统而需要分享的东西。EDA供应商必须准备好工具,以便我们能够实际利用我们开发的技术,但是一旦启用了EDA供应商,他们便可以将其作为每个人的功能提供。周围有一种敏感性,因为您基本上是在公开近期的方向。但是,正如您所看到的,有很多方向可供选择,因此对我们而言,能够与这些工具供应商进行预先沟通非常重要。总是有NDA协议,例如,如果我们需要供应商来开发功能,但是我们不希望它们透露细节或功能。但是这些工具供应商必须参与其中-他们与许多不同的客户合作,所以他们有办法解决这个问题。我认为他们也理解,如果他们为英特尔开发某种功能,则可能仅在短期内对英特尔有帮助,但是从开发此功能中总会学到一些技能。通过堆叠和互连,将需要一种或多种方法来实现这些功能。

问:

您个人参与了多少工作,从现在开始,在三到五分以上的时间内为您工作?

RN:我与Synopsys进行交互,这是我与之交互的主要供应商,即使它不是经常使用。我确实参与了,也许不是很详细,但是肯定是在较高的指导水平上。

问:

今年早些时候,英特尔披露它已发售了第200万枚EMIB产品。您是否看到EMIB进入主流台式机市场,在那里您将交付10+百万种产品,而不仅仅是高端小批量硬件?

RN:是的,绝对是。实际上,与其他一些集成方案相比,这就是EMIB的优势:成本在数量之内,并且使其易于管理。这就是我们想要分摊这些费用的数量。

问:

我对EMIB的担心之一是,英特尔从来没有将两个高功率芯片(只有一个高功率芯片和HBM)配对在一起,直到我们看到最新的Stratix 10产品线确实使用了两个由3连接的高功率FPGA。EMIB连接,这是随着EMIB设计的不断改进而实现的吗?

RN:确实与设计chiplet有关。当您将电路板级组件与EMIB放在一起时,这些部件并不是设计为共同封装在一起的,因此您最终会遇到与热应力和机械应力有关的问题。我认为这与我一直在谈论的思维转变有关,我们如何创建产品归结为我们如何认为这些chiplet将彼此交互,并且必须从头开始进行架构这样做。不仅如此,而且在将来,他们将不得不与其他人打成一片。

这需要对我们如何创建产品以及如何对单个组件的性能进行基准测试有更广阔的视野。我们还必须激励开发这些产品的团队如何确定他们的优先级,他们的工作目标是什么?因此,从chiplet的目标到架构或微体系结构,它的确做到了。因此,在某些方面它可能会变得更加复杂,但是在其他方面,如果我们可以定义这些接口并为这些单独的部分设置目标,那么这基本上就是我们前进的方式。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2181期内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

FPGA

|

稳懋

|台积电

|华为

|

IC

|

CMOS|RISC-V|2019半导体盘点

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!