来源:内容由半导体行业观察(ID:icbank)编译自「

nextplatform

」,谢谢。

在2014年将其IBM Microelectronics部门出售给GlobalFoundries(其本身是AMD的衍生产品)时,IBM就已经宣告退出芯片代工业务。毫无疑问,IBM此举是希望可以摆脱对代工厂的投资,同时还可以帮助成就一个更强大的第三方代工厂,蓝色巨人可以依靠它为其生产Power和z处理器。然而,具有讽刺意味的是,IBM的这笔交易能成功,是因为他们给GlobalFoundries 支付了15亿美元。更讽刺的是,后者也有可能帮助IBM的CPU竞争对手。

尽管IBM退出了代工业务,但发生了两个有趣的事情。

首先,该公司通常在纽约的工厂继续与AMD,三星,GlobalFoundries以及有时与Intel一起对半导体基础金属进行研究。我们不确定,但我们认为IBM想从这项工作中获得一些收益,近年来,他们也在7纳米,5纳米以及目前的2纳米工艺技术上做了一些研究。并推出了测试芯片。也许IBM认为,这项工作是保持其Power和z处理器不断发展的必要条件,但事实我们目前尚不清楚。

其次,GlobalFoundries于2018年8月终止了其7纳米极紫外(EUV)和常规浸没式光刻技术的进一步研发,因此这让IBM陷入了困境。为此他们选择了与三星合作,后者拥有制造DRAM和闪存的大型工厂,他们同时也正寻求扩大为自身和他人CPU做代工的晶圆代工业务。7纳米技术的代工合作伙伴的水平,对于今年即将面世的Power10芯片至关重要。

据之前报道,Power10最初计划使用IBM本身或GlobalFoundries的10纳米技术生产,但在此过程中发生了一些变化,他们在7nm翻车了。虽然三星已经对其进行了重建,但是Power路线图的时间已经延长了——正如英特尔因其10纳米和7纳米工艺的延迟而迫使其在架构上做更多的工作,但在工艺缩减上做得比以前少得多。

毫无疑问,从现在开始展望未来五年,半导体业务将会很艰难,因为随着摩尔定律的推进,缩小晶体管尺寸将变得越来越困难,并且预期的晶体管成本比例下降趋于平缓,近年来尤其困难。这就是为什么IBM Research今天在其纽约奥尔巴尼技术中心宣布其突破性的2nm技术的原因。

在蓝色巨人看来,这项突破性技术是非常重要,因为其展示了采用2纳米CMOS工艺在标准300毫米硅晶圆上蚀刻真实芯片的过程。

无论IBM推出这个的目的是啥,让我们感到高兴的是,IBM正在进行这项研究,并尽其所能帮助保持工艺节点的到来。过去,IBM完成了很多研发工作,其中包括数十年前创建单cell DRAM,当时该公司仍在自己制造存储芯片;他们还制造光刻胶并进行自己的3D芯片堆叠;IBM于1997年还发明了铜互连线,取代了半导体上传统的铝线,从根本上改善了性能并降低了晶体管的功耗;IBM还于2000年发明了硅绝缘子技术,并于2001年发明了低k电介质,所有这些技术都被带入了2001年推出的Power4处理器,使其能与RISC和CISC的竞争对手相比。这些技术让IBM的这个芯片成为了野兽。

由此可见,IBM深信,芯片制造技术使芯片架构得以飞跃。因此,也许显而易见的是,为什么蓝色巨人希望加入并发挥自己的作用。它是开明的工作自私,可能会花费与其产生的金钱相同或更多的费用。

据报道,目前担任IBM混合云研究副总裁的Mukesh Khare带领其完成了2纳米技术的突破。(如果Khare真正从事半导体研究,那么这个头衔就显得很愚蠢)。资料显示,Khare在1999年到2003年间,从事90纳米SOI工艺的开发,该工艺将Power4和Power4 +推向市场,他随后又负责了65纳米和45纳米SOI的推进,这些技术被Power5和Power6采用;之后他对对用于Power7的32纳米技术进行了研究,然后研究了在Power8上使用的22纳米工艺中使用的高k /金属栅极技术。然后Khare继续担任奥尔巴尼纳米技术中心的半导体研究总监,

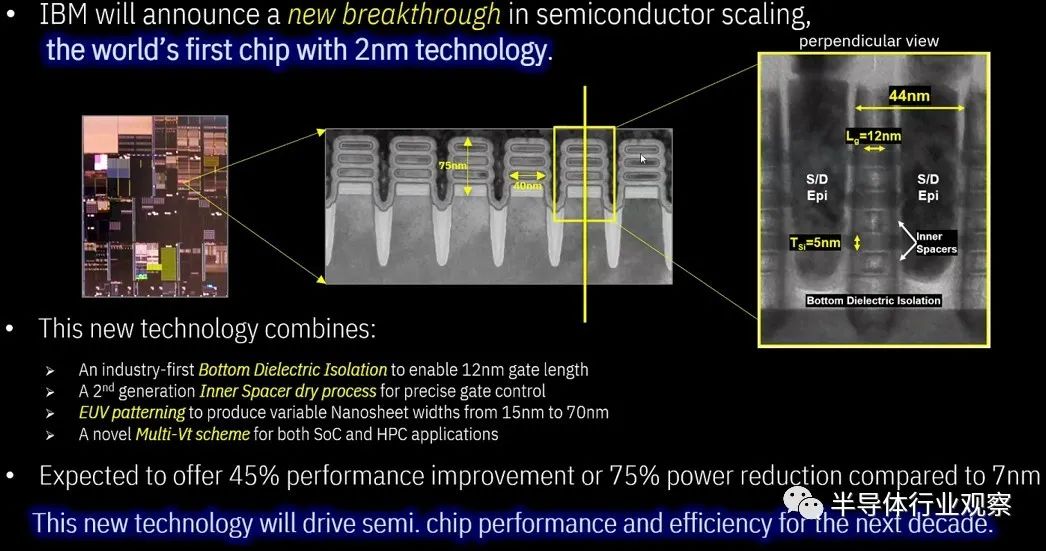

如下图所示,这是IBM掌握的2纳米芯片制造技术的要点。里面有很多东西,所以让我们把它拆开一点。

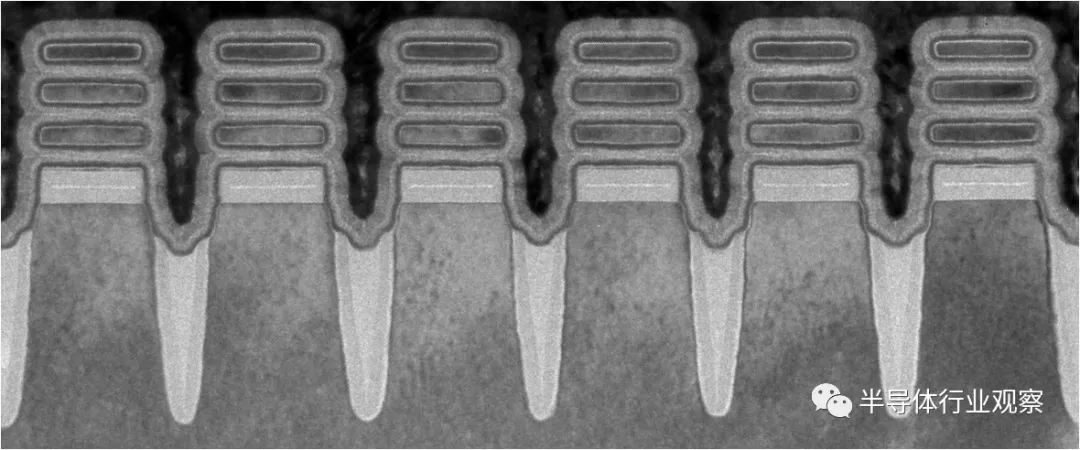

首先,在这个芯片上,IBM用上了一个被称为纳米片堆叠的晶体管,它将NMOS晶体管堆叠在PMOS晶体管的顶部,而不是让它们并排放置以获取电压信号并将位从1翻转为零或从0翻转为1。这些晶体管有时也称为gate all around或GAA晶体管,这是当前在各大晶圆厂被广泛采用的3D晶体管技术FinFET的接班人。从以往的介绍我们可以看到,FinFET晶体管将晶体管的源极和漏极通道拉入栅极,而纳米片将多个源极和漏极通道嵌入单个栅极以提高密度。

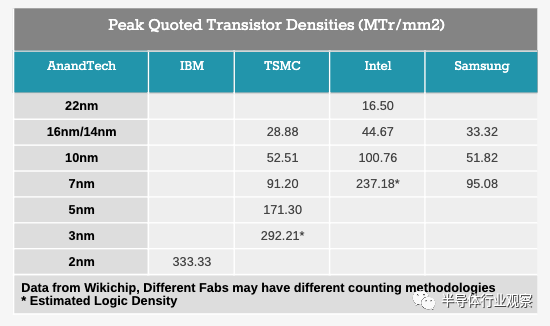

IBM表示,其采用2纳米工艺制造的测试芯片可以在一块指甲大小的芯片中容纳500亿个晶体管。

在IBM的这个实现方案下,纳米片有三层,每片的宽度为40纳米,高度为5纳米。(注意,这里没有测量的特征实际上是在2纳米处。因为这些术语在很大程度上是描述性的,而不是字面意义的,这令人发指。可以将其视为如果栅极仍为平面则必须具有的栅极尺寸,但却不是平面的,我想可能是这样。)如果您在上表的右侧看,那是一张纳米片的侧视图,显示出它的侧视图,其间距为44纳米,栅极长度为12纳米,Khare认为这是其他大多数晶圆代工厂在2纳米工艺所使用的尺寸。

2纳米芯片的制造还包括首次使用所谓的底部电介质隔离(bottom dielectric isolation),它可以减少电流泄漏,因此有助于减少芯片上的功耗。在上图中,那是浅灰色的条,位于中部横截面中的三个堆叠的晶体管板的下面。

IBM为2纳米工艺创建的另一项新技术称为内部空间干燥工艺(inner space dry process),从表面上看,这听起来不舒服,但实际上这个技术使IBM能够进行精确的门控制。

在实施过程中,IBM还广泛地使用EUV技术,并包括在芯片过程的前端进行EUV图案化,而不仅是在中间和后端,后者目前已被广泛应用于7纳米工艺。重要的是,IBM这个芯片上的所有关键功能都将使用EUV光刻技术进行蚀刻,IBM也已经弄清楚了如何使用单次曝光EUV来减少用于蚀刻芯片的光学掩模的数量。

这样的改善带来的最终结果是,制造2纳米芯片所需的步骤要比7纳米芯片少得多,这将促进整个晶圆厂的发展,并可能也降低某些成品晶圆的成本。这是我们能看到的。

最后,2纳米晶体管的阈值电压(上表中的Vt)可以根据需要增大和减小,例如,用于手持设备的电压较低,而用于百亿超级计算机的CPU的电压较高。

IBM并未透露这种2纳米技术是否会采用硅锗通道,但是显然有可能。

与当前将使用在Power10芯片的7纳米制程相比,这种2纳米制程有望将速度提高45%或以相同速度运行,将功耗降低75%。

现在,我们知道您在想什么。首先,Power11芯片会使用这种2纳米工艺吗?其次,这之后到底会发生什么?1纳米工艺似乎几乎是不可能的,不是吗?

让我们再谈一遍Power路线图。Power10为7纳米,并且考虑到Power和z服务器业务的保守性和遗留的特性(正在对处理器进行三年更新),已经在设计中的Power11和正在白板中的Power12在有5纳米和3纳米节点可以使用时,似乎并没有必要先冲到2纳米。Khare也预计将在2024年底准备生产。Power11应该在2023年左右的某个时候出现,并且应该采用成熟的5纳米工艺,这意味着它将相对便宜。(比起采用4纳米,3纳米或2纳米工艺更便宜,这是相对的部分。)

Khare说:“我认为没有一堵墙是我们无法突破的,我会说还有更多的突破正在酝酿之中,随着技术的成熟,我们将分享越来越多的突破。”这是一个不错的措辞。“我没有看到一堵墙,我看到了很多机会和很多可以创新的东西,我们可以不断创新。”他补充说。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2668内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备|封测

|射频|存储|美国|台积电

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!