来源:内容由半导体行业观察(ID:icbank)编译自「

semiwiki

」,谢谢。

关于摩尔定律的消亡,近年来有很多讨论。连续工艺节点的场效应晶体管密度的增加已从早些年的每2.5年增加一倍的速度降下来。摩尔在几十年年前发表的评论的经济性质也受到了影响——每个晶体管的成本降低也有开始降速。

由于多方面的要求,传统的技术缩放模型已变得更加复杂,更多的技术也开始被引入。例如替代沉积和蚀刻设备、新的互连和介电材料。与此同时,行业越来越依赖于新的设计技术协同优化(DTCO)集成方法。

顺便说一句,各种2.5D和3D多die封装产品的出现导致使用了

“

More than Moore

”

的出现。这些封装中管die功能和工艺选择的潜在多样性为实现有效 密度和成本提供了其他折衷,这是摩尔定律的基础。

尽管有关于摩尔定律即将死亡的讨论不绝于耳,但仍存在对新设备的巨大研发投资,这些新设备将继续提供改进的性能,功率和面积。

在最近由SEMI主办的的高级半导体制造会议(ASMC)上,Intel的Design Enablement副总裁兼总经理Gary Patton的主题演讲,他概述了这些研发工作。同时他在有关

“

摩尔定律

”

的演讲对未来的技术功能提出了乐观的看法。

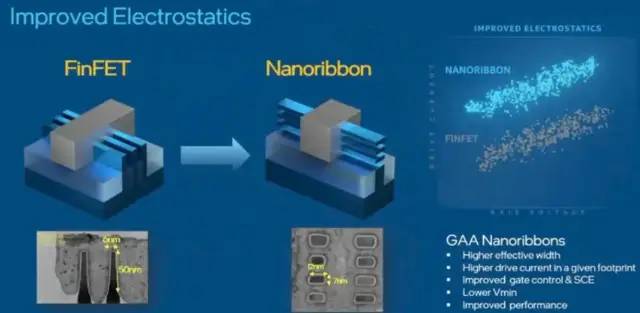

Gary介绍了向全栅极(GAA)器件的过渡,该器件有望成为FinFET的直接后继产品。(随着重新引入单个晶体管宽度又是设计参数的设备,可能需要重新解释晶体管/ mm ** 2密度度量。)

作为CMOS以外的潜在长期过渡,正在进行许多研究计划 ,例如2D半导体材料(的阵列),例如MoS2,WS2和WSe2。

在Gary的演讲中,特别值得注意的是对工艺技术开发领域的描述,该领域可能没有得到应有的考虑。例如异构半导体材料的3D单片集成,用于制造优化的nFET和pFET器件。这种方法提供了持续的器件缩放,成熟工艺制造技术的集成,并且建立在现有(基于CMOS)电路设计经验的基础上。

在详细介绍某些整体式3D可能性之前,他对异质材料结合的描述也是很有见地的。

Oxide Bonding和Donor Wafer Cleaving

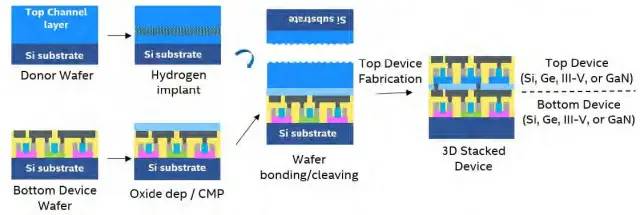

单片3D集成的目标是为设备制造提供多种堆叠的半导体材料。在主晶圆中制造晶体管的子集。随后,将(不同半导体组成的)

Donor Wafer

结合到主体上,并在主体顶部上提供薄材料层以用于后续的器件处理。下图说明了晶圆处理流程。

全厚度主晶圆提供机械支撑;薄的doner层不会显着增加整体厚度,从而可以使用现有的处理设备和制造流程。(正如不久将要讨论的那样,用于处理doner层设备的热预算受到限制,以免对现有的主机设备特性产生不利影响。)

-

-

主晶圆接受薄介电层的沉积(例如,SiN和SiO2的化学气相沉积)

-

-

使用优化的注入能量和剂量,对一个(300mm)doner晶圆进行H +(质子)注入

-

在键合host和doner晶圆之前,采用特定的硅片表面清洁化学方法。两个硅片表面必须是亲水的,“原子上光滑的”并且具有高密度的化学键合位点(以防止在界面处形成微孔)。

在特殊的对准器(带有双晶片卡盘)中,主硅片和Doner硅片彼此相对放置,对准并接触。在初始的晶圆对晶圆界面键合稳定之后,释放Doner卡盘。

然后,对复合材料进行热退火步骤。该退火具有两个关键功能: 加强键合界面,并允许注入的氢在半导体晶体中扩散,并成核形成H2。

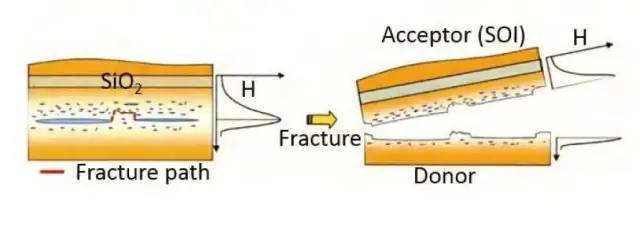

在Doner中会形成一个非常薄的H2层,其深度等于H +注入后最高的硅片位错点。该H 2层在doner硅片晶体内引入了结构上较弱的界面。

多年来,这种用于氧化物键合和Doner层转移的技术已用于绝缘体上硅(SOI)晶片制备的生产中。(对成核退火步骤中H +扩散,H2层形成以及对doner硅片晶体的结构影响的深入了解仍然是研究的活跃领域。)

Gary的演讲重点介绍了英特尔研究部门正在将这一层转移技术应用于3D单片集成的两个领域,以进一步扩展摩尔定律。

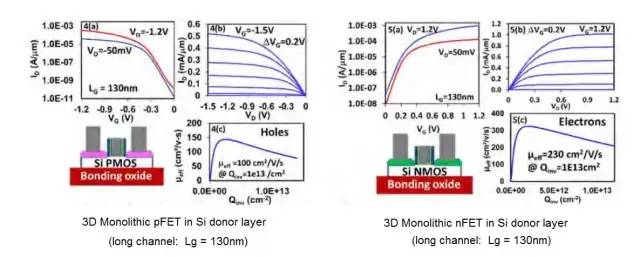

先进工艺开发面临的问题之一是Si中相对较弱的空穴迁移率,尤其是在较高的空穴自由载流子密度和电场下。

当前的工艺技术在pFET器件通道中引入了压缩机械应力,以提高空穴迁移率。最近的进步致力于直接在pFET器件通道中利用化学计量的Si和Ge的组合-即Si(x)Ge(1-x)-来利用Ge中更高的空穴迁移率。

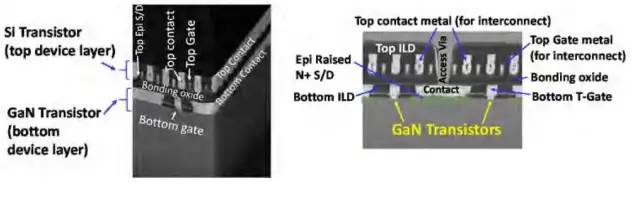

英特尔研究小组一直在使用3D单片集成技术,该技术使用键合在Si主硅片顶部的Gedoner层,如下图所示。

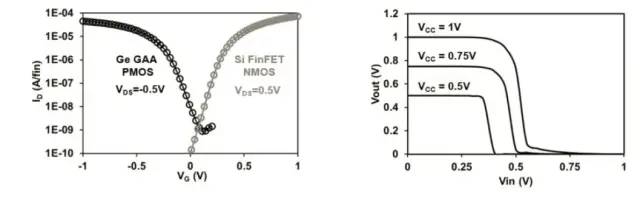

在这种情况下,在用于nFET的主晶圆上制造了FinFET器件结构,而在Ge doner层中的pFET使用了GAA拓扑。如上所述,选择nFET高K,金属栅极,源/漏掺杂外延和接触金属的工艺流程和材料选择,使其与Ge施主层的后续热处理和pFET的制造兼容(例如, <600C)。

在制造GAA pFET源极/漏极Epi,器件氧化物和金属栅极(使用替换栅极工艺)以及源极/漏极触点之后,在两个晶体管层之间形成通孔。

上面还显示了一个300mm晶圆上的Ge doner层厚度的示例分布图,显示了整体层转移过程的出色均匀性(整个晶圆上的变化小于3nm)。

下图描述了3D单片反相器逻辑门(低至VCC = 0.5V)的最终3D横截面,(短通道)Si nFET和Ge pFET特性,以及Vout与Vin传输特性。Ge pFET的离子对Ioff曲线说明了应变Si器件的改进特性。

使用垂直堆叠在Si层顶部的Ge层进行异构集成为CMOS逻辑实现提供了独特的机会,有助于扩展摩尔定律。

上一节介绍了一种在Ge pFET中实现改善的空穴迁移率的方法。出现高级工艺开发问题的另一个领域是需要与常规CMOS逻辑集成的高效RF级设备。对于5G(及更高版本)应用的需求,对于mmWave功率放大器,需要最佳的器件截止频率(Ft)和最大振荡频率(Fmax)响应,对于低噪声放大器具有相应的低噪声特性,并且对于RF开关具有快速的开关速度。增强型GaN器件出色的Ioff和低Ron吸引了高效集成稳压器设计。

Gary强调了英特尔研究团队为开发GaN器件与常规Si CMOS电路的单片异构集成所做的工作。

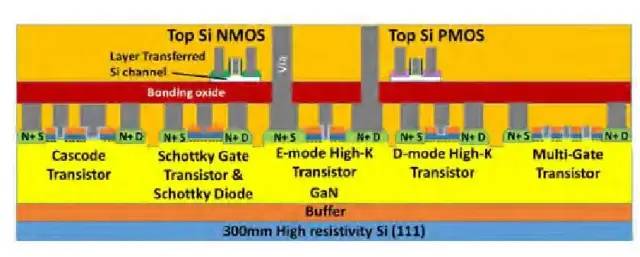

下图说明了在主硅片(Si衬底)上的外延层中制造各种GaN组件的制造-例如,增强型和耗尽型nFET,肖特基栅极FET和肖特基二极管(无高电平)。-k栅极氧化物电介质)。还显示了最终结构的横截面。

在这种情况下,doner硅片是Si,用于制造nFET和pFET器件,就像用于模拟功能,数字信号处理和逻辑/存储器一样。(P沟道GaN器件的制造极具挑战性。)

以前的Si nFET和Ge pFET单片集成的电路级CMOS集成需要一致的(且具有攻击性)设计规则,而(RF)GaN器件和(CMOS)Si器件的独特应用使这两种技术脱钩。与Si FinFET相比,GaN器件的尺寸可能与FET相差很大(例如,对于Ron非常低,W> 10um),或者具有更长的沟道长度以支持高压应用。

与在键合doner Ge pFET层之前制造的主体Si nFET一样,GaN器件在随后的doner Si层转移和nFET / pFET器件制造中具有很大的耐受性。

下面显示了(长沟道)GaN增强模式和耗尽型nFET器件的典型Ids对Vg曲线,以及在doner层中制造的Si nFET和Si pFET器件的特性。

FinFET器件在摩尔定律中的下一个发展将是GAA拓扑。3D单片集成确实可以促进继续摩尔定律的机会,将用于SO硅片制造的键合层转移技术扩展到更广泛的半导体材料,例如Ge和GaN。这将有助于减轻与引入“Beyond CMOS”材料工艺相关的风险。

对于从高性能计算到高频RF信号处理的各种应用,跟踪各种类型的设备的垂直堆叠的进展和创新将非常有趣。

学术界成员在ASMC上的一则评论引起了我的注意。他说:“我发现学生对追求微电子学作为研究领域的兴趣正在减弱。他们听到“摩尔定律已死”,并得出结论认为这一领域已经停滞了。”

坦率地说,我想不起来比现在有更多的机会在设备研究,处理技术和电路/系统应用程序开发方面取得重大进展。如果您是阅读本文的学生,请意识到延续摩尔定律过程中,有许多激动人心的经历。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2680内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|美国|华为|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!