比利时imec在2021年11月举办了针对日本的技术介绍会议一一ITF(imec Technology Forum) Japan 2021,在会议上imec披露了当下的研发成果和未来的计划。之前都是在东京的某家酒店举行会议,今年受到疫情影响,在线举行。

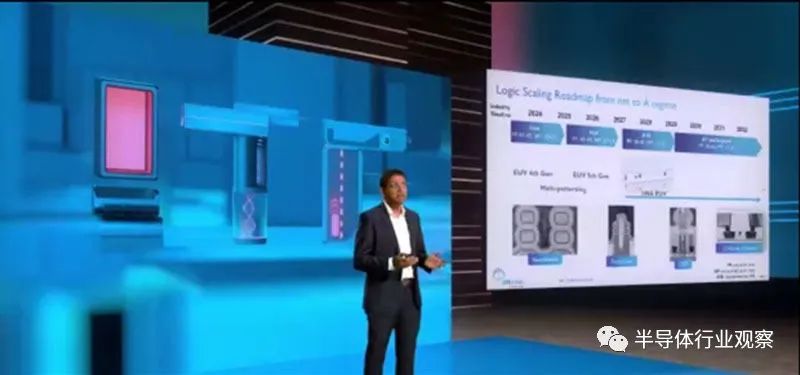

图1:ITF Japan 2021的演讲。出自笔者截图。

在上世纪末,就已经出现“摩尔定律”已经终结的悲观论调。但是,imec为了不让摩尔定律(是半导体产业增长的原动力)终结,一直在致力于提高工艺微缩化的集成度。而且,imec认为,在2020年之前的五十多年时间里,摩尔定律一直都在发挥作用。未来,通过导入微缩化、新型元件结构、新材料,以及堆叠芯片内晶体管和3D封装(堆叠芯片),摩尔定律还会继续发挥作用。

图2:在过去五十年里,半导体芯片上晶体管数量的变迁。摩尔定律一直存在。(图片出自:mynavi)

首先,作为2D的微缩化方向的努力,imec此次展示了未来十年的逻辑半导体工艺、电子元件的长期技术蓝图。

一直以来,微缩化的标准都是以纳米为单位表示的,在2025年以后,即进入以“埃(Å,angstrom,1埃 = 0.1纳米 = 1^(-10)米)”来表示的时代。届时逻辑半导体工艺、元件实用化的蓝图如下:2025年为“A14(14Å=1.4纳米)”、2027年为“A10(10Å=1nm)”、2029年为“A7(7Å=0.7纳米)”。

这与英特尔在2021年7月披露的逻辑半导体工艺技术蓝图如出一辙,即2024年为“Intel2(2纳米)”、2025年为“Intel 18A(18 Å)”(注:此处为英特尔公司内部叫法,可以看出英特尔试图追赶在微缩化方面领先的TSMC)。Imec展示的逻辑半导体元件的技术蓝图上记载了“Industry Timeline”,还展示了先进半导体企业开始生产的年份。

另外,imec的长期方向在于研发先进工艺,而不是先进半导体企业从事的生产工艺。即,为了实现1纳米以下的微缩化元件,imec已经在研发工艺、材料。将研发业务委托给imec的全球先进半导体企业与诸多设备材料厂家一起,外派了诸多技术人员、研发人员到比利时的imec园区,从事合作研发。

之前,人们使用最小加工尺寸、最小线宽、MOS晶体管的栅极(Gate)长等来表示逻辑工艺的微缩化,如今,各家公司不再将微缩化的程度拘泥于指标性数字,实际上集成电路上并没有表示其长度的地方。因此,TSMC一直以来的“Nx(比方说,不说4纳米,而是说N4)”、Intel最近提出的“Intel x(比方说,不说4纳米,而是说Intel 4)”,这些名称上都没有提到长度单位。

从数字来看,每个代际(技术节点)都是上一代际的0.7倍左右(如,3纳米、5纳米、7纳米、10纳米。。。。。。),这是英特尔自1970年制造出全球首个1K DRAM以来的传统,长度为上一代际的0.7倍,面积就会成为上一代际的二分之一。如今,代际已经不再用长度来表示,因此面积也不一定就是上一代际的二分之一。

比方说,从下图3中可以看出,PP为多晶硅(Polysilicon)排线线距(Pitch)的实际长度,MP为第一段金属排线层的线距的实际长度。这样,各家公司对于逻辑元件微缩化的指标就大相径庭,且他们的指标远远小于线距。

图3:imec的逻辑工艺·元件的微缩化技术蓝图。时间轴与先进半导体企业的生产元年一致,imec已经开始研发1纳米(10Å)以下的工艺。imec的目标是在三年内,将High NA EUV设备从试做到导入量产。(图片出自:mynavi)

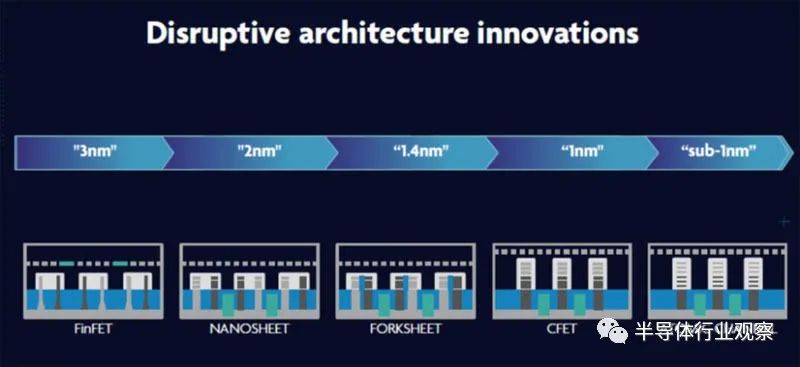

就逻辑元件而言,随着微缩化发展,其晶体管的结构从长年以来的平板型(Planner)结构到FinFET结构,在2纳米以后,TSMC、英特尔正试图采用GAA(Gate-All-Around,全环绕栅极)纳米片(Namo-sheet)压层结构。英特尔称之为“RibbonFET”。此外,三星率先宣布已经从3纳米过度到GAA纳米层(三星称之为“MBCFET(Multi Bridge Channel FET)”)。

就14 Å节点而言,imec提案了原用于CMOS的Forksheet结构(将p型和n型纳米片晶体管成对排列,由于类似于用餐的叉子,所以命名为Forksheet),并一直在研发。就10Å节点而言,imec试图采用CEFT结构(Complementary FET,在硅表面垂直堆叠P-channel FET和N-channel FET),制作CMOS。在1纳米(10Å)以及以下节点,计划采用原子形状的沟道(Atomic Channel),其沟道采用厚度为1~多个原子层的2D材料。此外,imce所指的2D材料为半导体单层过渡金属二硫属化物(Dichalcogenide),化学式为MX

2

。此处的M为Mo(钼)、W(钨)等过渡金属元素。X为硫、Se硒、Te(碲)等硫硒碲化合物(16类元素),imec通过采用2D材料和High NA EUV,开拓了1纳米以下的工艺。

图4:对晶体管结构变化的预测,imec正在研发以上所有的晶体管结构。(图片出自:mynavi)

目标是在High NA EUV试做机出货三年后实现量产

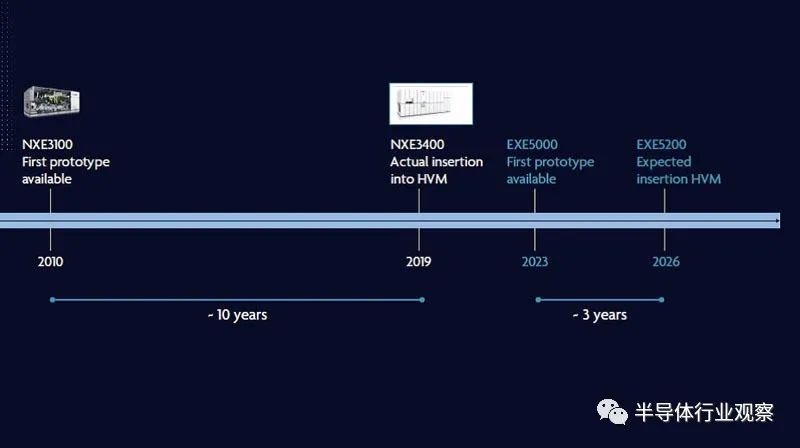

下面我们来看看EUV 光刻的未来技术蓝图。就2纳米工艺而言,其使用的是继7纳米、5纳米、3纳米之后的第四代EUV光刻技术,且14Å就在其延长线上。

但是,据预测,在14Å以后,将不再使用NA=0.33的EUV,而是采用NA=0.55的High NA EUV光刻。Imec和ASML已经合作在荷兰设立“imec-ASML Joint High NA EUV Research Laboratory”,由ASML在2023年导入High NA试做一号机。就EUV专用涂覆显影设备(coater developer,即clean truck)而言,已经决定由独霸市场的东京电子来提供。

ASML在2010年出货了用于首代量产技术研发的EUV曝光设备一一“XE:3100”,十年后,量产设备“NXE:3400”被用于逻辑半导体的量产产线。就High NA EUV曝光设备而言,目标是在2023年出货试做设备(EXE:5000),在三年后的2026年导入量产产线,技术人员正在imec-ASML的合作研究所里集中推进研发。

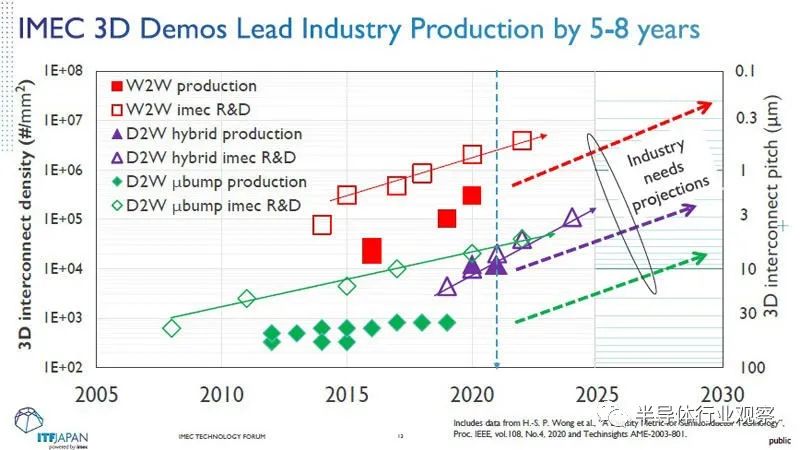

通过将原本平铺的晶体管垂直堆叠,就可以使集成电路的晶体管数量增多,这是一个方向;此外,通过采用3D封装技术(堆叠半导体芯片或者晶圆),来进一步增加晶体管数量的研发也在如火如荼地进行。TSMC在日本成立3DIC研究中心的目的似乎也在于此。

就imec而言,其研发水平远远领先于业界5一一8年的时间,其目标是先于业界实现某些技术,而且这些研究大部分是与合作伙伴共同合作的。

图6:半导体企业的3D Interconnect密度、imec的推移表、未来的预测。(图片出自:mynavi)

此外,imec在ITF Japan 2021上 做了新的研究主题一一《可持续发展的半导体技术、系统(Sustainable Semiconductor Technology and Science: SSTS项目)》。

在这个项目中,预测了生产半导体芯片时对环境造成的影响(电能消耗、化学药品、材料、超纯水、气体等其他消耗),通过详细分析碳足迹(Carbon Footprint,指的是一个人或者团体的“碳耗用量”),力求实现降低生产IC时的环境负荷。很期待半导体厂家(如生产设备厂家、材料厂家、晶圆代工厂)等企业共同加入研发,最近Apple(既是半导体Fabless、也是半导体客户)也加入了研发,作为一项可以响应全球“碳中和(Carbon Neutral)”目标的活动,而被业界所熟知。

即,imec希望通过以上措施,以支持全球半导体供应链削减 “碳足迹”。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2877内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!