来源:内容由半导体行业观察(ID:icbank)

编译自IMEC

,谢谢。

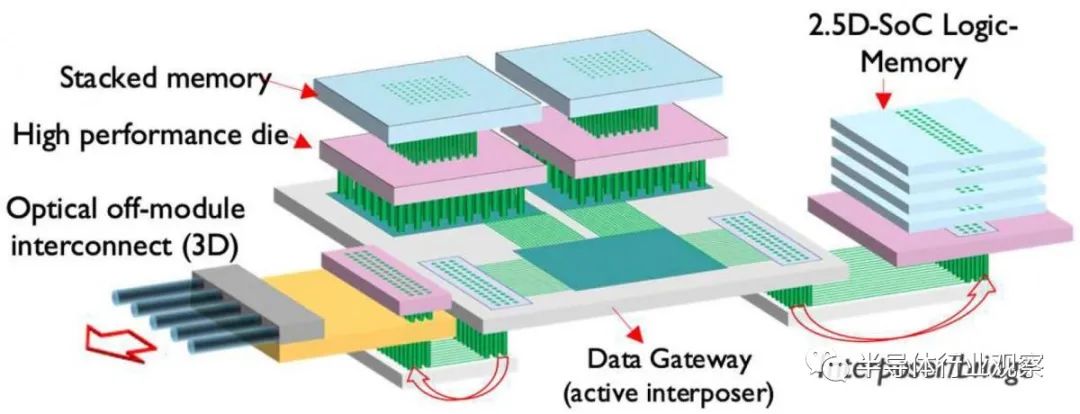

用于高级计算、数据服务器或深度学习应用的数据密集型高性能系统越来越受到所谓的内存墙的影响——即足够快地访问数据的挑战。拆除内存墙的一个有趣方法是 3D 片上系统 (3D SOC) 集成。遵循这种异构集成方法,系统会自动划分为独立的芯片,这些芯片在三维空间中同时设计和互连。

在 2021 年受邀的 IEDM 论文“3D-SOC integration, beyond 2.5D chiplets”中,作者解释了这种 3D-SOC 概念如何超越当今流行的小芯片方法,以实现多芯片异构系统集成。Imec 高级研究员、研发副总裁兼 3D 系统集成项目总监 Eric Beyne:“小芯片涉及单独设计和处理的小芯片芯片。一个众所周知的例子是高带宽存储器 (HBM)——动态随机存取存储器 (DRAM) 芯片的堆栈。该内存堆栈通过接口总线连接到处理器芯片,这将它们的使用限制在容忍延迟的应用程序中。因此,小芯片概念永远不会允许在逻辑与快速、一级和中级缓存存储器之间进行快速访问。”

通过 3D-SOC 集成,可以使用直接和较短的互连来实现内存逻辑分区,从而显着提高性能。在他们受邀的论文中,作者展示了 3D-SOC 设计的优化实现,内存宏位于Die的顶部,其余逻辑位于Die的底部——与 2D 设计相比,工作频率提高了 40%。

图 1:未来可能的高性能系统的抽象视图。具有 3D-SOC 堆叠内存的高性能芯片在有源中介层芯片上实现,该芯片充当数据网关并以“2.5”方式与本地高带宽内存和光收发器模块(如 2021 IEDM 展示)连接。

他们还讨论了实现全功能 3D SOC 的关键挑战。imec 首席科学家、布鲁塞尔自由大学教授 Dragomir Milojevic:“在设计方面,逻辑和内存分区都需要 3D-SOC 协同设计策略。这需要能够同时处理两种设计的专用电子设计自动化 (EDA) 工具,在布局布线期间使用自动化工具进行系统分区和 3D 关键路径优化。通过与 Cadence 的合作,我们可以使用这些非常先进的工具。”

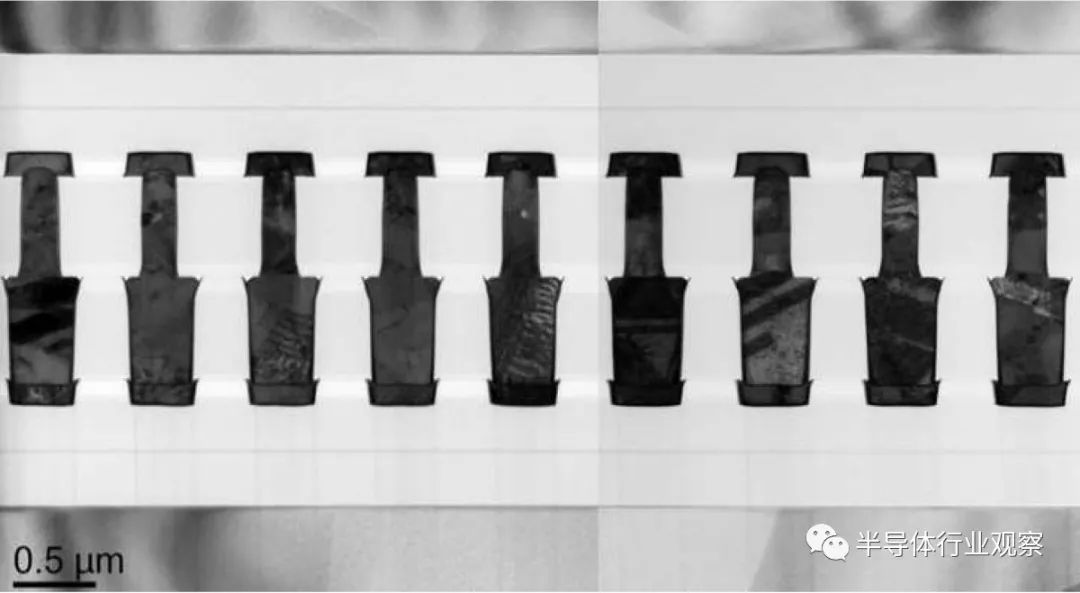

在技术方面,晶圆到晶圆混合键合解决方案的进步将允许非常高的芯片到芯片互连密度,这是对一级和中级高速缓存进行分区所必需的。

图 2:700nm 间距的晶圆到晶圆混合键合(如 2021 IEDM 所示)。

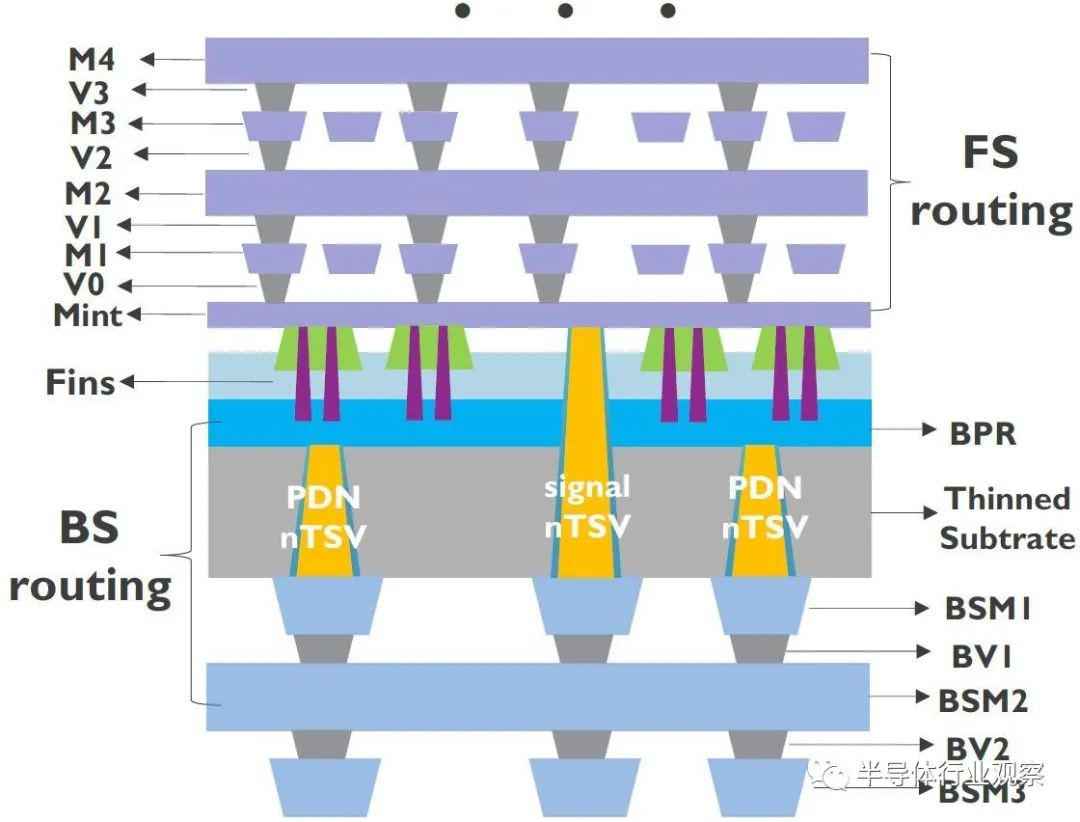

高性能 3D-SOC 系统的一种可能划分涉及将部分或全部存储器宏放置在Die的顶部,而将逻辑放置在Die底部。在技术方面,这可以通过使用低温晶圆对晶圆键合技术将“逻辑晶圆”的有源正面键合到“存储器晶圆”的有源正面来实现。在这种配置中,两个晶圆的原始背面现在都位于3D-SOC 系统的外部。

Eric Beyne说:“我们现在可以考虑利用这些晶片的‘自由’背面进行信号路由或直接为‘逻辑晶圆’中的晶体管供电。传统上,信号路由和电力传输发生在晶圆的正面,它们在复杂的后端互连方案中争夺空间。在这些设计中,硅片的背面仅用作载体。2019 年,Arm 的模拟首次显示了在中央处理单元 (CPU) 设计中使用背面供电网络 (BSPDN) 的有益影响,中央处理单元 (CPU) 实施了由 imec 开发的 3nm 工艺。在此设计中,位于晶圆减薄背面的互连金属使用位于掩埋电源轨上的硅通孔 (TSV) 连接到硅片正面的 3nm 晶体管。

因此,当实现 BSPDN 以提供位于“逻辑存储器”3D-SOC 底部的耗电核心逻辑电路时,可以预期额外的性能提升。还可以考虑替代 3D-SOC 分区,其中部分内存块(例如 L1 级缓存静态随机存取内存 (SRAM))也位于底部裸片中,也由背面供电。

除了扩展 3D-SOC 设计的可能性之外,BSPDN 还被提议用于单片单芯片逻辑和 SRAM 片上系统 (SOC),它们可以帮助进一步的设备和 IC 扩展。imec 项目经理 Geert Van der Plas说:“将供电网络移至硅片背面已被证明是一种有趣的方法,可以解决线路后端 (BEOL) 路由拥塞挑战并减少 IR 压降。与 3D-SOC 方法的主要区别在于,现在将伪晶圆键合到目标晶圆上,以实现背面晶圆减薄和金属化。” imec 的合作伙伴之一最近宣布在其未来的节点芯片之一中实施这样的 BSPDN 概念。

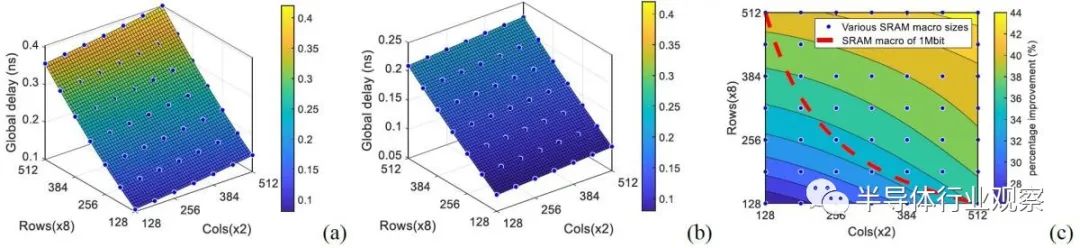

虽然 BSPDN 的好处已经在特定设计中得到证明,但使用晶圆背面进行全局信号路由可以预期获得额外收益。Imec 与 Cadence 合作,首次评估并优化了部分从背面布线的 SRAM 宏和逻辑电路设计。SRAM 宏不仅涉及存储器位单元阵列,还涉及外围电路(如地址解码器、控制块等)——与处理器设计相关。

图 3:用于 PDN 和信号路由的传统正面 (FS) BEOL 和背面 (BS) 金属示意图。用于 PDN 路由的 BS 金属使用 nTSV 将 BS 金属连接到掩埋电源轨,而用于信号路由的 BS 金属使用 nTSV 将 BS 金属连接到 FS 金属(如 2021 IEDM 所示)。

对于 SRAM 宏和逻辑,最多三个背面金属层用于信号路由,而纳米 TSV (nTSV) 将背面金属化连接到正面。SRAM 宏在其设计中实现了 2nm 纳米片晶体管。在这些宏中,只有外围电路的全局布线设计有背面金属化。对于逻辑,使用环形振荡器框架来评估背面信号路由的影响。该设计在逻辑标准单元中实现了 2nm 技术节点的分叉表。使用相同的 2nm forksheet 工艺设计套件 (PDK) 的 64 位 ARMTM CPU 的物理实现用于确保环形振荡器仿真结果的意义。

Geert Van der Plas表示:“与正面布线相比,背面布线在改善长互连信号布线的延迟和功率效率方面明显更有利。对于 SRAM 宏,与前端布线相比,我们展示了高达 44% 的性能提升和高达 30% 的电源效率提升。对于逻辑单元,背面布线使速度提高了 2.5 倍,能效提高了 60%。” R. Chen 等人在 2021 年 IEDM 论文“Design and optimization of SRAM macro and logic using backside interconnects at 2nm node

中描述了结果。

图 4 – SRAM 宏在各个宏行和列的全局布线延迟(读取访问)。(a) FS;(b) BS 和 (c) 从 FS 到 BS 的改进。宏大小范围从 128*128*16=256kbit 到 515*512*16=4Mbit(如 2021 IEDM 所示)。

通过实验和建模相结合,可以评估电路的性能和功率效率。Dragomir Milojevic说:“实验涉及在电容和电阻方面优化 nTSV 工艺——以确保正面和背面金属之间的良好电气连接。这些参数被输入到一个模型中,用于执行模拟。

最后,我们的团队执行了设计技术协同优化 (DTCO) 驱动的路由优化,显示了进一步改进的途径。通过降低背面金属的电容,我们展示了额外 20% 的性能提升。”

结论

通过系统架构重新设计和 3D 集成技术实现的异构 3D-SOC 方法已被证明是一种提高系统性能的有吸引力的方法。通过利用底部晶圆的背面进行功率传输和/或信号路由,可以获得额外的性能提升。Imec 首次展示了在 SRAM 宏和逻辑电路中使用背面互连的有益影响。这些背面互连可为高性能 3D-SOC 以及单片单芯片 SOC 带来性能改进。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2888内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!