来源:内容由半导体行业观察(ID:icbank)

编译自IMEC

,谢谢。

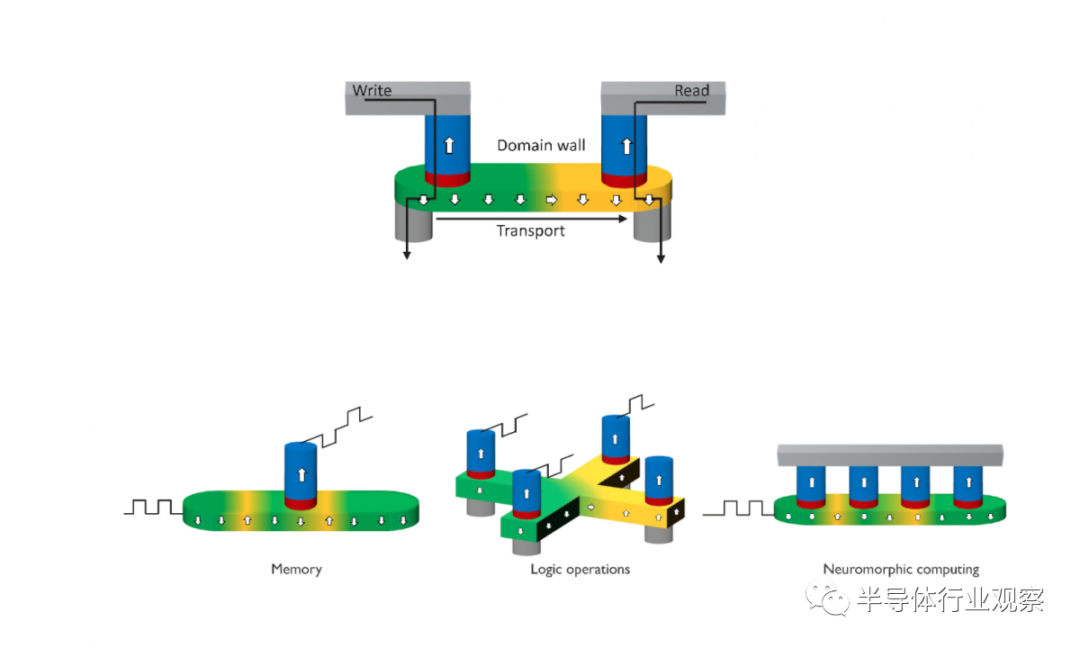

在半导体行业继续将摩尔定律推向下一个十年的同时,世界各地的研究机构和学术界正在探索超越尺寸缩放的方法,以在每个区域封装更多功能。一种有前景的功能缩放方法是domain wall设备:一种在magnetic domains中编码信息的设备。这些具有不同磁化强度(表示为“1”或“0”)的相邻magnetic domains被magnetic domain walls隔开。读写这些domains以及将这些domain walls

从输入传输到输出的能力为构建逻辑和存储设备提供了一个有趣的基础。

逻辑应用的先决条件是能够以非常高的速度在输入和输出之间以及不同逻辑门之间传输信息。这需要磁材料轨道内的domain walls快速运动。在这种情况下,它们可以用作多数门器件甚至更复杂的逻辑电路的构建块。多数门是democratic设备,如果超过 50% 的输入为真,则返回“真”(或“1”)。在他们最简单的实现中,他们使用三个输入和一个输出。

在存储器的背景下,domain wall器件早先被提议作为racetrack 存储器的推动器——一种非易失性存储器概念,其中domain walls通过磁道路由到选定数量的写入和读取元件。这些存储器有可能达到极高的密度,这一指标现在仅由用于磁轨的材料决定。

因此,拥有一个逻辑和内存都可以连接(沿着同一磁道)的平台提供了一种超越传统冯诺依曼架构的方法,在传统的冯诺依曼架构中,数据存储和计算在物理上是分开的。这意味着该技术也有望用于神经形态内存计算。

将magnetic domain wall器件用于逻辑和存储器应用的想法可以追溯到几十年前。自旋电子学专家在理论和实验室中探索了不同的设备概念。然而,他们的工作主要集中在探索不同材料的机制,以实现高效、快速的domain wall运动。同时,在更新纳米级电读写domain wall的方法方面创新较少。它们主要依靠使用外部磁场进行写入,以及使用磁成像技术进行读取。

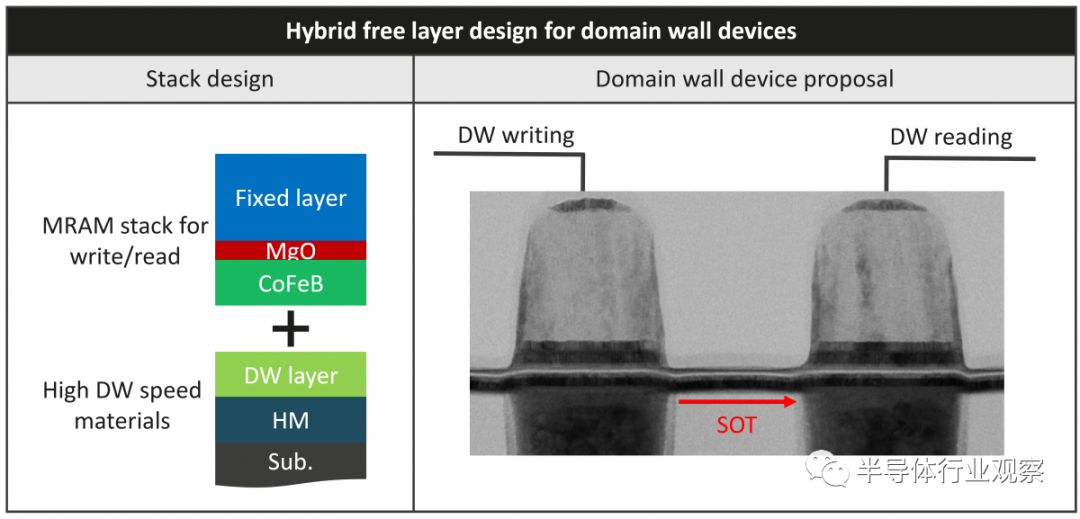

然而,当针对逻辑和存储器的可扩展、兼容 CMOS 的设备时,纳米级域设备的完全电气控制是必不可少的。一种有吸引力的方法是使用磁性隧道结 (MTJ) 进行电读写。在磁性随机存取存储器 (MRAM) 技术开发的背景下,MTJ 已得到深入研究和优化。它们由夹在磁性固定层和磁性自由层之间的薄介电层 (MgO) 组成。MRAM 的自旋转移矩 (STT) 变体使用电流来切换自由层(通常是铁磁 CoFeB)的磁化。读取是通过让电流通过结来测量 MTJ 的隧道磁阻来执行的。

图 1:(顶部)可以存储数据但也可以完全电气传输的domain wall设备的示意图;(底部)设想的应用,从左到右:racetrack存储器、作为超越 CMOS 逻辑器件的自旋扭矩多数门,以及用于神经形态计算的突触权重生成器(如 2021 IEDM 所示)。

尽管具有出色的读写性能,但传统的 STT-MRAM 材料堆栈对实际domain wall器件操作构成了严重限制。在铁磁 CoFeB 中,domain wall速度太低,不适用于逻辑应用。此外,MTJ“支柱”制造工艺中的蚀刻图案化步骤仍然存在挑战。CoFeB 层非常容易受到蚀刻损坏,这会额外阻碍magnetic domain wall在轨道内的传输。

Imec 克服了domain wall设备实际实现的挑战,提供了一套完整的组件来电气读取、写入和传输信息,并构建行业相关设备。关键创新是混合自由层的设计:专门用于domain wall传输的第二个自由层被合并到传统的 MTJ 堆栈中。新设计利用了 MTJ 技术开发(用于高效的读写操作)和传输材料优化(用于快速domain wall运动)。

第一个自由层 (CoFeB) 用于通过 STT 有效地写入域,通过它,domain wall也被注入到第二个自由“传输”层中。该层可以是铁磁体或反铁磁体(例如 Pt/Co/Ru/Co)。自由层之间的额外隔离物可实现两层之间的有效铁磁耦合。然后,domain wall在自旋轨道扭矩 (SOT) 的驱动下沿共享轨道高速行进。通过可靠的隧道磁阻实现输出(读数)检测。

图 2:用于domain wall器件电气控制的混合自由层设计和具有两个用于写入和读取的 MTJ 的 imec domain wall器件的 TEM 图像。MTJ 实现了一个混合自由层,其中一层用于写入和读取,一层用于启用 SOT 的domain wall传输(如 2021 IEDM 所示)。

这种新的全电概念还可以克服与 MTJ 蚀刻图案化步骤相关的关键集成挑战。即使第一层被图案化步骤损坏,domain wall仍然可以在底部传输层内移动,该传输层更能屏蔽蚀刻步骤。此外,这些设备是在 imec 的 300 毫米晶圆设施中制造的,采用 MRAM 技术的标准工艺——极大地促进了该技术的工业采用。

在 2020 IEDM 上,imec 团队首次展示了将这些magnetic domain wall器件用于逻辑应用的概念证明。几个充当逻辑输入的 MTJ 被配置为馈送简单的 AND 和 OR 逻辑门。

E. Raymenants 等人在 2021 年 IEDM 邀请论文“Magnetic domain walls: from physics to devices”中回顾了这些最新进展。E. Raymenants 等人在 Nature Electronics 论文“Nanoscale domain wall devices with magnetic tunnel junction read and write

展望:走向功能齐全的现实世界逻辑、内存和逻辑内存电路

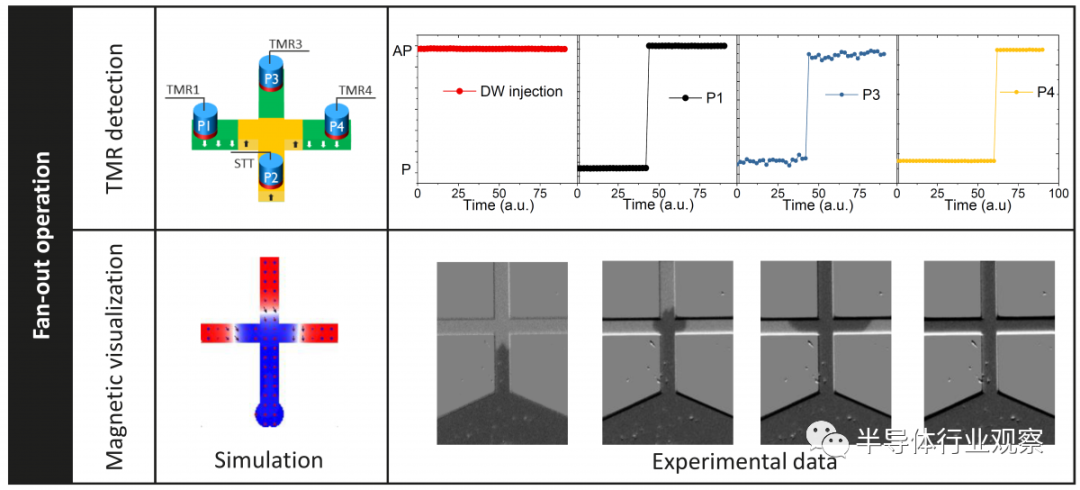

magnetic domain wall器件要进入商业产品还有很长的路要走。2021 年 IEDM 论文描述了该团队朝着构建更复杂的超越 CMOS 逻辑电路的第一步。在本研究中,上述基本构建块在更复杂的逻辑几何结构中实现,以了解有关这些结构内domain wall运动的更多信息。这种几何结构的一个例子是自旋扭矩多数门 (STMG) 的实现,由三个输入 MTJ 和一个输出 MTJ 组成。四个 MTJ 共享一个十字形的domain wall轨道。该团队不仅可以证明轨道内的domain wall运动(与磁成像观察一致),还可以证明这种设计能够实现扇出操作。

图 3:通过十字形纳米器件中的电读出 (TMR)、微磁模拟和微器件中的磁成像技术(如 2021 IEDM 所展示)观察到的扇出操作演示。

其他研究计划为功能齐全的高密度赛道存储器做准备。未来,还需要为基于domain wall的逻辑输入存储器设备开发新的架构和算法。

在 2021 IEDM 上,imec 回顾了其在用于逻辑和内存功能缩放以及神经形态计算的magnetic domain wall设备方面的工作。MTJ 内的新型自由层设计被证明可以克服最先进的磁畴壁设备的实际限制。在更复杂的逻辑电路中实现器件的初步研究看起来很有希望,为超越 CMOS 逻辑应用的节能自旋电子器件铺平了道路。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2891内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!