来源:内容由半导体行业观察(ID:icbank)

编译自anandtech

,谢谢。

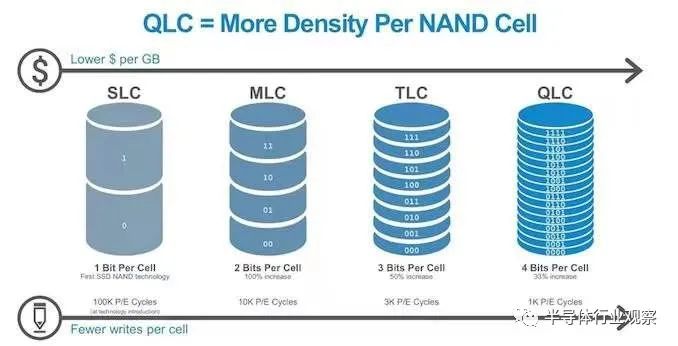

增加下一代存储容量的关键驱动因素之一是增加每个单元可以存储的位数。每个单元一到两个位的轻松跳跃直接增加了 100%,以换取读/写位所需的更多控制,但也限制了单元的耐用性。我们已经看到每个单元最多四位的存储的商业化,并讨论了五个。最近,一家日本公司现在准备开始谈论他们新的每单元 7 位解决方案。

从每单元 1 位变为每单元 2 位可轻松将容量翻倍,而改为每单元 3 位仅增加 50%。随着添加更多位,添加这些位的价值会减少,但控制读取和写入的设备成本呈指数增长。必须在每单元多少位具有经济意义与实现这些位的控制电子成本之间保持中等平衡。

-

每个单元 1 位需要检测 2 个电压电平,基本容量;

-

每单元 2 位需要检测 4 个电压电平,+100% 容量;

-

每单元 3 位需要检测 8 个电压电平,+ 50% 容量;

-

每单元 4 位需要检测 16 个电压电平,+33% 容量;

-

每单元 5 位需要检测 32 个电压电平,+25% 容量;

-

每单元 6 位需要检测 64 个电压电平,+20% 容量;

-

每单元 7 位需要检测 128 个电压电平,+16.7% 容量;

此外,每个单元的位数越多,耐用性越低 - 当您存储许多位时,电压变化只需稍微漂移即可获得错误结果,因此对高容量单元的重复读/写会使电压漂移直到电池无法使用。目前,市场似乎对每单元 3 位 (3bpc) 的性能和每单元 4 位 (4bpc) 的容量感到满意,还有一些 2bpc 设计可实现长期耐用性。一些主要供应商一直致力于 5bpc 存储,尽管低耐用性可能使该技术仅适用于 WORM——一次写入,多次读取,这是相当于老式 CD 或非-可重写 DVD。

来自日本的 C 系列初创公司 Floadia Corp. 早前发布了一份新闻稿,称其已开发出每单元 7 位 (7bpc) 的存储技术。虽然这个产品仍处于原型阶段,但他们认为这个 7bpc 闪存芯片,可能在 WORM 场景中,在 150摄氏度下具有有效的 10 年数据保留时间。该公司表示,具有这种控制级别的标准现代存储单元只能将数据存储约 100 秒,因此设计的秘诀在于他们开发的新型闪存单元。

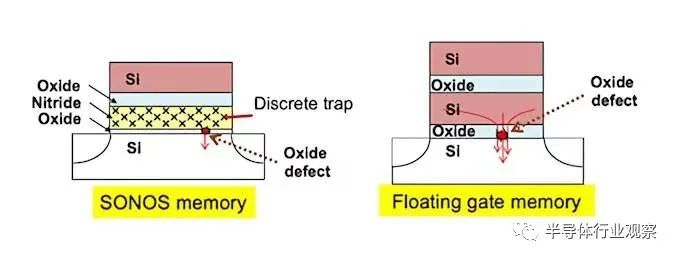

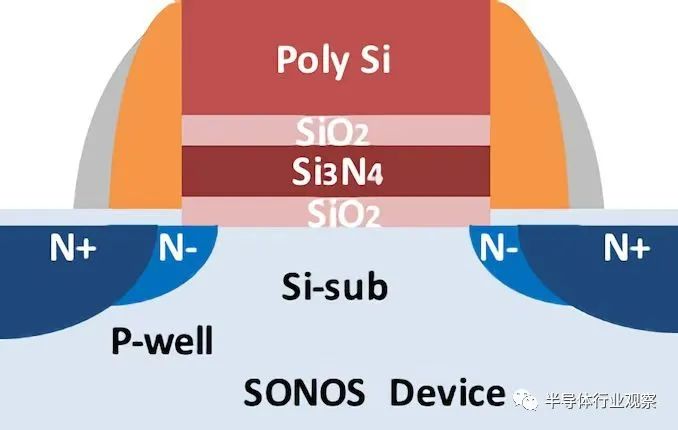

SONOS cell使用分布式电荷陷阱设计,依赖于氧化硅 - 氮化物 - 氧化物 - 硅布局,该公司指出中间有一个有效的氮化硅膜,电荷被捕获以实现高保留。在简单的电压编程和擦除周期中,该公司展示了 100k+ 个周期且电压漂移非常低。氧化物-氮化物-氧化物层依赖于 SiO2 和 Si3N4,后者据称易于制造。这允许在 NV-SRAM 或嵌入式设计(如微控制器)中使用非易失性 SONOS 单元。

这实际上是最后一点,这意味着我们还需要很长时间才能在现代 NAND 闪存中看到这一点。Floadia 目前正与东芝等公司合作,在各种微控制器中实施 SONOS 单元,而不是在 40 纳米工艺节点上部署大型 NAND 闪存,作为具有内存计算特性的嵌入式闪存 IP。这些还没有达到每单元 7 位,因此该公司正在宣传两个单元可以存储多达 8 位的网络权重用于机器学习推理——当我们达到每单元 8 位时,那么它可能更适用。单元数据的 10 年保留是有趣的地方,因为嵌入式平台将在产品的整个生命周期内使用具有固定权重的算法,除了可能罕见的更新。即使寿命延长,

从现代 3bpc 增加到 6bpc NAND 闪存将提供双倍的密度增加,但是需要更大的单元,这将抵消好处。如果> 4bpc 的开发曾经面向消费者,那么还有性能方面的问题,这一点尚未涉及。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2894内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!