[原创] OpenFive发布第八代Die to Die IP,采用Interlaken协议,性能高达1.2Tbps

2021-12-23

14:00:46

来源: 半导体行业观察

现在由于高性能计算、AI/ML以及数据中心,网络和交换等应用的兴起,他们都导致了大量的数据产生,当ASIC和SoC在这些应用中使用时,会有更多的数据流量的进出,这就需要高速的IO接口。在这个需求下,Die to Die将发挥重要作用。可能很多人对Interlaken并不是很熟悉,本文我们将通过OpenFive在这方面的耕耘,来了解下Die to Die IP和Interlaken协议对芯片的贡献。

如今SoC逐渐达到了最大的光罩尺寸,限制了可伸缩性,由于面积、功率、工艺或成本限制而不得不对芯片进行拆分,因此,多个Die、多个芯片、以及多个CPU需要连接在一起,于是,Die-to-Die和芯片到芯片(Chip-to-Chip)等连接需求诞生。分解正成为一个新趋势,Facebook表示,他们不再使用大型设备和集群,而是将网络分解为相同的服务器小单元,并在数据中心的所有小单元之间创建统一的、可扩展的、高性能的连接。

正如1965年戈登摩尔在论文中所说:“由分别封装并相互连接的小功能组成大系统可能更经济。”

在这个趋势下,凭借先进的技术节点、不断增加的芯片尺寸和基于 CPU集群的设计,Interlaken找到了一个独特的位置——即作为低延迟、高吞吐量芯片到芯片连接的首选协议。

Interlaken是Cisco和Cortina于2006年发明的可扩展芯片到芯片互连协议,它是一个通道化的接口,允许多个会话和应用程序同时交互。该免版税协议针对高带宽可靠的数据包传输进行了优化,它建立在SPI-4.2的通道化和每通道流控制特性之上,同时通过使用高速SerDes技术减少了集成电路I/O引脚的数量。再者,其串行链路捆绑在具有多个通道、背压能力和数据完整性保护的组件之间创建逻辑连接,以提高通信设备的性能。

相比以太网和PCIe等重量级的协议来说,Interlaken无疑是一个轻量级的协议。Interlaken在可扩展性、减少引脚数和数据完整性方面提供了许多优势。它的信道化、流量控制和突发交错特性使其适合于各种各样的应用。

而采用第三方Interlaken IP核则可大大降低采用新技术的成本,以系统公司为例,他们可能不熟悉芯片的设计过程或其制造部分,但他们确实希望尽快进入市场,Interlaken IP核就能在芯片和芯片连接的过程中为其提供助力。Interlaken IP核已在网络和交换结构中使用多年,许多应用程序都使用Interlaken IP,包括 NPU、流量管理和交换结构。

目前SiFive公司旗下的一个独立运营的业务部门OpenFive正在积极推动Die to Die IP核的演进发展。OpenFive也是Interlaken联盟的创始成员公司,该联盟的成立是为了确保 Interlaken 协议的不同实现之间的互操作性。自 2007 年以来,OpenFive的 Die 2 Die IP 已部署在多个不同的一级网络和计算客户产品中。这些产品中有许多目前正在多个代工厂的最新技术节点中进行生产。而现在,OpenFive又带来了Die to Die IP的最新进展。

OpenFive发布第八代Die to Die IP

近日,OpenFive发布了第八代芯片到芯片连接的Die to Die IP,该IP核将带宽提高到1.2Tb/s以上,同时减少了面积和功耗。再者,基于灵活、稳固的架构,该 IP核具有“管道效率”和“67位SerDes切片”,具体来看,通过有效地将管道映射到SerDes通道,同时降低所需的时钟频率,减少管道数量(64b内部数据路径),“管道效率”特性节省了大量面积;而“67 bit SerDes切片”的特性则允许IP在单个时钟周期(之前是2个周期)中操作SerDes切片功能,从而降低所需的时钟频率。所以第八代Die to Die IP在节省大量面积的同时,允许IP以较低的频率运行,从而节省了功耗。

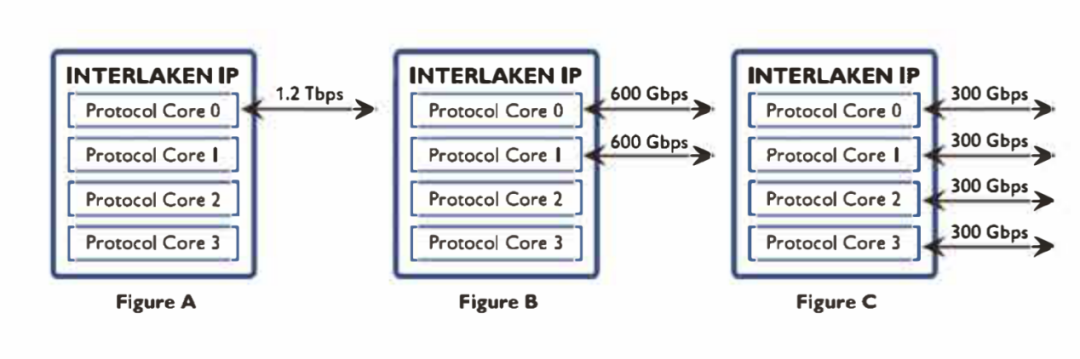

此外,该 IP可支持多个聚合带宽接口,如下图所示,单个IP实例可以在系统内配置,以支持不同的Interlaken协议接口,包括1x1.2Tbps、2x600Gbps或4x300Gbps,从而实现更高效、更灵活的区域实现。

除了上述这些强调的关键特性外,OpenFive 的第八代Die to Die IP还提供了以下特性集作为标准IP功能的一部分:包括支持256个逻辑通道,8位通道扩展至64K通道,启用/禁用独立SerDes通道,支持SerDes速度从3.125 gbps到56gbps,可配置的车道数从1到48,还有灵活的128b和256b用户界面选项:1x128b/2x128b/4x128b/8x128b和1x256b/2x256b/4x256/8x256b,还有从64字节到512字节可编程的BURSTMAX,从32字节到256字节的可编程BURSTMIN,同时带内和带外流量控制,可编程的日历,内置错误检测和中断结构,可测试性的可配置错误注入机制,全包模式和段模式,SerDe支持8,10,16,20,32,40,64,80位,具有控制和配置的维护接口,灵活的统计计数器,还有PRBS生成器/检查器和数据和流控制的循环支持调试功能。

可交付的成果主要有综合 RTL、EDA工具参考脚本和STA Signoff脚本、断言支持用户界面和配置寄存器、健全测试模拟环境,以及包括OpenFiveIP规范、内存、映射登记手册、设计验证计划等的文档。

因为现在诸如高性能计算集群、AI/ML芯片集群、物联网边缘设备、网络和交换结构等前沿技术要求在极低延迟的情况下从一个芯片到另一个芯片进行高透放数据传输,对此,OpenFive在第8代Die to Die IP核的基础上,还引入了跨许多应用程序使用的芯片到芯片和Die-to-Die连接Interlaken IP的低延迟版本。Interlaken-LL包括一个支持256Gbps的验证平台。

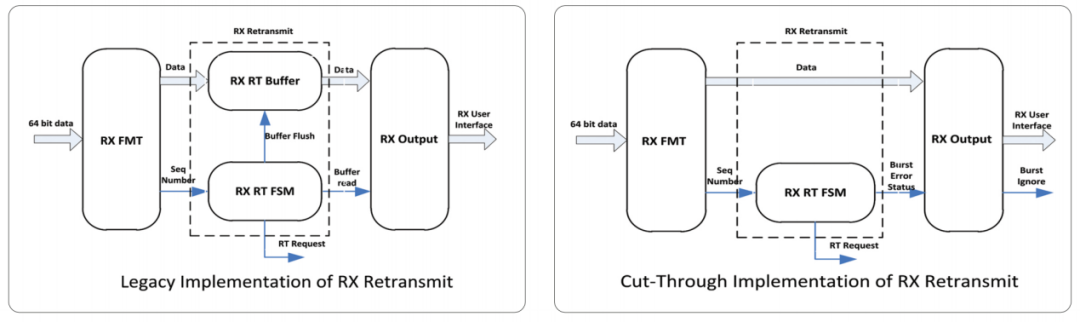

其关键特性具体表现在,有1x64-bit、2x64-bit、4x64-bit的用户界面选项,最多可支持8条车道,支持多达4根内部管道,在直通模式、存储/转发模式这两种模式下可进行重传,降低了整体数据路径延迟,支持NRZ SerDes达32Gbps,具有可配置的Asynchronous-FIFO-Optional,可配置的SerDes宽度高达64位,同时带内和带外流量控制。

除此之外,在其他一些标准特性上,低延迟版本支持256个逻辑通道,8位通道扩展至64K通道,启用/禁用独立SerDes通道,可编程的BURSTMAX从64字节-512字节,可编程突发短从8字节到128字节,可编程的日历,内置错误检测和中断结构,可测试性的可配置错误注入机制,支持内部和外部环回模式和SerDes测试能力使用测试模式。

经过设计和测试,可以很容易地合成到许多ASIC技术中,使用特定于供应商的经过验证的SerDes允许OpenFive客户快速将Die 2 Die IP Core集成到客户所选择的技术中。

Die to Die IP只是OpenFive 众多IP族群中的冰山一角,因为OpenFive在HBM、400/800G以太网、Die-Die、Chip-Chip、USB等其他多个IP领域有着广泛的布局,并且拥有在架构、设计实现、软件、芯片验证与生产环节非常扎实的专业能力。其一流的SoC IP涵盖从嵌入式、人工智能、网络到企业市场的广泛应用。在过去15年中,OpenFive拥有超过350个流片和超过1.5亿颗芯片的出货量。

值得一提的是,除了SoC IP之外,世界正朝着特定领域架构 (DSA) 发展,以解决功率、性能和成本需求。所以对于那些标准产品不能满足业务或技术要求时,OpenFive还提供专门针对功耗

、性能和面积进行优化的定制SoC解决方案,该方案将为客户提供更大的设计灵活性和竞争优势。

“标准化+定制化”两条腿走路,OpenFive也在IP这条道路稳扎稳打。

在工艺节点的先进性方面,OpenFive也是佼佼者,它是少数几家能提供基于台积电最新的5nm工艺的idea-to-silicon方案的公司之一,OpenFive 是TSMC VCA计划的长期成员。2021年4月13日,OpenFive宣布,在台积电5nm工艺技术上成功流片一款高性能SoC,并集成了针对高端HPC/AI、Networking和Storage应用的IP解决方案。目前OpenFive面向HPC/AI、Networking和Storage解决方案的5nm芯片方案已经准备好,可供客户开始设计。

未来OpenFive还通过投资Die to Die接口、小芯片技术和 2.5D 封装的 More-than-Moore 解决方案来保持领先地位。通过混合和匹配不同的技术,帮助设计人员在AI和HPC应用中,将更强的算力SoC在更小的封装尺寸中实现。

综上可以看出,OpenFive在物理设计、晶圆制造以及封装组装方面都有着很大的优势和先进性。OpenFive的Idea-to-Silicon解决方案使用先进的设计技术和封装技术构建在最先进的代工工艺节点上,为芯片的发展提供引擎。

OpenFive是SiFive公司的一个独立运营的业务部门,凭借其Spec-to-Silicon的设计能力和可定制化IP,针对AI/云/HPC/Storage/Networking应用,以及不限定处理器的特定应用领域架构,提供具有极具竞争力的SoCs。

OpenFive的IP组合包括HBM2/2E及用于多Die互连的Die-to-Die (D2D)接口IP, 包括chiplets、以及用于Chip-to-Chip连接的低延迟高吞吐量Interlaken接口IP、400/800G以太网MAC/PCS子系统和USB控制器IP。

OpenFive在架构、设计实现、软件、芯片验证和制造方面提供端到端的专业技术以提供高质量的芯片,最新的工艺节点已经延伸至5nm先进工艺。

今天是《半导体行业观察》为您分享的第2897内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie