芯华章王礼宾:应用牵引,立足创新,构建芯片验证新生态

2021-12-24

17:42:39

来源: 互联网

点击

12月22日,中国IC设计产业年度盛会ICCAD在无锡召开。芯华章科技董事长兼CEO王礼宾,在高峰论坛中发表《应用牵引,立足创新,构建芯片验证新生态》主题演讲,分析了当前芯片设计发展的最新趋势,并为产业同仁带来了解决验证三大痛点的“高效、协同、易用”的全新方案。

芯片设计成本剧增,验证价值凸显

在演讲的开始,王礼宾介绍到,在月初美国举办的DAC上,芯华章带着新发布的验证平台以及四款产品首次亮相。当时当地媒体报道,芯华章出现在今年的DAC上,是DAC的一道亮丽的风景线。在DAC圆桌论坛上,谷歌、苹果、亚马逊等在内的系统公司在谈对EDA的需求时表示,他们需要更强、更快的验证系统,这也是芯片行业现在最大的需求。

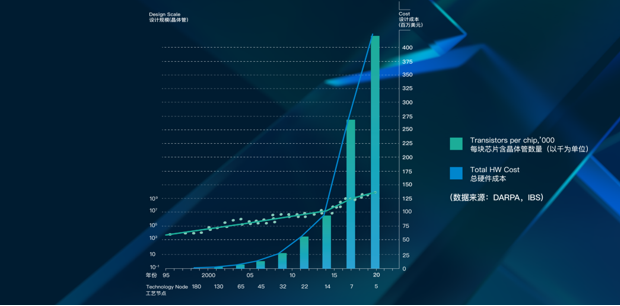

王礼宾指出,从当前芯片发展趋势来看,工艺越来越先进,复杂度越来越高,带来的成本也会大幅增加。从2000年到2020年,半导体工艺从100多nm演进到5nm、3nm甚至2nm,而复杂度在这20年提高了几万倍,成本变化更是成百倍增加。在这种情况下,芯片复杂度高,尤其是成本高起,任何芯片企业都很难承受芯片失败带来的巨大浪费,这就是为什么这些企业都希望有更强大的、更快的验证系统,能够帮他们降低芯片投片风险。

三大痛点:工具兼容性、数据碎片化、缺乏创新

基于目前EDA流程,芯片设计还是避免不了要碰到三大痛点。王礼宾指出,一是工具兼容性,虽然每个单点工具都能解决它相应的问题,但因为算法引擎的不同,导致互相不兼容,很难做到互联互通,这也导致芯片设计在重复造轮子。二是数据碎片化,极大地影响了重复使用可能性,导致验证收敛以及验证调试分析更加困难,有统计数据表明,在整个验证过程中,因为激励的移植、重复编译、碎片化调试,浪费的时间占整个验证周期30%左右。三是工具缺乏创新,传统EDA发展了这么多年,EDA企业有着很沉重的历史技术性包袱,这些包袱导致他们很难使用或者融合目前最先进的技术,比如说人工智能、云原生。

“高效、协同、易用” 王炸组合构建芯片验证新生态

上述这三大痛点显然会对EDA产生更高更严的要求。11月24号,芯华章发布了智能化验证平台,以及4款核心验证工具,受到了业界很广泛的关注。王礼宾对此进行了简要介绍,首先是智V验证平台,它具有统一的调试系统、编译系统、智能分割技术,以及统一场景激励源、统一云原生软件架构,为不同用户提供定制的验证解决方案,可以做到融合多种工具,针对不同的场景提供更合适的解决方案。

王礼宾表示,芯华章拥有4款自主知识产权的验证EDA工具,分别是桦捷-HuaPro-P1(高性能FPGA原型验证系统),穹鼎-GalaxSim-1.0(国内领先的数字仿真器),穹景-GalaxPSS(新一代智能验证系统),穹瀚—GalaxFV(国内率先基于字级建模的可扩展形式化验证工具),也正是这四个工具构成了芯华章的“王炸组合”。

智V验证系统有一个非常重要的特点,那就是具备多工具协同功能,具有全新底层结构。所有工具都是基于智V平台基础上进行自主开发,平台提供统一的技术来支持工具发展,因此智V验证平台能融合不同的工具和不同的技术,实现多工具协同,从而实现验证工具的1+1>2的效果。同时,它还能够使工具的使用变得更加简单,针对各类设计,在不同的场景需求下,可以提供定制化的、全面的验证解决方案,比如把验证工具上云,通过平台以及云原生技术,可以实现云资源调动,以及达到比较高的资源利用,使资源调动更加灵活。

最后,王礼宾强调,芯华章从去年3月份成立到现在拥有300名员工,80%是硕士博士,而且80%是技术人员。目前在全球布局了9个研发中心,申请了59个专利,其中14个专利已经获得了批准,共申请了125个商标。他表示,芯华章将跟全球EDA同仁们一起做出更好更新的产品,为广大IC设计产业保驾护航。

“中国集成电路设计业2021年会暨无锡集成电路产业创新发展高峰论坛(ICCAD 2021)”在无锡太湖国际博览中心隆重举行。本次大会由中国半导体行业协会集成电路设计分会、“核高基”国家科技重大专项总体专家组、中国集成电路设计创新联盟共同主办, 中国半导体行业协会集成电路设计分会、江苏省半导体行业协会、无锡市半导体行业协会、江苏省产业技术研究院智能集成电路设计技术研究所、国家集成电路设计(无锡)产业化基地、上海芯媒会务服务有限公司、上海亚讯商务咨询有限公司共同承办,中国通信学会通信专用集成电路委员会和《中国集成电路》杂志社共同协办。。

责任编辑:sophie